Download User Manual

Transcript

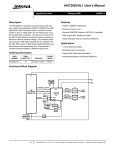

User Manual November 1999 DK86060-3 Version 3.2 16-bit Interpolating DAC Evaluation Board Fujitsu’s DK86060-3 16-bit Interpolating DAC Evaluation Board provides a simple and effective means of evaluating the MB86060 16-bit Interpolating DAC. This enables faster device evaluation without incurring the time and cost penalties of inhouse PCB design and manufacture. FME/MS/SFDAC1/UM_1/4190 EVALUATION BOARD The board provides a complete evaluation environment for the DAC device. A selectable single-ended or transformer-coupled differential analog output interface is provided on-board to simplify integration into target application and development environments. The clock can be sourced from either the internal crystal oscillator, or from a transformer-coupled RF source. 16-bit data is input via a 40way IDC header, or optional SMA/SMB connectors. The MB86060 device is a single 16-bit DAC enclosed in a 80 pin LQFP package with a 0.5mm pin pitch. Features • 16-bit data input via a choice of connectors • Transformer-coupled differential output via BNC & SMA/SMB • Internal oscillator with optional on-board crystal • Transformer-coupled RF clock input via BNC & SMA/SMB • Requires DC power supply of +3.3V Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 1 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board CAUTION ELECTROSTATIC DISCHARGE SENSITIVE DEVICE High electrostatic charges can accumulate in the human body and discharge without detection. Ensure proper ESD procedures are followed when handling this device. Copyright © 1999 Fujitsu Limited Tokyo, Japan, Fujitsu Microelectronics Europe GmbH, and Fujitsu Microelectronics Inc. USA. All Rights Reserved. The information contained in this document has been carefully checked and is believed to be entirely reliable. However, Fujitsu and its subsidiaries assume no responsibility for inaccuracies. Fujitsu Limited and its subsidiaries reserve the right to change products or specifications without notice. No part of this publication may be copied or reproduced in any form or by any means or transferred to any third party without the prior consent of Fujitsu. The information contained in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu. Page 2 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 2 Evaluation Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 2.1 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 2.2 Board And Interface Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 2.2.1 Switches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 2.2.2 Jumper Links . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 3 Getting Started . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 4 Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Appendix A Evaluation Board Circuit Diagrams . . . . . . . . . . . . . . . . . . . . .15 A.1 Components Not Fitted to the PCB . . . . . . . . . . . . . . . . .18 A.2 Changes to the PCB Schematics. . . . . . . . . . . . . . . . . . .19 Appendix B Component Overlays. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20 Appendix C Connector Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Appendix D Prototype Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25 Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 3 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board This page left intentionally blank Page 4 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 1 Overview The DK86060-3 evaluation board allows users to evaluate and demonstrate the different operational modes of the MB86060 16-bit Interpolating DAC. The evaluation board consists of a MB86060 device with support circuitry for single-ended or differential analog output interfaces, a clock input interface, and a clock output interface. This will enable simple connection of measurement equipment. For convenience, customer evaluation boards have been configured using soldered zero-ohm links for transformer-coupled differential output only. The CMOS input data interface has a 40 way IDC header for connection via a flat ribbon cable. Separate SMA/SMB connectors for individual data bit connections are also available, but not normally fitted (SMA not recommended due to insufficient space to rotate the connectors body). The setup of the device is controlled by on-board DIP switches, but these controls can be accessed and overridden via two 25 way male D type connectors if remote control is required. The evaluation board has been designed to address requirements of both automatic and conventional bench testing. Standard evaluation boards feature a simplified build state where certain components or connectors are omitted. These omissions are documented in Appendix A with the evaluation board schematics. This User Manual is intended to document the DK86060-3 Development Kit PCB titled 'MB86060 DAC TEST CARD - ISSUE 3' only. Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 5 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 2 Evaluation Board 2.1 Power Supply The DK86060-3 evaluation board requires a +3.3V supply, and a number of other low voltage DC supplies depending upon build configuration (marked †). A cable mounting socket suitable for mating with the PCB mounted power plug is supplied with the development board. Additional sockets, type Weidmuller BL3.6/ 16 may be obtained from RS Components (http://rswww.com), Stock no. 216-2683. The power should be connected to the board via this connector, as shown in Figure 2.1. Flexible cable of 16 - 28 AWG, 0.5 1.5mm 2 should be used. The format of the power connector is common across Fujitsu’s DAC Development Kit range. The result is that there are some un-necessary supplies (marked ‡). These supply pins are connected to test points for convenience if the user requires extra supplies for the prototype area Cable Mounting Socket PCB mounted power header Standard Requirement -5.2V † Data -2V Sense ‡ Data -2V Force ‡ Data GND Data +3.3V Force Data +3.3V Sense Opt. +3.3V Sense † Opt. +3.3V Force † +3.3V Sense +3.3V Force GND -2V Force † -2V Sense † +5V † +12V † Relay † Pin 16 Figure 2.1: Power Connections Page 6 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 2.2 Board And Interface Controls SW1 SW3 PL1 PL3 SW4 SW2 SW5 PL2 Clock Out Clock In Power Differential Out Figure 2.2: Evaluation Board Component Side Layout Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 7 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 2.2.1 Switches There are several control switches on the evaluation board, as shown in Figure 2.2. Switch idents are marked on the board silkscreen. Table 1: Switch 1 Settings Switch Mode / Function Setting SW1[1:3] (DITH0, DITH1, DITH2) Dither disabled VSS, VSS, VSS -27.0 dBFS pk Dither amplitude VDD, VSS, VSS -21.0 dBFS pk Dither amplitude VSS, VDD, VSS -15.0 dBFS pk Dither amplitude VDD, VDD, VSS -9.0 dBFS pk Dither amplitude VSS, VSS, VDD -3.0 dBFs pk Dither amplitude VDD, VSS, VDD Factory use only VSS, VDD, VDD Factory use only VDD, VDD, VDD Disabled VSS, VSS x2 Slow VDD, VSS x2 Fast VSS, VDD x4 VDD, VDD Segment Shuffling disabled VSS, VSS Random - every 4 cycles VDD, VSS Random - every 8 cycles VSS, VDD Random - every 16 cycles VDD, VDD Factory use only VSS SW1[4:5] (FILTS, FILTF) SW1[6:7] (SHUF0, SHUF1) SW1[8] (TEST) Page 8 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Table 2: Switch 2 Settings Switch Mode / Function Setting SW2[1:2] (OSC0, OSC1) Multiplier fastest mode VSS, VSS VDD, VSS VSS, VDD Multiplier slowest mode VDD, VDD Table 3: Switch 3 Settings Switch Mode / Function Setting SW3[1] (TWOC) Offset binary input data VSS 2’s Compliment input data VDD Clock multiplier bypass VSS, VSS, VSS Clock multiplier x1 mode VDD, VSS, VSS Clock multiplier x2 mode VSS, VDD, VSS Clock multiplier x3 mode VDD, VDD, VSS Clock multiplier x4 mode VSS, VSS, VDD Clock multiplier x5 mode VDD, VSS, VDD Clock multiplier x6 mode VSS, VDD, VDD Clock multiplier x8 mode VDD, VDD, VDD SW3[5] (NSHAPE) Noise shaping disabled VSS Noise shaping enabled VDD SW3[6]† (CKSEL) On-board crystal VSS External clock source VDD SW3[2:4] (MUL0, MUL1, MUL2) † Standard Evaluation Kits are not configured with an on-board crystal. Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 9 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Table 4: Switch 4 Settings † ‡ Switch Mode / Function Setting SW3[1] & SW4 Part Reset† SW3[1] VSS Push to Reset Full Reset‡ SW3[1] VDD Push to Reset With SW3[1] set to Offset binary, a 'Reset' will not reset the Clock Multiplier or the Reference circuits. With SW3[1] set to 2’s compliment, a 'Reset' will reset the entire device. Table 5: Switch 5 Settings Switch Mode / Function Setting SW5 Device in forced RESET mode B Device in normal operating mode A Note: SW1, 2 & 3 may appear to malfunction if pressure is placed on the slider when in either the left or right position. In this case the DAC control pin will be floating. Page 10 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 2.2.2 Jumper Links Table 6: Jumper Links Link Name Mode / Function Setting LK1A† (VDD) Optional supply used for VDD 1 to 2 linked Common supply used for VDD 2 to 3 linked Optional supply used for CVDD 1 to 2 linked Common supply used for CVDD 2 to 3 linked Optional supply used for RVDD 1 to 2 linked Common supply used for RVDD 2 to 3 linked Optional supply used for AVDD 1 to 2 linked Common supply used for AVDD 2 to 3 linked LK2‡ (SEOUT) Select single-ended output Linked Select differential output Not linked LK3 (CMRR) Centre tap of T1 (Pin 5) linked to AVSS Linked Centre tap of T1 (Pin 5) decoupled to AVSS Not linked DIFF OUT Ground linked to AVSS Linked DIFF OUT Ground floating Not Linked CLK OUT Ground linked to VSS Linked CLK OUT Ground floating Not Linked CLK IN Ground linked to CVSS Linked CLK IN Ground floating Not Linked LK7† (PSRR) Power supply ripple rejection disabled Linked Power supply ripple rejection enabled Not Linked LK8 CLK OUT biasing enabled Linked CLK OUT biasing disabled Not Linked LK1B† (CVDD) LK1C† (RVDD) LK1D† (AVDD) LK4 LK5 LK6 Note: Bold type indicates default jumper settings. † Standard Evaluation Kits are not configured to use the optional supply. LK1 and LK7 are not used. ‡ Standard Evaluation Kits are configured for Differential output. LK2 is not used. Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 11 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board This page left intentionally blank Page 12 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 3 Getting Started This Chapter documents the basic steps to powering up and starting to use the DK86060-3 Evaluation Board. Component references may be cross-referenced with the component overlay in Appendix B. Step 1. Configure the board The data input format must be configured to either Offset binary or 2’s Compliment. Use configuration switch SW3[1] to select. The device control signals should be set to the default conditions shown in Section 2.2. Use configuration switches SW1, SW2 and SW3 to select. Jumper links LK3 to LK6 inclusive, and LK8, should be 'Not linked'. Switch SW5 should be set to position 'A'. Step 2. Connect data input & analog output connectors to the board The input data should be connected via the 40 way IDC header PL2, or if fitted the SMA/SMB connectors J19 to J34 inclusive. See Table C1: for the pin description of the IDC header. The output is provided as a transformer-coupled differential signal, via a BNC connector. • Differential Output signal (J7). (50Ω source resistance) The DAC is coupled to a single output connector using a transmission line and 1:1 balun transformer. Signal swing is ±0.5V with a high impedance load, or ±0.25V with an external 50Ω load. For sinusoidal signals, this corresponds to approximately -2dBm into a 50Ω external load. Step 3. Connect clock The clock input is provided to the device through a transmission line transformer, via a BNC connector. • RF clock (J17). (50Ω input impedance) The DAC is coupled to a single input connector using a transmission line transformer. Sine wave or square wave input signals between -10dBm and +10dBm are acceptable, depending on clock frequency and required output jitter / phase noise. Step 4. Connect power header to power supplies Ensure that the power supply is connected according to Figure 2.1. Connect the power header to the board and turn the power supply on. Step 5. Press Reset Press the Reset button to ensure that the device is in the correct operating condition. Press Reset every time a configuration change is made. Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 13 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 4 Testing This section provides a brief introduction to testing with the DK86060-3 16-bit Interpolating DAC Evaluation Board. MB86060 incorporates a 12-bit, 400MSa/s digital to analog converter core with a 16-bit interpolation filtering front end, designed to give excellent SFDR performance. The use of novel techniques for the converter architecture have allowed high speed operation consistent with BiCMOS or bipolar devices, but with the low power consistent with CMOS. In certain applications it is now possible to consider using the MB86060’s DAC core at a full 400MSa/s DAC conversion rate, even though the generated signal band may only be, for example, up to 40MHz or less. Although, in theory, a 100MSa/s converter would be sufficient to reproduce this desired signal band, according to Nyquist, converter performance will tend to limit due to step-size and sinx/x roll-off as a result of the converters sample & hold output stage. 400MSa/s operation significantly reduces effects due to both of these - sinx/x roll-off is reduced from -4dB to -0.22dB, and the increased oversampling [DAC conversion rate / signal rate] reduces step sizes to give a direct improvement in spurious performance. These issues should be considered when testing the MB86060 and measurements should be obtained at different conversion rates to establish the most appropriate operating conditions for the target application. For convenience the board has been configured using soldered zero-ohm links as a transformer coupled differential output. To enable single-ended outputs changes to the soldered zero-ohm links would be required. For rise/fall time tests the transformer-coupled output should not be used since the transformer response will limit the dV/dt. The DAC current switches are designed to give the best possible differential performance, at the expense of some single ended performance, so there is a noticeable difference between the two configurations. The revised analog output circuit uses an additional transmission line transformer to improve rejection of common-mode distortion at the DAC output. If a spectrum analyser is used to measure the output spectrum, it should have a very good noise and distortion, for example HP8562E or R&S FSEA30. In addition, the input attenuator setting should be chosen such that input mixer distortion does not limit the measurements (e.g. 30dB RF attenuation). This implies that narrow resolution bandwidths and/or averaging are required to obtain low enough measurement noise floor. Page 14 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Appendix A Evaluation Board Circuit Diagrams Appendix A shows the circuit diagrams of the DK86060-3 evaluation board. Note that these diagrams are for reference only and that some components fitted to the board may be of a different value to the schematics or not fitted at all. Fujitsu has undertaken to document these changes where possible. The schematic is divided over two pages for clarity. • Sheet 1 - DAC support circuitry, including analog output interfaces [covers 2 pages] Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 15 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board 1 TP1 ST1 2 C1 1 150u 4 3 ST4 2 6 ST6 5 2 4 P5 J6 AVSS R102 51R 1 T1 A1 6 C14 1 P10 R14 0R R15 0R R104 AVDD 51R LK3 2 AVSS +12V C13 C27 AVSS 1 R16 0R R17 0R 2 SGND 100n 100n R106 R105 C11 100n AVDD LK2 51R 51R CVSS J35 C20 CVSS 22p R57 1M 1 6 0R 0R R97 R99 0R 0R CVSS T3 R61 51R VSS J16 R108 10K R52 10K CVSS 100n T2 3 1 2 VDD 1 VR1 100R R E S E T B C K S E L N S H A P E C S U B L O C K 2 6 R58 75R 4 R59 75R D V V N T V V D D D S D S / WD S I I I U D S C O D S T T T B / C H H H S 2 1 0 O U T C K D O S V V U U D S T B D S B C K M O V V U U D S L T D S 2 M U L 1 C17 100n 100n R50 0R R51 0R 1 SW5 1PCO SW4 2 3 R53 200R R56 R54 200R R55 200R 10K SPDT VSS 1 1 1 1 1 1 2 2 2 1 2 1 2 1 2 1 1 4 2 5 3 6 4 7 5 8 6 9 7 0 8 1 9 2 0 3 1 4 2 5 3 ADT4-1WT C22 3 CLKOUT_GND APP.GND Page 16 of 28 100n LK5 1 2 TP5 VSS M U L 0 VDD 5 LK8 1 J13 C C C V C V V S L S D S K S D O V E R VSS 1 2 VSS J12 BNC C L K B A S U B C18 3 10K ADTL1-12 CLKIN_GND APP.GND F I L T S 100n J14 R107 100n C24 F I L T F R94 10K C28 J18 S H U F 0 CVDD C29 100n 4 S H U F 1 C19 X2 R62 10K CVSS R V S S / T E S T 2 2 2 2 2 2 2 2 2 3 3 3 3 3 3 3 3 3 3 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 R98 J36 100n R60 51R B G A P RVSS RVDD OSC0 OSC1 AVDD AVSS IOUTB IOUTB AVSS AVDD AVDD AVSS IOUT IOUT AVSS AVDD XIN XOUT CVDD CVSS CVDD J15 V R E F CVSS 1 2 R R E F X1 X1 22p C23 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 C12 100n R96 C21 CVSS 1K CVDD 50R CVSS CVSS 3 C9 100n AVDD RCON CVSS J17 BNC 200R 200R AVSS C10 100n J11 1 AVSS C8 100n AVSS R11 R12 AVDD R103 AVSS 10K C7 100n OSC0 OSC1 R109 4 8 A2 R9 RVSS AVSS RF103-12 AVSS 0R RVSS AVSS C32 RL1 AVSS R18 0R A4 RVDD P11 50R 7 2 R8 R10 P12 6 AVSS 100n C30 A4 J9 BNC C6 RVSS 8 7 7 7 7 7 7 7 7 7 7 6 6 6 6 6 6 6 6 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 AVSS 1 1 J3 RVSS P3 P4 2 5 R100 6 R7 51R 2 3 4 VSS AVSS CVSS A3 A2 5 3 TC04BCZM D1 3 4 5 5 3 R101 R13 100R R19 J8 1K J4 +5V AVSS R6 RVDD 100n P1 P2 -5.2V P9 A3 0R -2V -2V P8 AVSS A1 AVSS P7 R R R 2 AVDD P6 0R RVDD ST8 4 3 R4 RVSS 4 2 0R R5 100n 2 5 4 3 6 ST9 1 0R R3 C31 1 TP4 J7 BNC LK7 2 R R R R R CVDD C4 6 C5 150u 0R AVDD 3 J2 1 150u +5V R2 2 C3 1 2 RVDD 3 AVDD 5 4 3 3 ST7 2 CVDD VDD 0R ST5 0R R38 3 1 TP3 LK6 2 3 150u 1 LK1D 1 4 DVDD R1 LK1C 1 VDD 5 C2 +12V J10 1 3 2 SGND LK4 LK1B 1 2 ST3 RCON ANALOGUE APP.GND LK1A 1 DVSS 3 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 J5 BNC TP2 1 ST2 J1 -5.2V D-2VS D-2VF DGND D+3.3VF D+3.3VS OPTS OPTF +3.3VS +3.3VF SGND -2VF -2VS +5V +12V RELAY R39 3 2 -5.2V TP6 TP7 TP8 PL3 DB25 Copyright © 1999 Fujitsu Microelectronics Europe GmbH R November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board PL1 R39 LK1C VSS LK1D 0R R38 1 2 VSS R20 10K RVDD OSC0 R21 2 AVDD 1 2 4 5 10K OSC1 0R 3 R30 R31 R32 R33 R34 3 OSC1 VDD 6 SW2 2PCO OSC0 (TEST) 200R 200R 200R 200R 200R SHUF1 SHUF0 FILTF R35 R36 R37 D D R6 200R 200R 200R 1K FILTS OVER VSS R22 10K VDD 1 2 4 5 7 8 10 11 13 14 16 17 19 20 22 23 RVDD R23 C15 100n TC04BCZM R24 RVSS 10K VSS D1 R7 51R C6 R8 100n R9 0R VSS 10K R10 R25 10K R26 10K R27 10K VDD C16 100n R40 200R R28 10K R29 10K V R E F B G A P RVSS RVDD OSC0 OSC1 AVDD AVSS IOUTB IOUTB AVSS AVDD AVDD AVSS IOUT IOUT AVSS AVDD XIN XOUT CVDD CVSS C L K B R V S S / T E S T S H U F 1 C C C V C V V S L S D S K S D S H U F 0 R E S E T B F I L T F C K S E L F I L T S N S H A P E A S U B C S U B O V E R L O C K D V V N T V V D D D S D S / WD S I I I U D S C O D S T T T B / C H H H S 2 1 0 O U T C K D O S V V U U D S T B D S B C M K O V V U U D S L T D S 2 M U L 1 100n D0 D1 DVSS D2 D3 D4 D5 DVDD D6 D7 D8 D9 DVSS D10 D11 D12 D13 DVDD D14 D15 R63 R64 R65 R66 R67 R68 R69 R70 R71 R72 R73 R74 R75 R76 R77 R78 CVSS C19 X2 CVDD 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 2 R79 R80 R81 R82 R83 R84 R85 R86 R87 R88 R89 R90 R91 R92 R93 R95 U1 MB86060 200R 200R 200R VSS C17 VDD VSS R55 200R R48 10K R49 10K J20 J21 PL2 IDC40 J22 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 X2 X1 J25 J24 J23 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R J27 J28 J29 J30 J34 J33 J32 J31 TWOC R47 10K R54 200R J19 DVDD R46 10K R45 10K 10K PDT VDD DVSS 100n VDD R53 200R R56 24 SW1 8PCO J26 100n SW4 VSS 21 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R 160R DVSS 100n 100n C18 0R DB25 18 C26 M U L 0 R41 R42 R43 CVSS R51 DITH0 DVSS C25 2 2 2 2 2 2 2 2 2 3 3 3 3 3 3 3 3 3 3 4 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 X1 0R DITH1 12 DVSS R R E F R50 DITH2 9 1K DVDD 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 (SOUT) 6 15 TWOC 8 7 7 7 7 7 7 7 7 7 7 6 6 6 6 6 6 6 6 6 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 200R 200R 10K 3 13 25 12 24 11 23 10 22 9 21 8 20 7 19 6 18 5 17 4 16 3 15 2 14 1 DVSS R44 10K VSS FUJITSU MICROELECTRONICS EUROPE 1 1 1 1 1 1 7 6 4 3 1 0 8 7 5 4 2 1 NETWORK HOUSE NORREYS DRIVE MAIDENHEAD BERKSHIRE, SL6 4FT VSS 1 1 1 1 1 1 2 2 2 1 2 1 2 1 2 1 1 4 2 5 3 6 4 7 5 8 6 9 7 0 8 1 9 2 0 3 1 4 2 5 3 SW3 6PCO P8 PL3 DB25 Title MB86060 DAC TEST CARD 1 8 VDD Copyright © 1999 Fujitsu Microelectronics Europe GmbH 1 5 1 2 Size 9 6 3 Document Number B Date: REV CAD DATA C9905 September 14, 1999 3 Sheet 1 of 1 Page 17 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board A.1 Components Not Fitted to the PCB Table A1: Components Not Fitted Reference Value LK1a, b, c, d - Power supply selection jumper links LK2 - Single-ended output selection jumper link LK7 - PSRR jumper link J2 to J6, J8, J10, J11, J13 to J16, J18 to J36 - SMA/SMB connectors J5, J9 - BNC connectors D1 TC04BCZM Reference diode RL1 RF103-12 X1 - C2 150uF C14, C32 - C20, C21 22pF R1 0R Optional power supply PSRR series resistor R6 1K Reference current limit resistor R7 51R Reference series resistor R14, R16 0R Single-ended output relay bypass resistors R18 0R CMRR jumper link bypass resistor R19, R109 - R57 1M Crystal shunt resistor R63, R65, R67, R69, R71, R73, R75, R77, R79, R81, R83, R85, R87, R89, R91, R93 0R Data input series resistors (for SMA/SMB connectors) R102, R104 51R Analog output termination resistors T4 - Page 18 of 28 Description Output selection relay Crystal Optional power supply decoupling capacitor Analog output RC network capacitors Crystal capacitors Analog output RC network resistors Optional analog output circuit transformer Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board A.2 Changes to the PCB Schematics Table A2: Schematic Changes Reference R100 C30 T1(a) T1(b) Old Value New Value - 51R 22pF ADTT1-1 ADTL1-12 Description Analog output RC network resistor Analog output RC network capacitor Mini-Circuits 1:1 analog output transformer Mini-Circuits transmission line transformer 1 6 To DAC To Output T1b 3 4 T1a 5 Figure A1 Replacement Schematic For T1 (Pin Numbers Refer To T1) Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 19 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Appendix B Component Overlays Figure B1 Component Overlay For Layer 1, (Component Side) Page 20 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Figure B2 Component Overlay For Layer 4 (Solder Side) Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 21 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Appendix C Connector Pin Functions Table C1: Data Connector PL2 Pin Functions 1 39 Page 22 of 28 2 40 Pin Function 1 Data Bit 15 (MSB) 3 Data Bit 14 5 Data Bit 13 7 Data Bit 12 9 Data Bit 11 11 Data Bit 10 13 Data Bit 9 15 Data Bit 8 17 Data Bit 7 19 Data Bit 6 21 Data Bit 5 23 Data Bit 4 25 Data Bit 3 27 Data Bit 2 29 Data Bit 1 31 Data Bit 0 (LSB) 33 XIN 35 XOUT 37 Not Used 39 Not Used 2 to 40 (Even numbers only) Data Ground (DVSS) Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Table C2: Control Connector PL1 Pin Functions † Pin Function 1 to 13 Digital Ground (VSS) 14 DITH0 15 DITH1 16 DITH2 17† SOUT (O/P) 18 OVER (O/P) 19 FILTS 20 FILTF 21 SHUF0 22 SHUF1 23† TEST 24 OSC0 25 OSC1 These pins are for factory test purposes only. Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 23 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Table C3: Control Connector PL3 Pin Functions Pin Function 1 to 13 Digital Ground (VSS) 14† Test Point 8 15† Test Point 7 16† Test Point 6 17† Test Point 5 18 RESETB 19 CKSEL 20 NSHAPE 21 LOCK (O/P) 22 MUL2 23 MUL1 24 MUL0 25 TWOC † These pins are connected to test points so that connections to the prototype area can be made via the control connector. Page 24 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Appendix D Prototype Area A prototype area has been introduced into the DK86060-3 development kit PCB. This area takes the form of a matrix of pads with plated through holes on a 2.54mm pitch. The pads are made square to allow for 0805 format surface mount devices to be fitted between adjacent pads. The matrix area has four rows individually linked together to act as power rails. These rows are arranged as two pairs, with connections to the internal planes (layers 2 and 3) made to each of the rows. The internal plane regions only occupy the prototype area, and are not linked to any other area of the PCB. The prototype area layout is shown in Figure D1. Layer 2 would typically be used as the ground plane, and layer 3 as the power plane, with signals routed on layer 1. However the choice in the prototype area is free as the planes are entirely separate to the rest of the PCB. Layer 2 Layer 3 Layer 2 Layer 3 Figure D1 Prototype Area Layout Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 25 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board This page left intentionally blank Page 26 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Notes: Copyright © 1999 Fujitsu Microelectronics Europe GmbH Page 27 of 28 November 1999 Version 3.2 FME/MS/SFDAC1/UM_1/4190 DK86060-3 16-bit Interpolating DAC Evaluation Board Worldwide Headquarters Japan Fujitsu Limited Asia Fujitsu Microelectronics Asia Pte Limited Tel: +81 44 754 3753 Fax: +81 44 754 3329 1015 Kamikodanaka 4-1-1 Nakahara-ku Kawasaki-shi Kanagawa-ken 211-88 Japan Tel: Fax: 151 Lorong Chuan #05-08 New Tech Park Singapore 556741 http://www.fujitsu.co.jp/ +65 281 0770 +65 281 0220 http://www.fmap.com.sg/ USA Fujitsu Microelectronics Inc Europe Fujitsu Microlectronics Europe GmbH Tel: +1 408 922 9000 Fax: +1 408 922 9179 3545 North First Street San Jose CA 95134-1804 USA Tel: +49 6103 6900 Fax: +49 6103 690122 Am Siebenstein 6-10 D-63303 Dreieich-Buchschlag Germany Tel: +1 800 866 8608 Fax: +1 408 922 9179 Customer Response Center Mon-Fri: 7am-5pm (PST) http://www.fujitsu-fme.com/ http://www.fujitsumicro.com/ The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams. FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.). CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval. Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan. FME/MS/SFDAC1/UM_1/4190 - 3.2 Page 28 of 28 Copyright © 1999 Fujitsu Microelectronics Europe GmbH