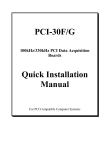

Download PC104-30F/G User`s Manual

Transcript