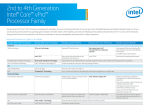

Download CompuLab IPC2 Specifications

Transcript