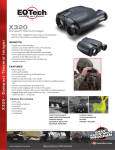

Download SVGA+ Rev3 XL SERIES 852 X 600 ACTIVE MATRIX

Transcript