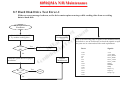

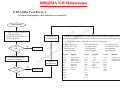

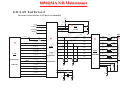

Download MiTAC 8050QMA Service manual

Transcript