Download hvr-dx710_sm3.25 MB

Transcript

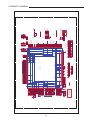

FILE NO. SERVICE MANUAL HDD/DVD Recorder HVR-DX700 (Product Code: 1 682 342 65) (Australia, New Zealand) HVR-DX710 (Product Code: 1 682 342 66) (Australia, New Zealand) SPECIFICATIONS Power Source: 200-240V 50/60Hz Power Consumption: 57W Dimensions: 435(W) x 60(H) x 343(D)mm Net Weight: Approx. 5.6kg Specifications subject to change without notice. REFERENCE No. SM0905006 CONTENTS SPECIFICATIONS ...............................................................................................................2 SCHEMATIC DIAGRAM..................................................................................................................7 PCB CIRCUIT BOARD..................................................................................................................24 INSTRUMENT DISASSEMBLY .....................................................................................................31 PACKING VIEW.............................................................................................................................32 1 SAAA P E C IF IC AT IONS SECTION MODEL -Local Model -Description -Target Area -Mass Production GENERAL -Power Plug -Set Size (WxHxD) - wihtout leg - with leg -Safety Regulation -Set Weight (Net/Gross) -Power Print on Rear Panel -Operation temperature -Power Consumption - Maximum - Operate - Stand-By(power off) -Power Failure Compensation -Stuffing Quantity - 20 ft - 40 ft - 40 ft (HQ) DVD MODULE Spec. -Manufactruer of FEM (Front End Module) -Interface -Opitical P/U -FE Chip -BE chip type Numbers HDD Spec. -Drive interface -Capacity -RPM -Start time -Stop time PLAYABLE DISC TYPE -DVD Type : DVD-ROM / DVD+R / DVD+RW / DVD-R / DVD-RW / DVD-RAM -CD Type : CD-ROM / CD-R / CD-RW -Video Format : DVD / VCD / SVCD / MPEG 4 / JPEG / Kodak picture CD / DviX -Audio Format : DVD-Audio / SACD / HDCD / CDDA / MP3 / WMA / MP3 Pro -Disc size -Regional Code PLAYBACK FEATURES -Disc access time ( play ready time from drawer close press) -Fast Scan Motion (FWD / REV) ; DVD (ROM/-VIDEO/VR) -Fast Scan Motion (FWD / REV) ; HDD (With Time Shifting) -Fast Scan Motion (FWD / REV) ; VCD -Fast Scan Motion (FWD / REV) ; CDDA,MP3 -Fast Scan Motion (FWD / REV) ; DivX -Slow Motion (FWD / REV) ; DVD (ROM/-VIDEO/-VR) -Slow Motion (FWD / REV) ; HDD -Slow Motion (FWD / REV) ; VCD -Slow Motion (FWD / REV) ; CDDA,MP3 -Slow Motion (FWD / REV) ; DivX -Next, Previous -Resume play -Frame-by-Frame Playback (FWD / REV) -Search Title / Chapter / Track / Time -Zoom (In Playback or Pause state) 1st Model REMARK DG-M13E1D-HR/O , DG-M23E1D-HR/O DVD Recorder + HDD For Australia '06.07 2-Pin type ( For Australia) 435 x 55 x 343 mm 435 x 60 x 343 mm CE 4.3Kg / 5.6Kg 200~240V, 50/60Hz 35 57 W 40 W 4.5 W 1 Min. 824 EA 1724 EA 1954 EA Lite On / Daewoo ATA (IDE bus) Interface SANYO & SONY MT1818, MT1816 DMN-8652 ATA (IDE bus) Interface 80GB/ 160 GB (1platter) 7200 RPM 8 sec ( 15 sec max ) 12 sec ( 20 sec max ) Yes to All (Except DVD-RAM) 250G Available - DVD+R/-R After finalize - DVD-R/-RW (Video Format) Yes to All Yes to All (Except MPEG4, Kodak Picture CD) CDDA / MP3 - WMA is Hidden 8cm/12cm 4 Less than 20 sec. (O/O) : x2, x4, x8, x16, x32 (O/O) : x2, x4, x8, x16, x32(except REV x2) (O/O) : x2, x4, x8, x16, x32 (O/O) : x2 (O/O) : x2, x4, x8 (O/O) : x1/2, x1/4, x 1/8 (O/O) : x1/2, x1/4, x 1/8 (O/X) : x1/2, x1/4, x 1/8 (X/X) (X/X) O O (DVD Only) (O/X) : DVD, HDD, VCD DVD : Title & Chapter HDD : Title & Chapter VCD : Track CDDA/MP3 : X O (x2, x4) 2 DVD-R/RW After finalized, DVD Video format HDD OK S P E C IF IC AT IONS -Subtitle SECTION 1st Model O (DVD-ROM Only) -Multi-angle playback O (DVD-ROM Only) -Random Playback -Program Playback X X DVD : Chapter Title Disc Shuffle Scan Off HDD : Chapter Title Disc Off VCD : Track Disc Off CDDA/MP3 : Track All Off DVD,HDD,VCD X X X X O -Repeat -Repeat A-B -Yes DVD -Clear Play -Auto Play -x2 Audio -Combination Playback : JPG + MP3 Only SYSTEM -Language 15 languages E/G/F/S/I/D/Nr/Sw/Pr/H/R/Po/Da/Fi/Cz -On-screen display on/off-user selectable -Disk Type displayed OSD / Front Panel Display -Company LOGO -Screen Saver -PBC for VCD 2.0 or SVCD -Parental lock -Child Lock -TV Aspect Ratio (16x9, Pan Scan, letterbox) -Upgradeable Flash Memory Capability by CD -Video Output Format -Information On HDD Size & Available Space -Erase all program on HDD -Auto Chapter Making (5Min, 10Min, 15Min, Off) -Closed Caption -Menu Language Change -Subtitle Laguage Select -Audio Language Select -Network DVD (Digital 5) -Up Scalar Analog Video Out (720p / 1080i) -HDMI -AV LINK -CM Skip -Time Shift Mode -PIP -DV Camcorder Control File Management & Editing -Rename -Erase Disc ENGLISH X O/X SANYO X O O O (Pushing PWR Key 5sec.) O O PAL O O O X O O O X X X X X O (Buffering 60Min.) X X -Overwrite disc O -Lock -Protect -Edit - Append - Split - Delet - Delet All -Menu Display Thumbnail (Title) Thumbnail Change -Manual Chapter Making / Delete Chapter Mark -Chapter Hide / Unhide -Edit Title Name RECORDING -Dual Format -Video Recording Format -Video Recording Compress Format O O -DVD Type O O REMARK - Only in case that DVD-Video disk supports multi-angle scenes English, German, French, Spanish, Italian, Dutch, Norwegian, Swedish, Portuguese, Hungarian, Russian, Polish, Danish, Finnish, Czech - Erase all titles on the disc - Record a new title to the beginning of the title list X O (Title / Chapter) O (Title / Chapter) O (Chapter) O O X/X O O X DVD + VR Format MPEG II DVD+R / DVD+RW / 3 S P E C IF IC AT IONS SECTION -Disk Recording Rate (Mbps) & Recording Hour with 4.7 GB -HDD Recording Capacity (160GB) 1st Model REMARK HQ : 9.5 Mbps, 60min SP : 5.1 Mbps, 120min EP : 2.5 Mbps, 240min SLP : 1.7 Mbps, 360min HQ : 9.5 Mbps, 32Hr SP : 5.1 Mbps, 66Hr EP : 2.5 Mbps, 128Hr SLP : 1.7 Mbps, 195Hr -DVD data full - Record (Include T.REC, & OTR) - Warning message such as 'DISC FULL' Stop -HDD data full - Record (Include T.REC, & OTR) -Initialize -Finalize -Time Shifting REC -HDD Recording and DVD Playback -DVD Recording and HDD Playback -REC Bit Rate Selection -Transrating DVD HDD ( REC Speed ) -HDD DVD copy Disc Writing speed -HDD DVD copy TIMER -Date Recognized Period -Number of Timer Recording -Clock display method -Manual Clock Setting -Auto Clock Setting -Timer Recording System - General - ShowView (VideoPlus+) - VPS / PDC - EPG -One Touch Recording - Recording Time Display Method DVD+R / DVD+RW DVD+R / DVD-R O O O O X O O ( MP3, JPG, JPEG, DivX) - By GUI & RCU key - X 2.4 2005~2104 8 Events / 1 Year 24 Hour O O O X X X O Recording Hours (Unit of 15Min) -Once Recording -Daily Recording -Weekly Recording -Weekend Recording -Timer Recording Contents Display O O O O O -Method to Timer Recording O -Timer Recording Start Timing On Time -Priority on Overlap Timer Recording X Broadcasting Tuner -Broadcasting System -Channel Selection Method -Band - PAL-B/G,I/I - PAL/SECAM-L -Total Channel Number - PAL BG - PAL I/I - PAL D/K - SECAM L -Position Memory Number -Auto Channel Setting - Auto Search & Memory - Auto Channel Sorting - Auto Station Name Display -Manual Channel Setting - CH Direct Input - Manual Search & Memory - Manual Channel Clear - Manual Space Management (Default) - Automatic Space Management (oldest title erase) Stop HDD ; Max (10 Hours / 15Min in any Mode) Auto Start when Power-Off Warning&Selection when Power-ON - Set turns on eariler than Recording time - Conflict message will be shown up on the screen PAL-B/G Programmable F/S V-L, V-H, UHF V-L/L', V-H, UHF 116 CH( CH 02-69, 74-80, CC 01-41) 116 CH( CH 01-13, 21-69, CC 01-54) 119 CH( CH01-12, 21-69, CC 01-58) 99 CH( CH 02-10, 21-69, CC 01-41) 99CH O Option O License (Royalty) O O O 4 S P E C IF IC AT IONS SECTION - Manual Channel Align -Manual Fine Tuning - Memory Available - E2PROM -RF Modulation Out VIDEO -Horizontal Resolution ( line input ) -Screen size(MPEG encoder) -Video DAC -Video output signal : NTSC / PAL / PAL 60Hz / PAL50Hz / SECAM -Progressive Scanning -Component / RGB Select AUDIO -Audio Recording Format -Sampling Rate -Audio ADC/DAC -S/N Ratio ( line input ) -Dynamic range ( line input ) -Digital output -Audio Digital-to-analog converter -Dolby Digital Down Mix (5.1ch to LtRt out) -Dolby Digital Passthrough -DTS Digital Passthrough -MPEG-2 Audio Passthrough -Dolby Digital 5.1-Ch decoding -DTS Digital 5.1-Ch decoding -Open MP3 Compatible (pre recorded MP3 Discs) -AC-3/PCM data Conversion -3D Surround -Dynamic range control Front Panel -Front Panel Key -LED Indicator -Front A/V jacks -IEEE 1394 DV Input -S-VIDEO Input -USB Input -Memory Card Slot -PCMCIA Front Panel DISPLAY -Device -Display Size -Display Color -Language -Clock / Counter Change - On DVD Out - On DVD In -Clock Display Method -Counter Display Method -Dimmer at Power Off Rear Panel -Analog Audio In (L/R RCA Jack) -Analog Audio Out (L/R RCA Jack) -S-video Out -Composite Video In (Yellow RCA Jack) -Composite Video Out (Yellow RCA Jack) -Component Out (Y/Pb/Pr RCA Jack) -Component Pair Analog Audio Out (L/R RCA Jack) -EURO AV (SCART 1) : Composite / RGB Switchable -EURO AV (SCART 2) : Decoder -DVI -HDMI -Digital Audio In / Out 1st Model O O O X REMARK - 21 pin Scart Cable Accessory <PAL/SECAM> HQ/SP : 500 Lines (DVD+R/RW) EP/SLP : 250 Lines (DVD+R/RW) <PAL/SECAM> HQ/SP: 720x576 (DVD+R/RW) LP/EP : 352x576 (DVD+R/RW) SLP : 352x288 (DVD+R/RW) 8bit PAL O O (OSD) - 576p By Setup menu & RCU key MPEG I Layer II 48 KHz 24bit 65 dB weighted 75 dB DTS, AC3, MPEG2 96kHz/24bit O O O O O X O O O O 11 Key Open/Close, Play, Stop, REC, NEXT, PREV, DVD/HDD, Menu, Standby/ON, PR+ , PRX 2EA FOR AUDIO (R/L) 1EA FOR VIDEO O O X X X LED Array 62(W) x 18(H) mm RED / YELLOW English Clock Clock 24 Hour Real Time O 1 EA 1 EA 1 EA 1 EA 1 EA 1 EA 1 EA X X X X Output Only 5 - Down Mixing SPECIFICATIONS SECTION - Coaxial - Optical Power cord Type - Cord Holder Spec & Serial Number Label Antenna Jack Type - Antenna Jack Layout REMOTE CONTROL Tool Multi-brand TV Control Code type IR (Infra-Red) Response Back-lit remote Joy Stick Jog / Shuttle on Remote Accessories RMC Batteris Bundle Disc Power Cord RF cable Composite A/V Cable Component Video Cable S-video cable (4 pin mini DIN) - 6' Scart Cable Coaxial, Optical Cable IB/Safety Tips IB, Number of Books / Language IB, Color / Size Safety Sheet / Product Registration Card POP Material Advertisement Material Sensormatic Tag 1st Model O O Polarized O O (DEC's spec) F type : 1 Pair In : Up , Out : Down VR-FA3FC0 X DAEWOO O X X X O O O X O O X X X X O TBD B,W / B5 TBD O O TBD 6 REMARK - Mitsubishi format VIDEO BLOCK DIAGRAM 7 1 2 3 4 IIC TUNER A IIC AUDIO MUX R/L TSB41AB1 IIC VFD/KEY IIC B RESET IIC ISP ISP MICOM M3777 IIC MASTER IIC SLAVE CCIR656 VCLK VFD DRIVER IIC CCIR656[7..0] IIS CCIR656 VCLK IIS ADR/CTL DATA DDRAM(256M BIT) CCIR656[7..0] AUDIO ADC SAA7115 RESET B CS 5340 VIDEO DECODER R/L LC74793 VPS PDC REMOCON RECEIVER OPTION MM1443 IC CANAL+ MSP3417 MSP VIDEO IN FROM TUNER VIDEO IN FROM SCART2 VIDEO IN FROM SCART1 VIDEO IN FROM FRONT S-Video VIDEO FROM FRONT AUDIO IN SCART1 AUDIO FROM FRONT DV 1394 INPUT A ATAPI ADR/CTL C DATA FLASH 32M BYTE DVD RECORDER LOADER ATAPI 1 RESET RESET LSI 8652 MPEG2 CODEC C IIS VIDEO SWITCH AND BUFFER ATAPI D R/L LA73053 HDD ATAPI2 RESET VIDEO SWITCH LPF SWITCH PSCAN COMPONENT OUT S-Video TO JACK RGB OUT TO SCART COMPOSITE OUT TO CANAL IIS AUDIO DAC CS4344 D HDMI COMPOSITE OUT TO CANAL HDMI E PSCAN COMPONENT OUT S-Video TO JACK RGB OUT TO SCART IC CANAL+ MM1443 BUFFER AUDIO OUT TO MM1443 E 1 2 3 4 SCHEMATIC DIAGRAM SCHEMATIC DIAGRAM 8 SCHEMATIC DIAGRAM 9 SCHEMATIC DIAGRAM 10 SCHEMATIC DIAGRAM 11 SCHEMATIC DIAGRAM 12 SCHEMATIC DIAGRAM 13 SCHEMATIC DIAGRAM 14 SCHEMATIC DIAGRAM 15 1 2 3 A 12 11 XN0 1 CN01 15P GND (/RST_VI) (MUTE) E5_VPAD VI_VSYNC VI_CLK0 + VI_VSYNC VI_CLK0 1 2 3 4 4 3 2 1 4 3 2 1 0.1UF CN04 0.01UF 0.1UF CN06 GND 0.01UF CN08 1. Pin No. E26, C19, B19, C20 --> N.C 2. Pin No. E24 : add to Pull down resistor 3. Pin No. AF14 : add to Pullup resistor 4. Pin No. AC19 : slave SDA --> Master SDA 5. Pin No. AD21 : slave SCL --> Master SCL 6. Pin No. AE10 : E5_GPIO2 --> slave SCL 7. Pin No. AE9 : E5_GPIO3 --> slave SDA 8. Pin No. AE19 : E5_SIO IRRX --> Master INT 0.1UF CN07 DN02 IN4148 VO_GND 0 1 Y CPST - - C CPST DAC_Vdd0(3.3v) DAC_Vdd1(3.3v) DAC_Dvss DAC1bar DAC0bar DAC_Dvdd (1.8v) DAC6 R/Pr - C CPST Y C CPST - DAC5 B/Pb DAC4 G/Y DAC3 DAC2 DAC1 CPST Y SEL 2 2nd vin VI_D0 VI_D1 VI_D2 VI_D3 VI_D4 VI_D5 VI_D6 VI_D7 VI_D8 VI_D9 24-bit vout 0.1UF VO_GND CN10 + CN09 10UF/6V/A GND USB VO_D16 VO_D17 VO_D18 VO_D19 VO_D20 VO_D21 VO_D22 VO_D23 VO_D0 VO_D1 VO_D2 VO_D3 VO_D4 VO_D5 VO_D6 VO_D7 2nd vout CONTROL 20-bit vin VI_D10 VI_D11 VI_D12 VI_D13 VI_D14 VI_D15 CS[8]- CS[9]- JTAG GPIOx[35] GPIO[6] GPIO[7] GPIOx[31] GPIOx[34] SKT-BGA3 88 VDENC VO_E* VO_ACTIVE* VO_HSYNC* VO_VSYNC* VO_CLK VO_D0 VO_D1 VO_D2 VO_D3 VO_D4 VO_D5 VO_D6 VO_D7 VO_D8* VO_D9* VO_D10* VO_D11* VO_D12* VO_D13* VO_D14* VO_D15* VIO_D0* VIO_D1* VIO_D2* VIO_D3* VIO_D4* VIO_D5* VIO_D6* VIO_D7* VIO_D8* VIO_D9* VI_E0 VI_VSYNC0 VI_CLK0 VI_CLK1* VI_VSYNC1* VI_E1 VI_D0 VI_D1 VI_D2 VI_D3 VI_D4 VI_D5 VI_D6 VI_D7 VI_D8 VI_D9 TCK TDI TDO TMS TRST_L CLKI CLKX CLKO BYPASS_PLL EPD_L* RSTO* AI_D0 AI_D1 AI2_D* AI_SCLK AI_FSYNC AI_MCLKI AI_MCLKO A2_SCLK* A2_FSYNC* AO_IEC958 AO_MCLKI AO_MCLKO AO_D0 AO_D1 AO_D2 AO_D3 AO_SCLK AO_FSYNC AO2_D0* V33_E5_USB DN01 IN4148 C6 D6 B6 B5 B4 D7 A8 A7 A6 A5 A4 A3 B15 C10 B9 C8 A16 VOE VO_ACTIVE VOHSYNC VOVSYNC VOCLK 4.7K 22 22 22 22 A10 B10 B11 A11 C11 C12 B12 A12 B13 A13 C13 C14 B14 A14 A15 C15 22/RP 5 VO_0 6 VO_1 7 VO_2 8 VO_3 VO_4 VO_5 VO_6 22/RP VO_7 8 VO_8 7 VO_9 6 VO_10 5 VO_11 VO_12 VO_13 VO_14 VO_15 RN15 4 3 2 22/RP 1 5 6 7 RN17 8 1 2 3 22/RP 4 8 7 6 5 RN19 RN20 RN21 RN22 RN23 B16 C16 D16 B17 C17 D17 B18 C18 A19 D18 GND B20 A21 A17 A18 C20 A20 C19 B19 B23 B22 A22 B21 C25 B26 C24 A26 B8 A9 B7 D8 C7 22/RP 5 VO_16 6 VO_17 7 VO_18 8 VO_19 VO_20 VO_21 VO_22 VO_23 22 GND A1 A2 H1 H4 D9 C9 D26 E24 E26 D24 C26 B24 A24 E23 D25 A23 B25 A25 G24 G23 F26 G25 F24 E25 F25 RN13 4 3 2 22/RP 1 5 6 7 8 RN12 V33_E5_DAC_AVDD GND 7 Pr/R_Out CN03 7 7 7 7 C_Out Pb/B_Out Y_Out Y/G_Out 7 12 12 12 12 RN18 RN16 RN14 (NC) 12 CVBS_Out E5_VPAD VO_DE VO_HSYNC VO_VSYNC VO_CLK VO_D0 VO_D1 VO_D2 VO_D3 VO_D4 VO_D5 VO_D6 VO_D7 VO_D8 VO_D9 VO_D10 VO_D11 VO_D12 VO_D13 VO_D14 VO_D15 VO_D16 VO_D17 VO_D18 VO_D19 VO_D20 VO_D21 VO_D22 VO_D23 E5_GPIOx45 E5_GPIOx29 Change List CN05 100UF/10V V18_E5_DAC_DVDD VO_D[23..0] /RST_SiI9190 VI_D0 (NC) VI_D1 (NC) VI_D2 VI_D3 VI_D4 VI_D5 VI_D6 VI_D7 VI_D8 VI_D9 E5_TCK E5_TDI E5_TDO E5_TMS E5_TRST _L (/RST_PHY) E5_AI_SCLK E5_AI_FSYNC (To HDMI_INT) E5_AI_MCLKO E5_AO_MCLKO E5_AO_IEC958 AO_0 AO_1 AO_2 AO_3 E5_AO_SCLK E5_AO_LRCK CLK_E5_CLKI CLK_E5_CLKX E5_GPIOx35 22 22 22 22 22 AI_D0 7 (Input only) E5_GPIO6 (Input only) E5_GPIO7 AI_SCLK 7 RN09 AI_FSYNC 7 RN10 E5_GPIOx32 12 AI_MCLKO 7 RN11 E5_GPIOx31 E5_GPIOx34 AO_IEC958 7,12 RN07 E5_GPIOx33 12 AO_MCLKO 7,12 RN08 E5_GPIOx35 (POWER DOWN LOADER) 11 9 (NC) (NC) (Reserve) VI_D[9..0] 2 CN02 15P 13.5MHZ GND 22 22 22 22 22 22 USB_Avdd0(3.3v) USB_Avdd1(3.3v) USB_VSS0 USB_VSS1 RN01 RN02 RN03 RN04 RN05 RN06 AOUT E4 F4 E3 F3 AO_D0 AO_D1 AO_D2 AO_D3 AO_SCLK AO_FSYNC AIN SYSTEM VIN Dplus_0 Dminus_0 Host_PO_0 Host_OC_0 Dplus_1* Dminus_1* Host_PO_1* Host_OC_1* USB_48MHZ* E2 E1 G1 G2 F2 F1 G3 G4 H2 7,12 12 12 12 7,12 7,12 1 21 2 E5_SDRAM_CLK#1 E5_SDRAM_CLK1 E5_SDRAM_CLK#0 E5_SDRAM_CLK0 5 5 5 1394 T23 R23 P23 N23 VREF D22 SDRAM_VREF E5_SDRAM_WE# E5_SDRAM_CLKE 5,6 E5_SDRAM_RAS# E5_SDRAM_CAS# 5 5 SDRAM_CLK_L1 SDRAM_CLK1 SDRAM_CLK_L0 SDRAM_CLK0 GPIOx[43] GPIOx[44] SKT-U3 GND 5 5 5 5 5 5 ADDR B 3.3V PADS 1000PF CN11 GND CN23 0.1UF GND 0.01UF E5_VDDREF 0.1UF CN14 CN22 1000PF CN13 E5_VPAD 1000PF CN12 SSTL2_VDD 1.8V CORE POWER SDRAM I/F 9 9 4 9 9 5 E5_SDRAM_DQ[31..0] C 3.3V 2.5V SDR DDR SDRAM 0.1UF CN16 GND CN28 1000PF CN27 0.1UF CN19 E5_AVDD 0.1UF 0.1UF GND 3.3V CN18 CN26 E5_AVDD 0.1UF CN17 GND UART2 IDC SIO UART1 RN43 E5_GPIO5 + 10UF/6V/A CN20 10UF/6V/A CN21 C + 1000PF CN42 1000PF CN29 1000PF CN43 1000PF CN30 1000PF CN44 1000PF CN31 GND VREF GND 0.01UF CN45 0.01UF CN32 AtapiAddr0 AtapiAddr1 AtapiAddr2 AtapiAddr3 AtapiAddr4 ATAPI_DATA15 ATAPI_DATA14 ATAPI_DATA13 ATAPI_DATA12 ATAPI_DATA11 ATAPI_DATA10 ATAPI_DATA9 ATAPI_DATA8 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 OEUWEGPIO0 GPIO1 GPIO2 GPIO3 GPIO4 GPIO5 LWEWAITDTACKCS5CS4CS3CS2CS1CS0MA[26] MS[25] MA[24] MA[23] MA[22] MA[5] MA[4] MA[3] MA[2] MA[1] ALE RSTMCONFIG CS0_8BIT 0.1UF CN46 0.01UF CN33 E5_VDDREF + + RN40 ATAPI1_DATA7 ATAPI1_DATA6 ATAPI1_DATA5 ATAPI1_DATA4 ATAPI1_DATA3 ATAPI1_DATA2 ATAPI1_DATA1 ATAPI1_DATA0 /E5_CS2 /E5_CS1 /WAIT E5_/DTACK E5_GPIO4 E5_GPIO5 M2 N2 N3 P3 R2 T1 U1 U3 Y1 V1 V4 R1 W2 W3 T3 HD15 HD14 HD13 HD12 HD11 HD10 HD9 HD8 HD7 HD6 HD5 HD4 HD3 HD2 HD1 HD0 MCONFIG GND ATAPI2_ADD0 ATAPI2_ADD1 ATAPI2_ADD2 ATAPI2_ADD3 ATAPI2_ADD4 ATAPI2_DATA15 ATAPI2_DATA14 ATAPI2_DATA13 ATAPI2_DATA12 ATAPI2_DATA11 ATAPI2_DATA10 ATAPI2_DATA9 ATAPI2_DATA8 ATAPI2_DATA7 ATAPI2_DATA6 ATAPI2_DATA5 ATAPI2_DATA4 ATAPI2_DATA3 ATAPI2_DATA2 ATAPI2_DATA1 ATAPI2_DATA0 AE2 AD3 AC4 AF2 AE3 AF1 AE1 AD2 AC3 AB4 AD1 AC2 AB3 AC1 AB2 AA3 AB1 AA2 Y4 AA1 Y3 10UF/6V/A CN47 10UF/6V/A + + 10UF/6V/A CN48 10UF/6V/A CN35 0.1UF CN49 0.1UF CN36 D 0.1UF CN50 0.1UF CN37 0.1UF CN51 0.1UF CN38 0.1UF CN39 8 ATAPI2_DATA[15..0] 0.1UF CN53 0.1UF CN40 /RST_ATAPI2 8 ATAPI2_DMAACK_L 8 ATAPI2_DMARQ 8 ATAPI2_IORDY 8 ATAPI2_INTRQ 8 ATAPI2_DIOR_L 8 ATAPI2_DIOW_L 8 ATAPI2_ADD[4..0] /RST_ATAPI1 8 ATAPI1_DMAACK_L 8 ATAPI1_DMARQ 8 ATAPI1_IORDY 8 ATAPI1_INTRQ 8 ATAPI1_DIOR_L 8 ATAPI1_DIOW_L 8 8 ATAPI1_DATA[15..0] ATAPI1_ADD[4..0] E5_MA 22 8 E5_M A5 7,8 E5_M A4 7,8 7,8 E5_M A3 E5_M A2 7,8 E5_M A1 7,8 HD[15..0] (ETHNET) /E5_CS0 (FLASH)8 Caps with smaller capacitance values to be closer to respective power pins compared to those of larger values. All should be as close as possible. CN34 7,8 RX 2 TX2 8 8 E5_VPAD 10K 10K GND 0.1UF CN54 E5_VCORE GND 0.1UF CN41 RN26 RN25 E5_VPAD VCC 10K GND E5_VPAD + FBMJ2125HS420-T RN28 10K 10K RN27 10UF/6V/A CN56 LN05 V18_E5_DAC_DVDD E5_V5BIAS E5_VPAD V33_E5_DAC_AVDD E5_VDDREF E5_AVDD V33_E5_USB SSTL2_VDD FBMJ2125HS420-T R544 33 Delete Component TCON_06/2.0mm 1 2 3 4 5 6 JP9 JTAG HEADER FBMJ2125HS420-T FBMJ2125HS420-T LN04 LN03 FBMJ2125HS420-T LN02 LN01 0.1UF 10K 10K CN58 E5_VCORE 10K 10K 10K 0.1UF GND 0.1UF CN55 5V E5_VPAD 3.3V V25 2.5V V18 RX 1 TX1 RN29 RN30 RN32 RN33 RN34 RN35 CN59 1 1.8V 1 E5_GPIOx29 E5_GPIOx31 E5_GPIOx34 E5_GPIOx32 E5_UART1_RX E5_TRST _L E5_TDO E5_TDI E5_TMS E5_TCK 7,8 E5_GPIO6 E5_GPIO7 E5_GPIO3(SDA) E5_UART 1_TX E5_GPIO0 (FP D_HOST) E5_GPIO1 (INT_VI) E5_GPIO2(SCL) 7 (/ETHER_IRQ) E5_GPIO3(SDA) (Reset Audio and BTSC) E5_GPIO4 (Ain_Sel1) E5_GPIO5 (Ain_Sel2) /E5_WEL 7,8 /E5_OE 7,8 7,8 1 E5_ALE /SYS_RST 1 E5_VPAD E5_UART2_RX 10K 10K 10K 10K 10K 10K 10K 10K E5_UART 2_TX ATAPI1_ADD0 ATAPI1_ADD1 ATAPI1_ADD2 ATAPI1_ADD3 ATAPI1_ADD4 ATAPI1_DATA15 ATAPI1_DATA14 ATAPI1_DATA13 ATAPI1_DATA12 ATAPI1_DATA11 ATAPI1_DATA10 ATAPI1_DATA9 ATAPI1_DATA8 AD6 AF3 AC5 AE4 AF4 AD5 AD4 RN36 RN37 RN38 INT(MASTER) RN52 /WAIT /E5_CS2 /E5_CS1 RN39 RN41 /E5_CS0 MCONFIG RN42 D E5_/DTACK E5_SPI_CS3 Y2 W1 V3 U4 P1 W4 V2 U2 T2 R3 P2 N1 M1 AD11 AE12 AF11 AC11 AF12 AE13 AE11 AD14 AE15 AD13 AD16 AC16 AE17 AD15 AE16 AD17 AF13 AC17 AD8 AE14 AE10 AE9 AF9 AF10 AF14 AC10 AD10 AF5 AE5 AF19 AF18 AF17 AF16 AE6 AC8 AF6 AD7 AE7 AF7 AD9 AC9 AE8 AF8 AF15 AE18 D10 AD12 E5_VPAD General decoupling cap placement: ATAPI2_DATA15 ATAPI2_DATA14 ATAPI2_DATA13 ATAPI2_DATA12 ATAPI2_DATA11 ATAPI2_DATA10 ATAPI2_DATA9 ATAPI2_DATA8 ATAPI2_DATA7 ATAPI2_DATA6 ATAPI2_DATA5 ATAPI2_DATA4 ATAPI2_DATA3 ATAPI2_DATA2 ATAPI2_DATA1 ATAPI2_DATA0 Atapi2Addr0 Atapi2Addr1 Atapi2Addr2 Atapi2Addr3 Atapi2Addr4 ATAPI2_RESET_L ATAPI2_DMAACK_L ATAPI2_DMARQ ATAPI2_IORDY ATAPI2_INTRQ ATAPI2_DIOR_L ATAPI2_DIOW_L ATAPI_DATA7 ATAPI_DATA6 ATAPI_DATA5 ATAPI_DATA4 ATAPI_DATA3 ATAPI_DATA2 ATAPI_DATA1 ATAPI_DATA0 ATAPI_RESET_L SD_SECSTART ATAPI_DMAACK_L SD_ERROR ATAPI_DMARQ SD_CLK ATAPI_IORDY SD_ACK ATAPI_INTRQ SD_RDREQ ATAPI_DIOR_L SD_WRREQ ATAPI_DIOW_L CD_C2PO CD_BCK CD_LRCK CD_DATA MA[21] MA[20] MA[19] MA[18] MA[17] MA[16] MA[15] MA[14] MA[13] MA[12] MA[11] MA[10] MA[9] MA[8] MA[7] MA[6] SD_D[7] SD_D[6] SD_D[5] SD_D[4] SD_D[3] SD_D[2] SD_D[1] SD_D[0] 10K 10K 10K 10K MASTER PCMCIA_IOWPCMCIA_IORWR- LDSUDS- SBP_FRAME SBP_ACK SBP_RD SBP_REQ SBP_CLK SBP_D[7] SBP_D[6] SBP_D[5] SBP_D[4] SBP_D[3] SBP_D[2] SBP_D[1] SBP_D[0] D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 RD WAITDTACKD31 D30 D29 D28 D27 D26 D25 D24 D23 D22 D21 D20 D19 D18 D17 D16 RDDMAREQ HINTA0 A1 A2 RSTMCONFIG CS- SLAVE SCL(MASTER) RN51 GPIOx[23] GPIOx[22] GPIOx[21] GPIOx[20] GPIOx[19] GPIOx[18] GPIOx[17] GPIOx[16] All the singals with * and the ATAPI-2 I/F are not available in 308-pin package NOTE: IR RN44 E5_GPIO4 PLL 0.1UF 0.1UF CN60 GND 0.01UF CN25 E5_AVDD 0.01UF CN24 0.1UF CN15 E5_VCORE 5V GND SPI 10K RN45 E5_GPIOx35 PLL E5.1-BGA-388-A TOP VIEW DATA 10K E5_GPIO2(SCL)RN46 SDA(MASTER) RN50 10K RN47 E5_GPIO1 10K RN48 E5_GPIO0 10K RN49 E5_SPI_CS2 AVDD0 AVDD1 AVDD2 AVDD3 VDDX B 9 BIO_PHY_DATA7 BIO_PHY_DATA6 BIO_PHY_DATA5 BIO_PHY_DATA4 BIO_PHY_DATA3 BIO_PHY_DATA2 BIO_PHY_DATA1 BIO_PHY_DATA0 BIO_PHY_CTL1 BIO_PHY_CTL0 BIO_LREQ BIO_LPS BIO_LINK_ON BIO_PHY_CLK K2 K3 J1 J2 M3 M4 L4 J3 L3 J4 L2 L1 H3 K1 9 9 9 9 9 9 9 9 USB_D0+ USB_D0USB_PO0 USB_OC0 USB_D1+ USB_D1USB_PO1 USB_OC1 E5_GPIOx36 9 9 BIO_PHY_DATA7 9 BIO_PHY_DATA6 9 BIO_PHY_DATA5 9 BIO_PHY_DATA4 9 BIO_PHY_DATA3 9 BIO_PHY_DATA2 9 BIO_PHY_DATA1 9 BIO_PHY_DATA0 BIO_PHY_CTL1 BIO_PHY_CTL0 BIO_LREQ BIO_LPS BIO_LINK_ON BIO_PHY_CLK (BIO_PHY_PD) 5 5 5 E5_SDRAM_CS0 AB26 Y23 E5_SDRAM_CS1 E5_SDRAM_A15 AB25 E5_SDRAM_A14 AD23 AF26 AC24 AE26 AD24 AF25 AC23 AE25 AD26 AD25 AB24 AC26 AA24 AB23 AC25 SDRAM__A17 SDRAM__A16 SDRAM__A15 SDRAM__A14 *SDRAM__A13 SDRAM__A12 SDRAM__A11 SDRAM__A10 SDRAM__A9 SDRAM__A8 SDRAM__A7 SDRAM__A6 SDRAM__A5 SDRAM__A4 SDRAM__A3 SDRAM__A2 SDRAM__A1 SDRAM__A0 AC12 VDD_PAD1 AC13 VDD_PAD2 AC14 VDD_PAD3 AC15 VDD_PAD4 D14 VDD_PAD5 D15 VDD_PAD6 D19 VDD_PAD7 D20 VDD_PAD8 P4 VDD_PAD9 R4 VDD_PAD10 T4 VDD_PAD11 9 E5_SPI_CLK E5_SPI_CS3 E5_SPI_CS2 D3 D2 D5 D4 B1 E5_SDRAM_A12 E5_SDRAM_A11 E5_SDRAM_A10 E5_SDRAM_A9 E5_SDRAM_A8 E5_SDRAM_A7 E5_SDRAM_A6 E5_SDRAM_A5 E5_SDRAM_A4 E5_SDRAM_A3 E5_SDRAM_A2 E5_SDRAM_A1 5 E5_SDRAM_A0 5 5 E5_SDRAM_DQM3 5 E5_SDRAM_DQS3 5 E5_SDRAM_DQ315 E5_SDRAM_DQ305 E5_SDRAM_DQ295 E5_SDRAM_DQ285 E5_SDRAM_DQ275 E5_SDRAM_DQ26 E5_SDRAM_DQ25 E5_SDRAM_DQ24 5 5 K23 H26 J26 J23 J25 J24 H24 H25 G26 H23 SDRAM_DQM3 SDRAM_DQS3 SDRAM_DQ31 SDRAM_DQ30 SDRAM_DQ29 SDRAM_DQ28 SDRAM_DQ27 SDRAM_DQ26 SDRAM_DQ25 SDRAM_DQ24 AA4 VDD_CORE1 AA23 VDD_CORE2 AC6 VDD_CORE3 AC21 VDD_CORE4 D11 VDD_CORE5 D12 VDD_CORE6 D13 VDD_CORE7 F23 VDD_CORE8 K4 VDD_CORE9 N4 VDD_CORE10 (FP SCLK) (FP D_FM) AGND0 AGND1 AGND2 AGND3 GNDX AA26 W23 Y24 AA25 E5_SDRAM_DQM2 E5_SDRAM_DQS2 E5_SDRAM_DQ23 E5_SDRAM_DQ22 E5_SDRAM_DQ21 E5_SDRAM_DQ20 E5_SDRAM_DQ19 E5_SDRAM_DQ18 E5_SDRAM_DQ17 E5_SDRAM_DQ16 5 5 M26 L24 K24 K25 K26 L23 L25 L26 M24 M25 SDRAM_DQM2 SDRAM_DQS2 SDRAM_DQ23 SDRAM_DQ22 SDRAM_DQ21 SDRAM_DQ20 SDRAM_DQ19 SDRAM_DQ18 SDRAM_DQ17 SDRAM_DQ16 VDD_25V1 VDD_25V2 VDD_25V3 VDD_25V4 VDD_25V5 VDD_25V6 VDD_25V7 VDD_25V8 12 7 B3 C3 C5 C4 B2 SDRAM_WE_L SDRAM_CKE SDRAM_RAS_L SDRAM_CAS_L E5_SDRAM_DQM1 E5_SDRAM_DQS1 E5_SDRAM_DQ15 E5_SDRAM_DQ14 E5_SDRAM_DQ13 E5_SDRAM_DQ12 E5_SDRAM_DQ11 E5_SDRAM_DQ10 E5_SDRAM_DQ9 E5_SDRAM_DQ8 5 5 C22 D23 M23 N24 P24 R24 T24 U23 VIO E5_SDRAM_DQM0 E5_SDRAM_DQS0 E5_SDRAM_DQ7 E5_SDRAM_DQ6 E5_SDRAM_DQ5 E5_SDRAM_DQ4 E5_SDRAM_DQ3 E5_SDRAM_DQ2 E5_SDRAM_DQ1 E5_SDRAM_DQ0 5 5 N26 R25 N25 P26 P25 R26 T26 T25 U26 U25 SSTL2_VDD CS11CS10- SDRAM_DQM1 SDRAM_DQS1 SDRAM_DQ15 SDRAM_DQ14 SDRAM_DQ13 SDRAM_DQ12 SDRAM_DQ11 SDRAM_DQ10 SDRAM_DQ9 SDRAM_DQ8 BIAS (RDY_FM) (ATN_FM) E5_SPI_MISO E5_SPI_MOSI AD18 AD20 AC18 AE21 AF21 AD22 AE22 8 8 SPI_CLK *SPI_CS3 SPI_CS2 SPI_CS1 SPI_CS0 SPI_MISO SPI_MOSI 8 8 AF23 AE20 AF24 AC20 E5_UART2_TX E5_UART2_RX AE24 AC22 AE23 AF22 GPIOx[25] GPIOx[24] U24 W25 V26 V25 W26 V24 Y26 Y25 W24 V23 (Reserve) 7 7 UART1_RTS UART1_CTS UART1_TX UART1_RX SDA(MASTER) SCL(MASTER) AC19 AD21 E5_GPIOx40 INT(MASTER) AF20 AD19 AE19 *IRTX2 IRTX1 IRRX IDC_DAT IDC_CLK *UART2_RTS *UART2_CTS UART2_TX UART2_RX ATAPI I/F SDRAM_DQM0 SDRAM_DQS0 SDRAM_DQ7 SDRAM_DQ6 SDRAM_DQ5 SDRAM_DQ4 SDRAM_DQ3 SDRAM_DQ2 SDRAM_DQ1 SDRAM_DQ0 AC7 5V_BIAS0 D21 5V_BIAS1 7,8,12 7,8,12 SBP VSS_PC2_CTR1 VSS_PC2_CTR2 VSS_PC2_CTR3 VSS_PC2_CTR4 VSS_PC2_CTR5 VSS_PC2_CTR6 VSS_PC2_CTR7 VSS_PC2_CTR8 VSS_PC2_CTR9 VSS_PC2_CTR10 VSS_PC2_CTR11 VSS_PC2_CTR12 VSS_PC2_CTR13 VSS_PC2_CTR14 VSS_PC2_CTR15 VSS_PC2_CTR16 VSS_PC2_CTR17 VSS_PC2_CTR18 VSS_PC2_CTR19 VSS_PC2_CTR20 VSS_PC2_CTR21 VSS_PC2_CTR22 VSS_PC2_CTR23 VSS_PC2_CTR24 VSS_PC2_CTR25 VSS_PC2_CTR26 VSS_PC2_CTR27 VSS_PC2_CTR28 VSS_PC2_CTR29 VSS_PC2_CTR30 VSS_PC2_CTR31 VSS_PC2_CTR32 VSS_PC2_CTR33 VSS_PC2_CTR34 VSS_PC2_CTR35 VSS_PC2_CTR36 VSS_PC2_CTR37 VSS_PC2_CTR38 C21 C23 L11 L12 L13 L14 L15 L16 M11 M12 M13 M14 M15 M16 N11 N12 N13 N14 N15 N16 P11 P12 P13 P14 P15 P16 R11 R12 R13 R14 R15 T11 T12 T13 T14 T15 T16 R16 E5_V5BIAS ADDR CONTROL ATAPI2 I/F DATA SD/CD VSS_REF R_REF VDD_REF C2 C1 D1 1.2K 1% 16 RN24 A E E 1 2 3 4 SCHEMATIC DIAGRAM 17 1 2 3 4 E5_SDRAM_DQ[31..0] SDRAM_DQ8 SDRAM_DQ9 SDRAM_DQ10 SDRAM_DQ11 SDRAM_DQ12 SDRAM_DQ13 SDRAM_DQ14 SDRAM_DQ15 SDRAM_DQ16 SDRAM_DQ17 SDRAM_DQ18 SDRAM_DQ19 SDRAM_DQ20 SDRAM_DQ21 SDRAM_DQ22 SDRAM_DQ23 SDRAM_DQ27 SDRAM_DQ26 SDRAM_DQ25 SDRAM_DQ24 SDRAM_DQ31 SDRAM_DQ29 SDRAM_DQ30 SDRAM_DQ28 RM03 51/RP 8 1 7 2 6 3 5 4 RM04 51/RP 8 1 7 2 6 3 5 4 RM05 51/RP 1 2 3 4 RM06 51/RP 8 7 6 5 RM07 51/RP 4 3 2 1 RM08 51/RP 8 7 6 5 8 7 6 5 1 2 3 4 5 6 7 8 1 2 3 4 1 2 3 4 E5_SDRAM_DQ8 E5_SDRAM_DQ9 E5_SDRAM_DQ10 E5_SDRAM_DQ11 E5_SDRAM_DQ12 E5_SDRAM_DQ13 E5_SDRAM_DQ14 E5_SDRAM_DQ15 E5_SDRAM_DQ16 E5_SDRAM_DQ17 E5_SDRAM_DQ18 E5_SDRAM_DQ19 E5_SDRAM_DQ20 E5_SDRAM_DQ21 E5_SDRAM_DQ22 E5_SDRAM_DQ23 E5_SDRAM_DQ27 E5_SDRAM_DQ26 E5_SDRAM_DQ25 E5_SDRAM_DQ24 E5_SDRAM_DQ31 E5_SDRAM_DQ29 E5_SDRAM_DQ30 E5_SDRAM_DQ28 E5_SDRAM_DQM0 E5_SDRAM_DQM1 E5_SDRAM_DQM2 E5_SDRAM_DQM3 SDRAM_A0 SDRAM_A4 SDRAM_A2 RM11 22/RP 8 7 6 5 1 2 3 4 E5_SDRAM_A0 E5_SDRAM_A4 E5_SDRAM_A2 4 4 4 4 4 RM23 E5_SDRAM_CS0 RM22 1 2 3 4 E5_SDRAM_RAS# E5_SDRAM_CLKE E5_SDRAM_CAS# E5_SDRAM_WE# A 4 4 E5_SDRAM_CLK0 E5_SDRAM_CLK1 E5_SDRAM_CLK#0 E5_SDRAM_CLK#1 RM14 RM15 RM16 RM17 RM18 RM19 4 RM20 4 RM21 4 4 4 4 22 22/RP 8 7 6 5 22 22 22 22 51 51 51 51 SDRAM_CS0 SDRAM_RAS# SDRAM_CLKE SDRAM_CAS# SDRAM_WE# SDRAM_CLK0 SDRAM_CLK1 SDRAM_CLK#0 SDRAM_CLK#1 SDRAM_DQS0 SDRAM_DQS1 SDRAM_DQS2 SDRAM_DQS3 SDRAM_A12 SDRAM_A11 SDRAM_A10 SDRAM_A5 RM13 22/RP 1 8 2 7 3 6 4 5 E5_SDRAM_A12 4 E5_SDRAM_A11 4 E5_SDRAM_A10 4 E5_SDRAM_A5 4 E5_SDRAM_DQS0 E5_SDRAM_DQS1 E5_SDRAM_DQS2 E5_SDRAM_DQS3 SDRAM_A7 SDRAM_A14 SDRAM_A9 SDRAM_A12 RM12 22/RP 1 2 3 4 8 7 6 5 E5_SDRAM_A7 4 E5_SDRAM_A14 4 E5_SDRAM_A9 4 E5_SDRAM_A12 4 4 4 4 SDRAM_A1 SDRAM_A6 SDRAM_A3 SDRAM_A15 RM10 22/RP 1 2 3 4 8 7 6 5 E5_SDRAM_A1 4 E5_SDRAM_A6 4 E5_SDRAM_A3 4 E5_SDRAM_A15 4 SDRAM_DQM0 SDRAM_DQM1 SDRAM_DQM2 SDRAM_DQM3 SDRAM_DQ4 SDRAM_DQ5 SDRAM_DQ6 SDRAM_DQ7 RM02 51/RP 8 7 6 5 1 2 3 4 E5_SDRAM_DQ4 E5_SDRAM_DQ5 E5_SDRAM_DQ6 E5_SDRAM_DQ7 RM09 22/RP 8 7 6 5 SDRAM_DQ0 SDRAM_DQ1 SDRAM_DQ2 SDRAM_DQ3 E5_SDRAM_DQ0 E5_SDRAM_DQ1 E5_SDRAM_DQ2 E5_SDRAM_DQ3 4 4 4 4 B 6 SDRAM_DQ[31..0] 0.1UF CM18 0.1UF CM13 B 0.01UF CM38 0.01UF CM36 0.1UF CM20 0.1UF CM15 0.1UF CM21 0.1UF CM16 0.1UF CM10 0.1UF 0.01UF CM33 0.01UF CM31 1000PF CM42 1000PF CM39 VREF 1000PF CM43 1000PF CM40 0.01UF CM34 0.01UF CM32 GND_SSTL2 0.01UF CM30 0.01UF CM29 1000PF CM44 1000PF CM41 0.1UF CM11 0.1UF CM07 VREF 4,6 0.1UF CM22 0.1UF CM17 0.1UF CM12 0.1UF CM08 VTT VTT GND_SSTL2 GND_SSTL2 VTT The VTT side of the terminaton resistors should be placed on a wide VTT island on the surface layer. The island is located at each end of the bus, so it does not interfere with the signal routing. C VTT 4,6 VREF VREF VREF should be rou ted over a reference plane and isolated, and possibly shielded with both SSTL2_VDD and SSTL2_GND 0.1UF CM25 1 2 3 4 C GND_SSTL2 LP299 5 NC GND VSENSE VREF ICM03 VTT PVIN AVIN VDDQ 8 7 6 5 VTT GND_SSTL2 0.1UF CM24 0.1UF CM23 SSTL2_VDD 220UF/10V CM47 SSTL2_VDD + D + 10UF/6V/A CM49 1000PF CM46 1000PF CM45 0.1UF CM27 VREF + D 10UF/6V/A CM50 VREF 4,6 6 SDRAM_DQ[31..0] 0.1UF CM28 TERMINATION AT DDR DDR TERMINATION VOLTAGE REGULATOR 0.01UF CM37 0.01UF CM35 SSTL2_VDD 0.1UF CM09 0.1UF CM05 CM06 0.1UF 0.1UF SSTL2_VDD CM04 0.1UF 0.1UF CM03 CM02 CM01 SSTL2_VDD VREF needs to be decoupled to both SSTL2_VDD and SSTL2_GND with balanced decoupling capacitors. 0.1UF CM19 0.1UF CM14 TERMINATION AT E5.1 RM01 51/RP 8 1 7 2 6 3 5 4 4 A 6 6 6 6 6 6 6 6 6 6 6 6 51/RP 1 2 3 4 51/RP 1 2 3 4 51/RP 8 7 6 5 SDRAM_CS0 6 51 51 51 RM24 RM26 6 RM25 6 51 SDRAM_CAS# SDRAM_WE# SDRAM_CLKE 6 RM27 51 51 51 51 51 51 51 51 RM40 51/RP 1 2 3 4 RM41 RM42 51/RP 8 7 6 5 RM43 51/RP 1 2 3 4 RM44 RM45 RM46 51/RP 1 2 3 4 RM47 51/RP 1 2 3 4 RM48 51/RP 5 6 7 8 RM49 51/RP 5 6 7 8 51 51 51 51 6 RM35 6 RM34 6 RM33 6 RM32 6 RM39 6 RM38 6 RM37 6 RM36 8 7 6 5 1 2 3 4 1 2 3 4 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5 1 2 3 4 RM50 51/RP 1 2 3 4 RM5151/RP SDRAM_CLK#0 6 RM31 SDRAM_CLK#1 6 RM30 SDRAM_CLK0 6 RM29 SDRAM_CLK1 6 RM28 SDRAM_DQM0 SDRAM_DQM1 SDRAM_DQM2 SDRAM_DQM3 SDRAM_DQS0 SDRAM_DQS1 SDRAM_DQS2 SDRAM_DQS3 SDRAM_RAS# 6 SDRAM_A14 6 SDRAM_A15 6 SDRAM_A10 6 SDRAM_A12 SDRAM_A11 SDRAM_A9 SDRAM_A8 SDRAM_A7 SDRAM_A6 SDRAM_A5 SDRAM_A4 SDRAM_A0 SDRAM_A1 SDRAM_A2 SDRAM_A3 SDRAM_DQ28 SDRAM_DQ29 SDRAM_DQ30 SDRAM_DQ31 SDRAM_DQ24 SDRAM_DQ25 SDRAM_DQ26 SDRAM_DQ27 SDRAM_DQ20 SDRAM_DQ21 SDRAM_DQ22 SDRAM_DQ23 SDRAM_DQ16 SDRAM_DQ17 SDRAM_DQ18 SDRAM_DQ19 4 3 2 1 4 3 2 1 SDRAM_DQ8 SDRAM_DQ9 SDRAM_DQ10 SDRAM_DQ11 SDRAM_DQ12 SDRAM_DQ13 SDRAM_DQ14 SDRAM_DQ15 8 7 6 5 8 7 6 5 SDRAM_DQ4 SDRAM_DQ5 SDRAM_DQ6 SDRAM_DQ7 SDRAM_DQ0 SDRAM_DQ1 SDRAM_DQ2 SDRAM_DQ3 E E VTT 1 2 3 4 SCHEMATIC DIAGRAM 18 1 2 3 4 SDRAM_CS0 SDRAM_CLKE SDRAM_RAS# SDRAM_CAS# SDRAM_WE# SDRAM_DQM0 SDRAM_DQM1 SDRAM_DQS0 SDRAM_DQS1 5 5 5 5 5 5 5 5 5 5 SDRAM_CLK1 5 SDRAM_CLK#1 SDRAM_DQM2 SDRAM_DQM3 SDRAM_DQS2 SDRAM_DQS3 5 5 5 5 A SSTL2_VDD SDRAM_A0 SDRAM_A1 SDRAM_A2 SDRAM_A3 SDRAM_A4 SDRAM_A5 SDRAM_A6 SDRAM_A7 SDRAM_A8 SDRAM_A9 SDRAM_A10 SDRAM_A11 SDRAM_A12 SDRAM_A14 SDRAM_A15 SDRAM_A0 SDRAM_A1 SDRAM_A2 SDRAM_A3 SDRAM_A4 SDRAM_A5 SDRAM_A6 SDRAM_A7 SDRAM_A8 SDRAM_A9 SDRAM_A10 SDRAM_A11 SDRAM_A12 SDRAM_A14 SDRAM_A15 SDRAM_A0 SDRAM_A1 SDRAM_A2 SDRAM_A3 SDRAM_A4 SDRAM_A5 SDRAM_A6 SDRAM_A7 SDRAM_A8 SDRAM_A9 SDRAM_A10 SDRAM_A11 SDRAM_A12 SDRAM_A14 SDRAM_A15 SDRAM_CS0 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 VREF 5 4,5 5 SDRAM_CLK0 5 SDRAM_CLK#0 SDRAM_A0 SDRAM_A1 SDRAM_A2 SDRAM_A3 SDRAM_A4 SDRAM_A5 SDRAM_A6 SDRAM_A7 SDRAM_A8 SDRAM_A9 SDRAM_A10 SDRAM_A11 SDRAM_A12 SDRAM_A14 SDRAM_A15 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 CM5 2 16MX16 DDR VREF VCC VCC VCC VCCQ VCCQ VCCQ VCCQ VCCQ CLK CLK# CS# CKE RAS# CAS# WE# LDM UDM LDQS UDQS A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10/AP A11 A12 BA0 BA1 ICM02 CM5 1 16MX16 DDR VREF VCC VCC VCC VCCQ VCCQ VCCQ VCCQ VCCQ CLK CLK# CS# CKE RAS# CAS# WE# LDM UDM LDQS UDQS A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10/AP A11 A12 BA0 BA1 10UF/6V/A GND GND GND GNDQ GNDQ GNDQ GNDQ GNDQ NC NC NC NC NC NC NC D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 10UF/6V/A GND GND GND GNDQ GNDQ GNDQ GNDQ GNDQ NC NC NC NC NC NC NC D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 For DMN8652-HDD We used 16 x 16 DDR SDRAM. For DMN8612-HD We used 8 x 16 DDR SDRAM. 49 1 18 33 3 9 15 55 61 45 46 24 44 23 22 21 20 47 16 51 29 30 31 32 35 36 37 38 39 40 28 41 42 26 27 49 1 18 33 3 9 15 55 61 45 46 24 44 23 22 21 20 47 16 51 29 30 31 32 35 36 37 38 39 40 28 41 42 26 27 ICM01 + + A 34 48 66 6 12 52 58 64 43 50 53 14 17 19 25 2 4 5 7 8 10 11 13 54 56 57 59 60 62 63 65 34 48 66 6 12 52 58 64 43 50 53 14 17 19 25 2 4 5 7 8 10 11 13 54 56 57 59 60 62 63 65 B GND GND B SDRAM_DQ16 SDRAM_DQ17 SDRAM_DQ18 SDRAM_DQ19 SDRAM_DQ20 SDRAM_DQ21 SDRAM_DQ22 SDRAM_DQ23 SDRAM_DQ24 SDRAM_DQ25 SDRAM_DQ26 SDRAM_DQ27 SDRAM_DQ28 SDRAM_DQ29 SDRAM_DQ30 SDRAM_DQ31 SDRAM_DQ0 SDRAM_DQ1 SDRAM_DQ2 SDRAM_DQ3 SDRAM_DQ4 SDRAM_DQ5 SDRAM_DQ6 SDRAM_DQ7 SDRAM_DQ8 SDRAM_DQ9 SDRAM_DQ10 SDRAM_DQ11 SDRAM_DQ12 SDRAM_DQ13 SDRAM_DQ14 SDRAM_DQ15 5 SDRAM_DQ[31..0] GND 0.1UF CM6 6 0.1UF CM6 7 0.1UF SSTL2_VDD GND CM6 4 0.1UF 0.1UF CM6 3 SSTL2_VDD GND 0.1UF CM5 8 CM5 9 0.1UF 0.1UF SSTL2_VDD GND CM5 6 CM5 5 SSTL2_VDD C C 0.1UF CM6 8 0.1UF CM6 5 0.1UF CM6 0 0.1UF CM5 7 0.1UF CM6 9 1000PF CM7 5 0.1UF CM6 1 1000PF CM8 1 LAYOUT NOTE: 0.1UF CM7 0 1000PF CM7 6 0.1UF CM6 2 1000PF CM8 2 1000PF CM7 1 1000PF CM7 7 1000PF CM7 8 E5 + 1000PF CM8 3 PLACEMENT 1000PF CM7 2 D 1000PF CM7 3 1000PF CM8 0 CM5 3 10UF/6V/A CM5 4 10UF/6V/A 1000PF CM7 9 + SDRAM_CLK0 SDRAM_CLK1 SDRAM_CS0 D 1000PF CM7 4 1000PF CM8 4 M1 U22 M2 U25 GND GND_SSTL2 E E 1 2 3 4 SCHEMATIC DIAGRAM 1 2 3 4 4 4 GND GND GND 680 8 7 6 5 GND ST M 25P20-VMN GND GND E5_VPAD 0.1UF CM87 RM62 RM61 SPANSION S25FL00 2D0FMAC00 OR 33 33 33 33 33/RP 8 7 6 5 4.7K ATAPI2_ADD4 ATAPI2_DIOW_L 4 ATAPI2_DIOR_L 4 ATAPI2_DMAACK_L ATAPI2_DATA1 0 ATAPI2_DATA 5 ATAPI2_DATA1 1 ATAPI2_DATA 4 GND 10K RC32 ATA2_INTRQ ATA2_IORDY ATA2_DMARQ RC33 RC23 RC24 RC25 4 RC26 1 2 3 4 RC22 RC30 RC29 RC28 RC27 33 33 33 33 10K RC02 ATA2_ CS3F X ATA2_DIOW ATA2_DIOR ATA2_DMACK ATA2_D1 0 ATA2_D 5 ATA2_D1 1 ATA2_D 4 10K RC31 VCC ATA1_C S3F X ATA1_DIOW ATA1_DIOR ATA1_DMACK AT A1_A1 AT A1_A0 AT A1_A2 ATA1_C S1F X /RST_ATA2 0 82 4 ATAPI2_INTRQ 82 4 ATAPI2_IORDY 82 4 ATAPI2_DMARQ 33/RP 8 7 6 5 22 22 LM 03 LM 02 E5_V5BIAS 0.1UF CM88 /RST_ATA1 0 82 4 ATAPI1_INTRQ 82 4 ATAPI1_IORDY 82 4 ATAPI1_DMARQ ATAPI2 (HD) CC02 22PF RC13 RC10 RC11 RC12 4 RC09 1 2 3 4 RC05 RC06 RC07 RC08 ATAPI1_ADD4 ATAPI1_DIOW_L 4 ATAPI1_DIOR_L 4 ATAPI1_DMAACK_L ATAPI1_ADD1 ATAPI1_ADD0 ATAPI1_ADD2 ATAPI1_ADD3 GND 10K RC03 ATA1_INTRQ ATA1_IORDY ATA1_DMARQ E5_V5BIAS 22PF CC01 4.7K RC01 E5_V5BIAS A GND RC34 /RST_ATAPI2 4 ATAPI1_ADD[4..0] 680 AT24C1 6 8 7 6 5 DNS- SST25VF020-20-4C-SA CS VCC SO HOLD WP SCL GND SI EEPROM A0 VCC A1 WP A2 SCL GND SDA ICM05 GND 1 2 3 4 ATAPI1 (LOADER) 1 2 3 4 BK1608HM 121- T RC04 /RST_ATAPI1 GND LM 01 4 ATAPI2_ADD[4..0] 4 4 E5_SPI_CS3 E5_SPI_MISO ICM04 E5_VPAD 2M Bit SPI Flash ATAPI2_DATA 6 ATAPI2_DATA 9 ATAPI2_DATA 7 ATAPI2_DATA 8 ATAPI2_DATA 2 ATAPI2_DATA 13 ATAPI2_DATA 3 ATAPI2_DATA 12 ATAPI2_ADD3 ATAPI2_ADD0 ATAPI2_ADD2 ATAPI2_ADD1 ATAPI2_DATA 0 ATAPI2_DATA 15 ATAPI2_DATA 1 ATAPI2_DATA 14 B 1 2 3 4 1 2 3 4 1 2 3 4 RC17 RC16 RC15 4 3 2 1 4 3 2 1 4 3 2 1 4 3 2 1 33/RP 5 6 7 8 33/RP 5 6 7 8 33/RP 5 6 7 8 RC20 RC21 33/RP 5 6 7 8 4 33/RP 8 7 6 5 33/RP 8 7 6 5 33/RP 8 7 6 5 33/RP 8 7 6 5 4 RC19 RC18 ATAPI2_DATA[15..0] ATAPI1_DATA 8 ATAPI1_DATA 7 ATAPI1_DATA 9 ATAPI1_DATA 6 ATAPI1_DATA 10 ATAPI1_DATA 5 ATAPI1_DATA 11 ATAPI1_DATA 4 ATAPI1_DATA 12 ATAPI1_DATA 3 ATAPI1_DATA 13 ATAPI1_DATA 2 1 2 3 4 RC14 ATAPI1_DATA[15..0] E5_SPI_CLK 4 E5_SPI_MOSI 4 ATAPI1_DATA 14 ATAPI1_DATA 1 ATAPI1_DATA 15 ATAPI1_DATA 0 SCL 4,7,12 SDA 4,7,12 BK1608HM 121- T BK1608HM 121- T B ATA2_D6 ATA2_D9 ATA2_D7 ATA2_D8 ATA2_D2 ATA2_D1 3 ATA2_D3 ATA2_D1 2 ATA2_C S1F X AT A2_A0 AT A2_A2 AT A2_A1 ATA2_D0 ATA2_D1 5 ATA2_D1 ATA2_D1 4 ATA1_D8 ATA1_D7 ATA1_D9 ATA1_D6 ATA1_D1 0 ATA1_D5 ATA1_D1 1 ATA1_D4 ATA1_D1 2 ATA1_D3 ATA1_D1 3 ATA1_D2 ATA1_D1 4 ATA1_D1 ATA1_D1 5 ATA1_D0 GND 0.1UF CM86 E5_VPAD ATA2_DMARQ ATA2_DIOW ATA2_DIOR ATA2_IORDY ATA2_DMACK ATA2_INTRQ AT A2_A1 AT A2_A0 ATA2_C S1F X /RST_ATA2 ATA2_D7 ATA2_D6 ATA2_D5 ATA2_D4 ATA2_D3 ATA2_D2 ATA2_D1 ATA2_D0 CM92 LC46 LC47 LC48 LC49 LC50 LC51 LC52 LC53 LC55 LC29 LC31 LC33 LC35 LC37 LC39 LC41 LC43 LC45 LC18 LC19 LC20 LC21 LC22 LC23 LC24 LC25 LC27 LC01 LC03 LC05 LC07 LC09 LC11 LC13 LC15 LC17 8MB 4MB C BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM BK1608HM 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T 121- T BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 GND GND 2 4 6 8 1 0 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 2 4 6 8 1 0 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 HEADER 20X2 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 PC06 GND GND LC54 LC56 LC30 LC32 LC34 LC36 LC38 LC40 LC42 LC44 RM54,RM60 LC26 LC28 LC02 LC04 LC06 LC08 LC10 LC12 LC14 LC16 RM54,RM57,RM60 HEADER 20X2 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 PC05 RM53,RM57,RM58,RM59 RM53,RM58,RM59 /E5_WEL RM53 DNS-0 BA[22..1] 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T 21- T BK1608HM1 21- T BK1608HM1 21- T BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 21- T BK1608HM1 21- T BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 BK1608HM1 D V33 RM54 0 DNS-0 AT A2_A2 ATA2_C S3F X 0 RC35 GND ATA2_D8 ATA2_D9 ATA2_D10 ATA2_D11 ATA2_D12 ATA2_D13 ATA2_D14 ATA2_D15 KEYWAY (NO PIN) ATA2_CAB_S EL 0 GND ATA1_CAB_S EL AT A1_A2 ATA1_ CS3F X RC53 4,7 HD[15..0] RM55 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 0.1UF RM53,RM60 HD[7] HD[3:2] HD[1:0] HD0 HD1 HD2 HD3 HD4 HD5 HD6 HD7 E5_VPAD RM53,RM57,RM59 GND 00 01 10 11 10 00 01 11 0 1 GND RY/BY/A19 NC/A20/A20 A19/A19/A21 WP#/ACC DNS-4.7K 0.1UF BA1 CM91 HD11 HD3 HD10 HD2 HD9 HD1 HD8 HD0 HD15 HD7 HD14 HD6 HD13 HD5 HD12 HD4 BA17 CM93 E5_VPAD E RM53,RM57,RM58,RM59,RM60 RM53,RM57,RM58,RM59 Not Stuff HOST Read RM54,RM57,RM58,RM59 RM54,RM58,RM60 RM54,RM60 RM54 Stuff ATA1_D8 ATA1_D9 ATA1_D1 0 ATA1_D1 1 ATA1_D1 2 ATA1_D1 3 ATA1_D1 4 ATA1_D1 5 KEYWAY (NO PIN) 8MB 4MB 1MB 2MB Size 0 0 RM59 RM60 RM58 BA2 0 DNS-0 BA2 1 4.7K RM57 V33 A16 BYTE/VIO VSS D15 D7 D14 D6 D13 D5 D12 D4 VCC D11 D3 D10 D2 D9 D1 D8 D0 OE VSS CE A0 RM56 MX29L V320 A15 A14 A13 A12 A11 A10 A9 A8 A19/A19/A21 NC/A20/A20 WE RST ACC WP/ACC RY/BY/A19 A18 A17 A7 A6 A5 A4 A3 A2 A1 ICM07 SKT -TSOP48 BA2 2 BA1 BA17 ACC/VPP WP#/ACC RY/BY/A19 BA19 BA18 BA8 BA7 BA6 BA5 BA4 BA3 BA2 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 SKT-U1 /SYS_RST RM52 10K BA16 BA15 BA14 BA13 BA12 BA11 BA10 BA9 A19/A19/A21 NC/A20/A20 16M/32M/6 4M AMD AMD/ST/SST/FUJITSU/MXIC/AMIC Flash Flash GND DMN8652-HDD 4M DMN8612-HD 2M /SYS_RST RM54,RM57,RM58,RM60 BA1 BA2 BA3 BA4 BA5 BA22 GND BA18 BA19 BA20 BA21 BA14 BA15 4,7 BA16 4,7 BA17 BA6 BA7 BA8 BA9 BA10 BA11 BA12 BA13 RM54,RM57,RM58,RM59,RM60 4 10 15 21 28 34 39 45 13 14 16 17 19 20 22 23 2 3 5 6 8 9 11 12 RM53,RM59 Not Stuff 74LVC16373 GND GND GND GND GND GND GND GND 2B1 2B2 2B3 2B4 2B5 2B6 2B7 2B8 1B1 1B2 1B3 1B4 1B5 1B6 1B7 1B8 RM53 4,7 4,7 4,7 4,7 4,7 4 GND VCC VCC VCC VCC 1A1 1A2 1A3 1A4 1A5 1A6 1A7 1A8 1OE 1LE 2A1 2A2 2A3 2A4 2A5 2A6 2A7 2A8 2OE 2LE ICM06 2MB E5 _M A1 E5 _M A2 E5 _M A3 E5 _M A4 E5 _M A5 E5_ MA22 CM90 0.1UF 7 18 31 42 E5_VPAD 4,7 47 46 44 43 41 40 38 37 1 48 36 35 33 32 30 29 27 26 24 25 1MB GND CM89 0.1UF E5_AL E HD8 HD9 HD10 HD11 HD12 HD13 HD14 HD15 HD0 HD1 HD2 HD3 HD4 HD5 HD6 HD7 D FLASH MEMORY(2 or 4 or 8 MB) Stuff HD[15..0] Size Intel 10UF/6V/A ATA1_DMARQ ATA1_DIOW ATA1_DIOR ATA1_IORDY ATA1_DMACK ATA1_INTRQ AT A1_A1 AT A1_A0 ATA1_C S1F X /RST_ATA1 ATA1_D7 ATA1_D6 ATA1_D5 ATA1_D4 ATA1_D3 ATA1_D2 ATA1_D1 ATA1_D0 1000PF CM85 + 4,7 C DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K RC3 7 RC3 8 RC3 9 RC4 0 RC4 1 RC4 2 RC4 3 RC4 4 DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K DNS -2.2K 2.2K 19 E Nanya 64Mb DDR SDRAM 128Mb DDR SDRAM 256Mb DDR SDRAM Reserve Normal Mode (Jumper 1Debuge Mode (Jumper 2- ESMT - M13S128 168A-6T /E5_CS0 /E5_OE HD[15..0] 5 2) 3) B3 DNS HEADER 3X1 1 2 3 JP1 DELETE Samsung - K4H281638D-TC Micron - MT46V8M16-5 RC4 5 RC4 6 RC4 7 RC4 8 RC4 9 RC5 0 RC5 1 RC5 2 A 4,7 1 2 3 4 4,7 4 SCHEMATIC DIAGRAM 20 1 2 3 4 4 E5_GPIOx35 A USB_OC0 USB_PO0 4 USB_D0USB_D0+ 4 4 4 USB_D1+ USB_D1- USB_PO1 USB_OC1 4 4 GND_PHY_D 10K RD06 4 DNS-10K RD05 E5_VPAD 4 4 USB RD02 100 56PF E5_V5BIAS GND_PHY_D RD07 RD08 RD09 GND_PHY_D 4.7K RD04 22 0.1UF GND 10K GND 15K GND 15K GND 15K GND 15K RD59 RD52 RD51 RD53 RD54 BIO_LPS RD03 680 680 680 B GND 0.1UF CD53 PHY_PC0 PHY_PC1 PHY_PC2 10K GND PHY_XO SYSCLK CTL0 CTL1 D0 D1 D2 D3 D4 D5 D6 D7 PD RD60 1 2 3 4 5 6 7 8 9 10 11 12 ICD01 PHY_XI XD01 24.576MHz BIO_LREQ E5_VPAD 12PF CD02 12PF CD01 FIREWIRE PHY CD04 GND_PHY_D GND_PHY_D RD01 51 CD03 4 BIO_PHY_CLK 4 BIO_PHY_CTL0 4 BIO_PHY_CTL1 4 BIO_PHY_DATA0 4 BIO_PHY_DATA1 4 BIO_PHY_DATA2 4 BIO_PHY_DATA3 4 BIO_PHY_DATA4 4 BIO_PHY_DATA5 4 BIO_PHY_DATA6 4 BIO_PHY_DATA7 4 E5_GPIOx36 (/RST_PHY) GND_PHY_D BIO_LREQ BIO_LINK_ON 4 4 1394 TSB41AB1 S-PQFP-48-TI GND FBMJ2125HS420-T FBMJ2125HS420-T LD53 LD54 0.1UF CD54 LD55 LD56 CD51 0.1UF CD52 0.1UF BK1608HM601-T BK1608HM601-T USB_BDM0 USB_BDP0 BK1608HM601-T BK1608HM601-T 22 22 22 22 RD56 RD55 RD57 RD58 10K 10K 1K 1K PHY_R1 TPBIAS TPA+ TPATPB+ TPB- PHY_R1 PHY_R0 RD15 91K/1% RD14 6.8K/1% GND E5_VPAD PD52 PH7/2MM 7 6 5 4 3 2 1 PH6/2MM 6 5 4 3 2 1 PD51 56.2/1% 56.2/1% RD20 5.11K/1% 220PF 56.2/1% 56.2/1% CD06 RD19 RD18 0.1UF CD16 10UF/6V/A CD09 C GND V33 + V33 GND_PHY_A 0.22UF CD07 + 47UF/10V CD17 1000PF CD10 GND_PHY_A RD17 TPBIAS 6.8K//91K = 6.327K C RD16 GND_PHY_A E5_VPAD GND_PHY_D GND_PHY_A USB_BDP1 USB_BDM1 RD11 36 35 34 33 32 31 30 29 28 27 26 25 V33_PHY_A LD52 LD51 PHY_ISO RD10 RD13 RD12 AGND AVDD R1 R0 AGND TPBIAS TPA+ TPATPB+ TPBAGND AVDD CD05 0.1UF PHY_SE PHY_SM PHY_R0 B PHY_FILT1 PHY_FILT0 48 47 46 45 44 43 42 41 40 39 38 37 LREQ DGND DGND DVDD DVDD XO XI PLLGND PLLVDD FILTER1 FILTER0 RESET LPS DGND C/LKON PC0 PC1 PC2 ISO CPS DVDD TESTM SE SM 13 14 15 16 17 18 19 20 21 22 23 24 PHY_PC0 PHY_PC1 PHY_PC2 PHY_ISO PHY_CPS A 0.01UF CD12 FBMJ2125HS420-T LD03 GND_PHY_D 0.1UF CD11 GND_PHY_A 1UF/10V/A + CD08 0.1UF CD13 TPA+ TPATPB+ TPB- 0.1UF CD18 0.1UF CD15 + 47UF/10V CD19 V33_PHY_A 1000PF CD14 1 cTPB- cTPB+ cTPA- cTPA+ 0.1UF CD20 D GND_PHY_A 0.1UF CD23 0.1UF CD21 1000PF CD22 LD01 YB019T-221 Or DLP31DN201ML4+00-002 from MuRata NONE 4 RD21 2 3 NONE 1 RD22 2 NONE RD23 4 NONE 3 RD24 LD02 YB019T-221 Or DLP31DN201ML4+00-002 from MuRata D cTPAcTPA+ cTPBcTPB+ GND_PHY_D GND_PHY_A E GND_PHY_A PH7/2MM 2MM/PH7/TH 5 4 3 2 1 6 PD01 E 1 2 3 4 SCHEMATIC DIAGRAM 21 1 2 3 4 PH9/2MM 2MM/PH9/TH A GND GND + LC67 V33CONN1 CC17 220uF/10V 0 + GND LC64 0 CC11 220uF/10V GND CC18 0.1uF DNS-0 LC66 B LC68 0 B CC12 0.1uF CC04 47uF/10V V33CONN V5CONN GND CC13 220uF/10V GND + GND + LC60 0/2012 E5_V5_BIAS CC05 220uF/10V V5CONN V33CONN1 V33CONN V2.5CONN V2.5CONN V25_CONN TO Power Board PJ822 V2.5CONN V2.5CONN V33CONN V33CONN V5CONN 9 8 7 6 5 4 3 2 1 PC02 MAIN POWER CONN A GND GND GND + CC23 0.1uF 5 4 CC29 0.1uF 5 4 ADJ VIN ADJ VOUT VSENSE VCTRL ICC02 AP1184 VIN VOUT VSENSE VCTRL ICC01 AP1184 GND CC06 0.1uF V25_CON 2 3 1 2 3 1 GND GND GND 0.1uF CC07 LC62 0/2012 RC57 120 RC56 120 RC55 120 RC54 270 220uF/10V CC08 C GND CC14 0.1uF CC22 0.1uF GND CC21 0.1uF SSTV2-VDD + + CC20 220uF/10V GND + CC16 10uF/10V 220uF/10V CC09 LC63 0/2012 GND GND E5_VCORE(V18) V33 V5CONN For DDR VDD-2.5V GND CC19 330uF/10V GND + GND + CC15 330uF/10V GND + LC65 DNS-0/2012 C GND 0.1uF CC10 E5_V5_BIAS D D E E 1 2 3 4 SCHEMATIC DIAGRAM 1 2 3 GND_VIN 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 PV01 FMN31/1.0mm 1 2 3 4 5 6 7 8 9 PV02 0.1uF CV15 FMN31/1.0mm 0 LV16 0.1uF 0.1uF A E5_UART2_TX E5_UART2_RX 10uF/16V CV14 0 0.1uF CV17 0.1uF CV18 MMZ1608601B MMZ1608601B LV05 LV06 + + + + + + + + + + PC07 2 4 6 8 10 CA51 18pF GND GNDGND CON5X2 1 3 5 7 9 CA52 18pF Pr/R_Out Pb/B_Out Y/G_Out C_Out Y_Out CVBS_Out GNDGND CV25 0.1uF E5_VPAD AO_IEC958 10K RC59 QA02 DNS-BSS138 3 3 B RA54 100 1 1 RA55 DNS-3.3K E5_VPAD TP19 TP18 SDA(MASTER) 1 RF_CVBS 1 REAR_CVBS_IN2 F.C_IN CVBS_IN F.Y_IN F.CVBS_IN SCL(MASTER) DNS-3.3K RA53 E5_VPAD V5CONN DNS-4.7K DNS-4.7K RA56 100 QA01 DNS-BSS138 RA24 RA23 [2] [2] [2] [2] [2] [2] [2] [2] RA17 NONE F.AUDIO_IN(L) AMUTE /SYS_RST E5_SIO_IRRX E5_VPAD GND_VIN CV26 0.1uF F.AUDIO_IN(R) AUDIO_OUT(L) AUDIO_OUT(R) AUDIO_IN(R) AUDIO_IN(L) 0.1uF V33_VIA 0.1uF CV29 7115_VCC CV22 F.AUDIO_IN(R) F.AUDIO_IN(L) CVBS_IN RA58 DNS-10K 100 100 100 MMZ1608601B LV04 MMZ1608601B MMZ1608601B RA57 RA51 RA52 MMZ1608601B LA11 MMZ1608601B LV03 0 RA18 NONE 0 0.1uF CV21 RA15 CV24 0.1uF 0.1uF CV20 RA16 LV02 0.1uF CV19 LV01 F.C_IN F.Y_IN F.CVBS_IN + CV23 100uF/16V GND RC60 GND GND 0.1uF CV16 RV15 0 RV11 0 0 0 RV12 RV10 RA11 RA13 AUDIO_IN(L) AUDIO_IN(R) /RST_7115 E5_GPI03(SDA) E5_GPI02(SCL) GND_VIN NONE CV13 NONE CV12 NONE 4 + NONE LV17 0/2012 B C RV17 RV25 RV26 RA14 11K LA01 CA13 10uF/50V CA12 0.1uF 5 6 10 AUDIO_OUT(R) + 12 10 11 14 15 7115_VCC GND_VIN 7 + 10uF/10V CA11 10uF/10V CA09 0.1uF CA04 1uF/50V CA05 0.1uF CA08 0.1uF 10uF/10V SDA SCL V33_VIA + CA03 1uF/50V CA01 10uF/10V 0.1uF CV11 GND_VIN 7115_VCC AUDIO_OUT(L) + + CA14 10uF/50V CA17 CA16 LA03 100 100 100 CLK_VI_XTALI XV01 24.576MHz V5CONN 20pF CV10 20pF CLK_VI_XTAL 0.047uF NONE CV06 CV05 V5CONN RA12 11K 20K 20K 0.047uF CV08 NONE CV07 0.047uF 0.047uF NONE CV28 NONE CV27 CV02 0.047uF CV01 CV03 CV09 0.047uF CV04 GND_VIN C RA01 5.1 9 15 24 43 75 1 25 51 83 33 93 68 58 27 23 17 11 32 31 8 5 6 4 7 41 42 47 21 80 20 18 19 16 14 13 10 12 22 CA06 0.1uF VSSA2 VSSA1 VSSA0 VDDCI VDDE VDDE VDDE VDDE VDDI VDDI VDDI VDDI VDDI CE VDDA0 VDDA1 VDDA2 SDA SCL VXDD VXSS XTAL XTOUT XTALI AMXCLK ITRDY ITRI AGND XTRI AI11 AI12 AI1D AI21 AI22 AI2D AI24 AI23 AOUT VQ FILT+ AOUTR AOUTL CA10 0.1uF AINR AINL VQ REF_GND FILT+ CS5340 ICA01 D CS4344 ICA02 ASDAT0 ABCK ALRCK + RA02 10K V5CONN 7115_VCC 9 1 16 MCLK 22 22 22 22 RA06 RA07 RA08 RA09 1 2 3 4 ACLK [2] [2] [2] [2] E CA15 10uF/16V RA10 10K/NC 22 22 22 VCC 22 V5CONN 10K RV23 ARCLK ARLRCK ARBCK AI_DO VI_CLK0 TP12 RTC0 1 22 4.7K 4.7K 4.7K LA02 VI_D5 VI_D4 VI_D3 VI_D2 RV18 33/RP 5 6 7 8 4 VI_VSYNC0 VI_D9 VI_D8 VI_D7 VI_D6 RV19 33/RP 5 6 7 8 DNS-33 4 3 2 1 VI_3 VI_2 VI_1 VI_0 RV22 RV24 4 3 2 1 VI_7 VI_6 VI_5 VI_4 RA22 RA20 RA21 RA03 RA05 RA04 CA02 10uF/10V VI_7 VI_6 VI_5 VI_4 VI_3 VI_2 VI_1 VI_0 VI_[7..0] 2 8 7 + 30 38 88 63 76 50 26 100 97 98 2 3 99 29 45 28 94 95 92 91 96 35 34 36 81 82 84 85 86 87 89 90 46 54 55 56 57 59 60 61 62 RA19 CA07 0.1uF RESON VSSI VSSI VSSI VSSE VSSE VSSE VSSE TRSTN TCK TDO TDI TMS LLC2 ICLK LLC XCLK XDQ XRH XRV XRDY RTS1 RTS0 RTCO XPD7 XPD6 XPD5 XPD4 XPD3 XPD2 XPD1 XPD0 IDQ IPD7 IPD6 IPD5 IPD4 IPD3 IPD2 IPD1 IPD0 SAA7115 ICV01 E 4 SDIN SCLK LRCK D RST M0 M1 MCLK LRCK SCLK SDOUT 13 A 6 VA GND 5 2 2 3 VL 9 VA + AGND + 8 22 VD 64 65 66 67 69 70 71 72 52 53 48 49 TEST5 TEST4 TEST3 TEST2 TEST1 TEST0 HPD7 HPD6 HPD5 HPD4 HPD3 HPD2 HPD1 HPD0 IGPV IGPH IG0 IG1 79 78 77 74 73 44 RV09 ASCLK ALRCLK AMCLK RV16 39 40 37 RV14 RV13 + V33CONN [2] [2] [2] [2] VI_D[9..2] 4 1 2 3 4 SCHEMATIC DIAGRAM 23 4 4 4 4 4,7 4,7 4 AO_IEC958 AO_D0 AO_D1 GND AO_D2 AO_D3 GND E5_GPIOx33 E5_GPIOx40 V5CONN LV61 MMZ1608601B MMZ1608601B LA64 LA65 GND 0.1uF CA61 MMZ1608601B MMZ1608601B MMZ1608601B MMZ1608601B LA71 LA62 LA63 LA61 HEADER 16X2 2x16pin/pitch-100mil/Female 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 VO_D1 VO_D0 VO_D2 VO_D3 VO_D6 VO_D4 VO_D5 VO_D7 VO_D10 VO_D8 VO_D9 VO_D11 VO_D13 VO_D12 VO_D14 VO_D15 1 3 5 7 9 11 13 15 17 19 MMZ1608601B MMZ1608601B LA66 MMZ1608601B LA69 LA70 MMZ1608601B MMZ1608601B LA67 LA68 HEADER 10X2 2x10pin/pitch-100mil/Female 2 4 6 8 10 12 14 16 18 20 Digital Audio Connector PA03 GND VO_CLK GND 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 PV03 Digital Video Connector CV61 0.1uF V33 VO_VSYNC VO_HSYNC VO_DE GND VO_D17 VO_D19 VO_D18 VO_D16 VO_D23 VO_D21 VO_D20 VO_D22 GND 4 SCL SDA GND AO_MCLKO GND AO_FSYNC GND AO_SCLK E5_GPIOx29 E5_GPIOx32 VO_D[23..0] 4,7 4 4 4,7 4,7 4,7,8 4,7,8 SCHEMATIC DIAGRAM PCB CIRCUIT BOARD A. PCB MAIN TOP 24 PCB CIRCUIT BOARD B. PCB MAIN BOTTOM 25 PCB CIRCUIT BOARD C. MPEG PCB TOP 26 PCB CIRCUIT BOARD D. MPEG PCB BOTTOM 27 PCB CIRCUIT BOARD E. POWER PCB BOTTOM 28 PCB CIRCUIT BOARD LOGIC PCB PANEL 1 29 PCB CIRCUIT BOARD LOGIC PCB PANEL2 30 AAA INSTRUMENT DISASSEMBLY NO. 1 2 3 4 5 6 PART NAME COVER TOP SCREW TAPPTITE SCREW TAPPTITE TOTAL DVD SCREW DAMPER TAPPTITE DAMPER HDD PART NO. Q'TY MATERIAL REMARK DW-97P0488310 1 PCM T0.5 DW-7173300852 5 TT2 BIN 3X8 MFZN BK 3CR COVER TOP FIX DW-7171260651 4 TT2 PAN 2.6X6 MFZN 3CR LOADER FIX DW-97QD021610 1 DDW-806S-D DW-97P3121250 4 TT2 3X14 WAS SPECIAL 3CR HDD+Cov Bot FIX DW-97P2627700 4 BUTHYL, φ10 1 WD800BB-**JHCO 80G 2M HVR-DX700only DW-97P0D007H0 7 HDD DW-97P0D005H0 1 WD1600BB-55RDA0 160G 2M HVR-DX710only 8 BRACKET HDD DW-97P2448700 1 SECC T1.0 9 SCREW MACHINE DW-7043350651 4 BIN M3.5*6 3CR HDD FIX 10 SCREW TAPPTITE DW-7174300851 4 TT2 RND 3X8 MFZN 3CR PCB MPEG FIX 11 PCB MPEG MANUAL AS DW-PVMGMSE746 1 DG-M23E1D-HR/0 12 SCREW TAPPTITE DW-7174300851 4 TT2 RND 3X8 MFZN 3CR PCB POWER FIX 13 PCB POWER MANUAL AS DW-PVPWMSE613 1 DG-M21D1D-HB 14 SCREW TAPPTITE DW-7174300851 3 TT2 RND 3X8 MFZN 3CR PCB MAIN FIX 15 PCB MAIN MANUAL AS DW-PVMPMSE746 1 DG-M23E1D-HR/0 16 COVER BACK DW-97P0488403 1 SECC T0.6 17 SCREW TAPPTITE DW-7173500852 2 TT2 BIN 5X8 MFZN BK 3CR FAN FIX 18 SCREW TAPPTITE DW-7173300652 1 TT2 BIN 3X6 BK 3CR TMI FIX 19 SCREW TAPPTITE DW-7173300852 1 TT2 BIN 3X8 MFZN BK 3CR COVER BACK FIX 20 SCREW TAPPTITE DW-7173300852 2 TT2 BIN 3X8 MFZN BK 3CR JACK A/V RE FIX 21 MOTOR FAN DW-97P8101000 1 RDM5015S(50X50X15)12V 5000 RPM ALL SLEEVE 22 COVER BOTTOM DW-97P0488200 1 SECC T0.8 23 PCB LOGIC MANUAL AS DW-PVLAMSN789 1 DG-M23D1N-GS 24 SCREW TAPPTITE DW-7174300851 2 TT2 RND 3X8 MFZN 3CR JACK A/V FR FIX 25 CUSHION LEG DW-97P4220000 4 EVA T2.0 CHASSIS BOTTOM 26 SCREW TAPPTITE DW-7174300851 2 TT2 RND 3X8 MFZN 3CR PANEL FIX 27 PANEL FRONT AS* DW-97PP349611 1 DG-M23,HIPS(VO),DV 28 SCREW TAPPTITE DW-7174300851 2 TT2 RND 3X8 MFZN 3CR PLATE EARTH AB FIX 29 PLATE EARTH AB DW-97P0919100 2 SUS 304 CSP T=0.2 30 CLAMP WIRE DW-97P4603400 1 EGI T0.6+PVC TUBE L=70MM * When you order spare parts with the *-mark to our service team, please inform them on PART NO. with your model No. such as DW-97PP349611 (HVR-DX700). Note 1) Only the parts in above list are used for repairing. 2) Other parts except the above parts can't be supplied. 31 PACKING VIEW NO. PART NAME PART NO. Q'TY MATERIAL REMARK 1 PAD FRONT/BACK DW-97P4936200 1 EPS 2 POLY BAG FOR SET DW-97P4820000 1 1030*650*T0.5 PE FOAM 3 BOX CARTON* DW-97P5060520 1 COLOR(505X452X136) 4 MANUAL OWNERS DW-97P95600D0 1 EC MODEL 5 CABLE RF DW-97P881RP10 1 PAL 1.0M 6 COVER ACCESSORY DW-97P0424100 1 LD-PE T0.05 7 REMOCON HANDSET AS DW-97P1RA3FC0 1 VR-FA3FC0 GYGY3401A AAA 8 BATTERY DW-486A716202 2 AAA 1.5V(SUPERGARD) 9 CABLE RCA DW-97P880P815 1 3P-3P WEL-WHT-RED 1.5M * When you order spare parts with the *-mark to our service team, please inform them on PART NO. with your model No. such as DW-97P5060520 (HVR-DX700). SANYO Electric Co., Ltd. Osaka, Japan Sept/’06 32