Download ADSP-21065L: DSP、マイクロコンピュータ

Transcript

DSPマイクロコンピュータ

ADSP-21065L

概要

64 Mワード外部アドレス範囲

通信、オーディオ、自動車、計装および工業分野のアプリケーショ

プログラム可能な12本のI/Oピンとイベント・キャプチャー・オプ

ンに最適な高性能シグナル・コンピュータ

ションを持った2つのタイマー

スーパー・ハーバード・アーキテクチャ・コンピュータ(SHARC )

ADSP-2106xファミリーとコード互換

4つの独立したバスによりデュアル・データ、命令、I/Oのフェッ

208ピン MQFP、196ピンMini-BGAパッケージ

チを1サイクルで実行

3.3 V電源電圧動作

32ビット固定小数点演算/32ビットおよび40ビット浮動小数点演算

544Kビットの内部SRAMメモリと集積されたI/O周辺部

フレキシブルなデータ・フォーマットと40ビット拡張精度

I2Sサポート、8つの同時受信および送信チャンネル

32ビット単精度および40ビット拡張精度IEEE浮動小数点データ・

特長

80ビットの加算器2個を持つ32ビット固定小数点データ・フォー

フォーマット

66 MIPS、最高198 MFローPS、連続132 MFLOPSの演算性能

マット、整数および分数

ユーザーが構成できる544 Kビット内部SRAMメモリ

並列演算

2つの外部ポートDMAチャンネルと8つのシリアル・ポートDMA

チャンネル

1サイクルで乗算とALU演算を並列処理、

ふたつのメモリのリード

低価格外部メモリ(@66 MHz)に直接インターフェースできる

/ライトと命令のフェッチを同時処理

SDRAMコントローラ

乗算と同時加/減算でFFTバタフライ演算を高速に処理

1024ポイント複素FFTベンチマーク:0.274 ms

(18, 221サイクル)

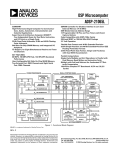

コア・プロセッサ

デュアル・ポートSRAM

データ

ADDR

DAG2

8 x 4 x 24

データ

I/Oポート

ADDR

データ

ADDR

データ

ブロック1

ADDR

DAG1

ブロック 0

ポート・ブロック

プロセッサ・ポート

8 x 4 x 32

JTAG

2つの独立したデュアル・

命令キャッシュ

32 x 48ビット

7

テストと

エミュレーション

外部ポート

プログラム・

シークエンサ

24

PM アドレス・バス

32

DMアドレス・バス

48

PMデータ・バス

IOD

48

IOA

17

SDRAM

インターフェース

アドレス・バス

MUX

24

マルチプロセッサ・

インターフェース

バス接続

(PX)

データ・バス

MUX

40 DMデータ・バス

32

ホスト・ポート

データ・

レジスタ・

ファイル

乗算器

16 x 40 ビット

IOP

レジスタ

(メモリ・マップ)

バレル・

シフタ

ALU

コントロール、

ステータス、

タイマーと

データ・バッファ

DMA

コントローラ

4

(2 Rx, 2Tx)

SPORT 0

(I2S)

(2 Rx, 2Tx)

SPORT 1

(I2S)

I/Oプロセッサ

図1.機能ブロック図

*SHARCはアナログ・デバイセズ社の登録商標です。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、

当社はその情報の利用、また利用したことにより引き起こされる第3者の特許または権

利の侵害に関して一切の責任を負いません。さらにアナログ・デバイセズ社の特許また

は特許の権利の使用を許諾するものでもありません。

REV.A

アナログ・デバイセズ株式会社

本 社/東京都港区海岸1 - 1 6 - 1 電話03(5402)8200 〒105−6891

ニューピア竹芝サウスタワービル

大阪営業所/大阪市淀川区宮原3 - 5 - 3 6 電話06(6350)6868㈹ 〒532−0003

新大阪第2森ビル

ADSP-21065L

構成が変えられる544 Kビットの内部SRAM

ホスト・プロセッサ・インターフェース

コア・プロセッサとDMAが独立してアクセスできる2ポート構成

8、

16、

32ビットのマイクロプロセッサと効率的なインターフェース

ブロック0とブロック1で16、32、48ビット長のデータとプログラ

ホストはADSP-21065LのIOPレジスタに直接リード/ライトが可能

ム・ワードの組み合わせ構成可能

マルチプロセッシング

DMAコントローラ

2つのADSP-21065Lとホスト間の並列バス接続を直接行うための

専用バス調停回路内蔵

10個のDMAチャンネル:

並列バスを介して132 Mバイト/秒の転送レート

外部ポート専用2個、シリアル・ポート専用8個

プロセッサが演算をフルに実行している時も、

並行してバック・グ

ラウンドDMA転送を最大66 MHzのレートで実行。

シリアル・ポート

各種のデータ転送:

独立した送信および受信機能

内部RAMとホスト間

3∼32ビットのシリアル・ワード幅をプログラム可能

内部RAMとシリアル・ポート間

I2Sサポートで8つの送信チャンネルと8つの受信チャンネル

内部RAMとマスター、またはスレーブSHARC間

工業標準CODECに直接インターフェース

内部RAMと外部メモリ、またはI/Oデバイス間

μ則/A則ハードウエア圧縮伸長機能付きのTDMマルチチャンネ

外部メモリと外部デバイス間

ル・モード

マルチチャンネル信号プロトコル

−2−

REV.A

ADSP-21065L

概要

CLKIN

ンピュータ)

は、現存する32ビットDSPでは最高レベルの性能とメ

RESET

RESET

モリ集積度を提供します。また、固定および浮動小数点の両方の機

01

能を、精度や性能を落とさずに提供する唯一のDSPです。

ID1-0

SPORT0

高速で低消費電力のCMOSプロセス、0.35μmテクノロジーで作

ADDR23-0

(198 MFLOPS)を実現。内蔵の命令キャッシュを用いて、すべて

の命令を1サイクルで実行できます。表ⅠにADSP-21065Lの性能

RD

WR

ACK

MS3-0

BMS

SBTS

SW

CS

HBR

HBG

REDY

SPORT1

を示すベンチマークを示します。

TX1_A

TX1_B

RX1_A

RX1_B

ADSP-21065L SHARCは、

浮動小数点DSPをコアに、

544 Kビット

のS R A M メモリやホスト・プロセッサとのインターフェース、

DMAコントローラ、SDRAMコントローラ、強化されたシリアル・

コントロール

ポートなどを集積しています。

図1はADSP-21065Lのブロック図で、以下のような機能が示され

ています。

共用のデータ・レジスタ・ファイルを持つ演算ユニット(ALU、

乗算器、シフタ)

ADDR

DATA31-0

TX0_A

TX0_B

RX0_A

RX0_B

られたADSP-21065Lは、32ビットDSPでは最高の性能−66 MIPS

CS

データ

CLOCK

アドレス

ADSP-21065L

#1

バーです。SHARC(スーパー・ハーバード・アーキテクチャ・コ

コントロール

ADSP-21065Lはコストに厳しいアプリケーションのために最適

化された、32ビットプロセッサSHARCファミリーの強力なメン

RAS

CAS

DQM

SDWE

SDCLK1-0

SDCKE

SDA10

データ・アドレス・ジェネレータ(DAG1、DAG2)

CPA

BR2

命令キャッシュとプログラム・シークエンサ

BR1

DATA

ブート

EPROM

(オプション)

ホスト・プロセッサ

(オプション)

CS

ADDR

DATA

ADDR

DATA

CS

SDRAM

(オプション)

RAS

CAS

DQM

WE

CLK

CKE

A10

イベント・キャプチャ・モードを持ったタイマー

図2.ADSP-21065Lシングル・プロセッサ・システム

内部デュアル・ポートSRAM

外部メモリや周辺素子とインターフェースするための外部ポート

独立して並列に配置された演算ユニット

ホスト・ポートとSDRAMインターフェース

DMAコントローラ

算術/論理ユニット(ALU)、乗算器、シフタはすべて1サイクル

強化されたシリアル・ポート

の命令で動作します。3つのユニットは並列に配置され、演算のス

JTAGテスト・アクセス・ポート

ループットを最大にしています。ひとつのマルチ機能命令よって

ALUと乗算器の操作を並行して行えます。

演算ユニットはIEEE 32

表Ⅰ.性能ベンチマーク

ビット単精度浮動小数点、拡張精度40ビット浮動小数点、そして32

ベンチマーク

演算時間

サイクル数

サイクル時間

15.00 ns

1

ビット固定小数点データ・フォーマットを扱うことができます。

データ・レジスタ・ファイル

1024ポイント複素FFT

汎用のデータ・レジスタ・ファイルを使って、演算ユニットと

(4基底、デジット・リバース) 0.274 ms

18, 221

データ・バス間のデータ転送や中間演算結果の保持が行えます。

行列の乗算(パイプライン)

この10ポート、32個のレジスタ(表16個、裏16個)で構成されるレ

[3×3]×[3×1]

135 ns

9

ジスタ・ファイルとADSP-21000のハーバード・アーキテクチャが

[4×4]×[4×1]

240 ns

16

組み合わせられて、演算ユニットと内部メモリ間の自由なデータの

FIRフィルタ(タップ当り)

15 ns

1

IIRフィルタ(バイクワッド当り)

60 ns

4

割り算(Y/X)

90 ns

6

ADSP-21065Lは、データ・メモリ(DM)バスでデータの転送を

平方根の逆数(1/√x)

135 ns

9

行い、プログラム・メモリ(PM)バスで命令とデータの両方を転送

DMA転送レート

264 Mバイト/秒

流れを実現しています。

命令と2つの演算データを1サイクルでフェッチ

するという、強化されたスーパー・ハーバード・アーキテクチャ構

成になっています(図1参照)。プログラム・メモリ・バスとデー

タ・メモリ・バスの分離と、内蔵の命令キャッシュにより、2つの

ADSP-21000ファミリー・コア・アーキテクチャ

演算データと(キャ ッシュからの )命令を1 サイクルで同時に

ADSP-21065LはADSP-21060/ADSP-21061/ADSP-21062とコー

フェッチすることができます。

ド、機能において互換です。ADSP-21065LはSHARCファミリー・

コアの以下の様な機能を備えています。

REV.A

−3−

ADSP-21065L

命令キャッシュ

列で構成されています。各メモリ・ブロックはデュアル・ポート

ADSP-21065Lは命令キャッシュを内蔵しており、1つの命令と2

になっていて、

コア・プロセッサとI/OプロセッサまたはDMAコン

つのデータを扱う3バス動作が可能です。

このキャッシュは選択的

トローラによる独立したアクセスに1サイクルで対応します。この

に使用され、PMバスのデータ・アクセスと命令のフェッチとがバ

デュアル・ポート・メモリと分離した内部バスによって、コアから

スの競合を起こす時にのみ、

命令をキャッシュします。これにより

とI/Oからの、2つのデータ転送を1サイクルで行えます(ADSP-

デジタル・フィルタの乗累算やFFTのバタフライ演算のように中

21065Lのメモリ・マップは図4を参照)。

ADSP-21065Lでは、メモリは最大で16 Kワードの32ビット・

心的な繰り返し処理を最高速で実行できます。

データ、34 Kワードの16ビット・データ、10Kワードの48ビット命

ハードウエア上でサーキュラ・バッファを構成できるデータ・

令(そして40ビット・データ)等に構成できます。また、最大544 K

アドレス・ジェネレータ

ビットまでの異なったビット幅のワードの組合わせも可能です。

ADSP-21065Lの2つのデータ・アドレス・ジェネレータ(DAGs)

は、サーキュラ・データ・バッファをハードウエアで実現していま

すべてのメモリは16ビット、32ビット、または48ビットのワードで

アクセスできます。

す。サーキュラ・バッファはデジタル信号処理で要求される、遅延

各メモリ・ブロックはコードとデータを混合して保持できます

ラインやその他のデータ構造の効果的なプログラミングを可能に

が、もっとも効率的にアクセスできるのは、ひとつのブロックを

し、デジタル・フィルタやフーリエ変換等でよく使用されます。

DMバスを使用したデータ保持に、もうひとつのブロックをPMバ

ADSP-21065Lの2つのDAGは、最高で32個(16の表レジスタのセッ

スを使用した命令やデータの保持に割り当てる場合です。このよ

トと16個の裏レジスタのセット)のサーキュラ・バッファを構成で

うにDMバスとPMバスを各メモリ・ブロックに専用に割り当てる

きるレジスタを持っています。このDAGは自動的にアドレス・ポ

ことにより、1サイクルで2つのデータ転送が可能になります。

この

インタの巻き戻しを行い、

オーバーヘッドを減らし、性能を向上さ

場合、命令はキャッシュの中に用意されていなければなりません。

せ、実行を簡単にします。サーキュラ・バッファは、どのメモリ位

1サイクルでの実行は、一方のデータがADSP-21065Lの外部ポート

置からでも開始、終了できます。

を使用して外部と転送している場合にも可能です。

柔軟性に富んだ命令セット

外部メモリと周辺素子へのインターフェース

ADSP-21065Lの外部ポートは、外部メモリや周辺素子へのイン

48ビットの命令ワードは各種の並列操作を許し、簡潔なプログ

ラミングが可能です。例えば、ADSP-21065Lは乗算や加算、減算、

ターフェースになります。ADSP-21065Lの統一されたアドレス空

分岐等のすべてを、条件によっては1つの命令で処理できます。

間には64Mワードの外部アドレス空間が含まれています。

PMアド

ADSP-21065Lの特長

バス、I/Oアドレス・バス、I/Oデータ・バスと分けられている内部

レス・バス、PMデータ・バス、DMアドレス・バス、DMデータ・

ADSP-21065Lは最大のシステム性能を実現するために最高のシ

バスは、外部ポートでマルチプレクスされて、1本の24ビット・ア

ステム・スループットが得られるように設計されており、クリスタ

ドレス・バスと4本のメモリ・セレクト、1本の32ビット・データ・

ルまたはTTL互換のクロック信号によって駆動できます。ADSP-

バスによる外部システム・バスを生成します。内部のスーパー・

21065Lは命令レートの半分の周波数の入力クロックを使います。

ハーバード・アーキテクチャにより3バス動作が可能で、外部の統

つまり、33 MHz入力クロックで15 nsのプロセッサ・サイクル(こ

一されたアドレス空間は設計の自由度を向上させます。

れは66 MHzに等しい)が得られます。ADSP-21065Lのインター

フェースは以下に示すように動作します。

このデータシートでは、

SDRAMインターフェース

S D R A M インターフェースは、A D S P - 2 1 0 6 5 Lと同期D R A M

1x=入力クロック周波数、2x=プロセッサの命令レートを示しま

(SDRAM)との2xクロック周波数でのデータのやりとりを可能に

す。

下記のクロック動作レートは 1x=33 MHz (命令レート/コア

します。2xクロック周波数での同期式アプローチは、220 Mバイト

/秒までの高スループットでのデータ転送をサポートします。

=66 MHz)を基準にしています。

66 MHz

SDRAMインターフェースは標準のSDRAM(16 Mb、64 Mb、128

外部SRAM

33 MHz

Mb)との直接インターフェースを提供し、ADSP-21065LとSDRAM

シリアル・ポート

33 MHz

の間の付加的バッファをサポートするオプションも含んでいます。

マルチプロセッシング

33 MHz

S D R A M インターフェースは非常に柔軟性に富み、S D R A M は

ホスト(非同期)

33 MHz

ADSP-21065Lの4つの外部メモリ・バンクのどれにでも接続できま

SDRAM

ADSP-21000ファミリー・コアに加えて、

ADSP-21065Lでは以下の

す。

いくつかのSDRAMデバイスが並列に接続されているシステムで

ようなアーキテクチャ機能を持っています。

は、

全体でのタイミング要求に適応するためにバッファリングが必

デュアル・ポートの内部メモリ

要なことがあります。ADSP-21065Lはアドレスとコントロール信

ADSP-21065Lは2バンク構成の544 KビットのSRAMメモリを内

蔵しています。バンク0は288 Kビット、バンク1は256 Kビットで

号のパイプライン処理をサポートして、

自分自身と複数のSDRAM

デバイスとの間のバッファリングを可能にしています。

す。バンク0は2 K×16ビットが9列、バンク1は2 K×16ビットが8

−4−

REV.A

ADSP-21065L

ホスト・プロセッサ・インターフェース

ADSP-21065Lのホスト・インターフェースは、ほとんど付加

ハードウエアを必要とせずに8ビット、16ビット、32ビットの標準

マイクロプロセッサ・バスに簡単に接続できます。プロセッサの

入力クロック・レートまでの非同期転送ができるホスト・イン

ターフェースは、

ADSP-21065Lの外部ポートを通してアクセスされ

ます。ホスト・インターフェースのために2チャンネルのDMAが

使用でき、コードやデータの転送は低いソフトウエア・オーバー

ヘッドで行えます。

ホスト・プロセッサはホスト・バス・リクエスト(HBR)、ホス

ト・バス・グラント(HBG)、レディ(REDY)信号を使ってADSP21065Lの外部バスに要求を送ります。ホストはADSP-21065Lの

IOPレジスタを直接、読み書きでき、DMAチャンネルのセットアッ

プやメイルボックス・レジスタにアクセスできます。ホスト・コ

マンドを効果的に実行できるように、

ベクトル割込みサポートが用

意されています。

DMAコントローラ

ADSP-21065Lの内部DMAコントローラによって、プロセッサを

介在せずに、

オーバーヘッド無しのスムーズなデータ転送が可能で

す。DMAコントローラは独立して動作し、プロセッサ・コアから

その動作が見えないので、

コアがプログラム命令を実行しているの

と同時にDMA操作を行うことができます。

DMA転送はADSP-21065Lの内部メモリと、外部メモリや外部周

辺素子、またはホスト・プロセッサとの間で行われます。DMA転

送はまた、ADSP-21065Lの内部メモリとシリアル・ポートの間でも

実行できます。外部メモリと外部周辺素子の間のDMA転送も行え

ます。16、32、48ビット内部ワードへの外部バス・パッキングが、

DMA転送中に行われます。

ADSP-21065Lには10チャンネルのDMAチャンネルが用意されて

います。8チャンネルがシリアル・ポート経由、2チャンネルがプロ

セッサの外部ポート(ホスト・プロセッサや他のADSP-21065L、メ

モリあるいはI/O転送)経由です。DMA転送を使ってADSP-21065L

にプログラムをダウンロードできます。DMAリクエスト/グラン

ト信号線(DMAR1-2、DMAG1-2)を使って、非同期の外部周辺素子か

ら2つのDMAチャンネルをコントロールできます。他にも、DMA

転送が完了した時に割込みを発生したり、自動リンクDMA転送の

ためのチェイニング機能等が用意されています。

シリアル・ポート

ADSP-21065Lは2つの同期式シリアル・ポートを持ち、広範囲な

デジタルおよびミックスド・シグナル周辺機器との安価なイン

ターフェースを提供します。シリアル・ポートは1xクロック周波

数で動作可能で、各ポートは最大で30 Mビット/秒のデータ・

レートが可能です。各シリアル・ポートは、表と裏の送受信チャン

ネルセットを持ちます。

送信と受信の機能が独立していますので、

柔軟性に富んだシリアル通信が行えます。シリアル・ポートの

データはDMAを介して、

内部メモリと自動的にやり取りできます。

各シリアル・ポートは、DSPシリアル・ポート・モード、I 2 Sモード

(オーディオCODECで良く使われるインターフェース)、TDM(時

分割マルチプレクス)

マルチチャンネル・モードの3つのモードをサ

ポートしています。

シリアル・ポートは下位ビットからでも上位ビットからでも転

送フォーマットを操作でき、

ワードの長さも3から32ビットの間で

選択できます。選択的同期や送信モードも提供し、

オプションとし

てμ則やA則の圧縮伸長も行えます。シリアル・ポートのクロック

やフレーム同期信号は内部での生成も、外部からの供給も可能で

す。

さらに、プロセッサ間の通信を強化するキーワードおよびキー

マスク機能も含んでいます。

REV.A

プログラマブル・タイマーと汎用I/Oポート

ADSP-21065Lは二つの独立したタイマー・ブロックを持ち、それ

ぞれパルス幅生成とパルス・カウントおよびキャプチャを行いま

す。

パルス幅生成モードでは、ADSP-21065Lは最大で71.5秒までの周

期で任意のパルス幅の変調波形を生成できます。

パルス・カウンター・モードでは、ADSP-21065Lはハイ・レベル

またはロー・レベルのパルス幅と入力波形の周期を計測できます。

ADSP-21065Lは入/出力のどちらにも使える、12本のプログラ

マブルな汎用I/Oピンを持ちます。

出力ピンとしては周辺デバイス

への信号線に、入力ピンとしては条件分岐のテスト条件に使えま

す。

プログラムのブート

システムのパワーアップ時、ADSP-21065Lの内部メモリは、8

ビットのEPROMやホスト・プロセッサ、外部メモリ等からブート

することができます。ブート源の選択は、BMS(ブート・メモリ・セ

レクト)ピンとBSEL(EPROMブート)ピンでコントロールされま

す。8、16、32ビットのホスト・プロセッサもブートに使用できま

す。詳細については、データシートの「ピンの説明」のBMSとBSEL

の記述を参照してください。

マルチプロセッシング

ADSP-21065LはマルチプロセッシングDSPシステムに最適な強

力な機能を備えています。統一されたアドレス空間によって、

2つ

のADSP-21065LのIOPレジスタへのプロセッサ間の直接アクセスが

可能です。最大で2つのADSP-21065Lとひとつのホスト・プロセッ

サを含んだシステムをシンプルに、直接接続するために、

専用のバ

ス調停回路が内蔵されています。マスター・プロセッサの交替に

は、1サイクルのオーバーヘッドを必要とするだけです。バス・

ロックによって、セマフォー(信号機)用の不可分な読み出し−更

新−書き込みシークエンスを行えます。プロセッサ間のコマンド

のためにベクトル割込みが用意されています。プロセッサ間の

データ転送の最大のスループットは、外部ポートを使って132Mバ

イト/秒です。

開発支援ツール

ADSP-21065Lには、EZ-ICE®イン・サーキット・エミュレータと

開発ソフトウエアを含む、ソフトウエア、ハードウエアの完全な開

発ツールが用意されています。

ADSP-21060/ADSP-21062用に使っているのと同じEZ-ICEハード

ウエアで、ADSP-21065Lを完全にエミュレートできます。

SHARC開発ツール・ファミリーと、プロジェクト管理機能やデ

バッグ環境を備えたVisualDSP ®の両方ともにADSP-21065Lをサ

ポートしています。VisualDSPプロジェクト管理環境は、ひとつの

集積されたプログラムからのアプリケーション開発とデバッグを

可能にします。

SHARC開発ツールには、算術的表記を基にした使いやすいアセ

ンブラをはじめとして、アセンブリ・ライブラリ/ライブラリア

ン、リンカ、ローダー、サイクル数が正確にわかるインストラク

ション・レベルのシミュレータ、Cコンパイラ、DSP関数や算術関

数を含んだCランタイム・ライブラリ等があります。

VisualDSPデバッガによるCおよびアセンブリ・プログラムの両

方のデバッグでは、以下のことが行えます。

・Cおよびアセンブリ・コードの混合表示

・ブレイク・ポイントの挿入

・ウォッチ・ポイントの設定

・バス動作のトレース

・プログラム実行の履歴

・メモリへの読み書き

・オリジナルのデバッガ・ウインドウの生成

−5−

ADSP-21065L

アナログ・デバイセズ社から入手できるソフトウエアやハード

ウエアの開発支援ツールに加えて、サード ・パーティからも

SHARCプロセッサ・ファミリーをサポートする、さまざまなツー

ルが用意されています。SHARC PCプラグ・イン・カードやマル

チプロセッサ・SHARC VMEボード、それに複数のSHARCや拡張

メモリを載せたドーターボード等が、

ハードウエアとして提供され

ています。これらのモジュールはSHARCPACTMモジュール規定に

基づいています。サード・パーティによるソフトウエアのツール

には、ADAコンパイラやDSPライブラリ、オぺレーティング・シス

テム、ブロック図設計ツール等があります。

Visual IDEで、マルチユーザー・プロジェクトの定義や管理が行

えます。Visual IDEのダイアログ・ボックスとプロパティ・ページ

により、SHARC開発ツールのすべてを構成し管理できます。この

機能によって、以下のことが可能になります。

・開発ツールが入力を処理し出力を生成する方法をコント

ロール

・ツールのコマンドライン・スイッチとの1対1の対応を維持

EZ-ICE®エミュレータは、ターゲット・ボートのプロセッサをエ

ミュレーション中にモニターしたりコントロールするのに、

ADSP21065LプロセッサのIEEE1149.1JTAGテスト・アクセス・ポートを

使用します。EZ-ICEはフル・スピードでのエミュレーションが可

能で、メモリやレジスタ、プロセッサ・スタックの検査や更新がで

きます。プロセッサのJTAGインターフェースを使うことで、動作

を妨げないインサーキット・エミュレーションが保証され、エミュ

レータによってターゲット・システムの負荷やタイミングが影響

を受けることはありません。

付加情報

ADSP-21065Lインストラクション・セットやアーキテクチャに

関しての、より詳細な情報は「ADSP-21065L SHARCユーザーズ・

マニュアル 第3版」と「ADSP-21065L SHARCテクニカル・リファ

レンス」を参照してください。

EZ-ICEおよびVisualDSPはアナログ・デバイセズ社の登録商標です。SHARCPACはアナロ

グ・デバイセズ社の商標です。

ADSP-21065L

#2

CLKIN

RESET

10

ADDR23-0

DATA31-0

ID1-0

コントロール

SPORT0

RESET

RESET

ID1-0

ADDR23-0

DATA31-0

アドレス

CLKIN

データ

ADSP-21065L

#1

CLOCK

01

CPA

BR2

BR1

コントロール

SPORT1

CS

ブート

ADDR

EPROM

データ (オプション)

ホスト・プロセッサ

(オプション)

SPORT0

RD

WR

ACK

MS3-0

BMS

SPORT1

SBTS

SW

CS

HBR

コントロール

HBG

REDY

RAS

CAS

DQM

SDWE

SDCLK1-0

SDCKE

SDA10

CS

ADDR

データ

ADDR

データ

CS

SDRAM

(オプション)

RAS

CAS

DQM

WE

CLK

CKE

A10

CPA

BR2

BR1

図3. マルチプロセッシング・システム

−6−

REV.A

ADSP-21065L

ピンの説明

ADSP-21065Lのピンの定義を以下に示します。同期(S)と示されている入力は、CLKIN(TMSやTDIではTCK)に対応するタイミング要

求を満たしていなければなりません。非同期(A)と示されている入力は、CLKIN(TRSTではTCK)に同期せずに入力してもかまいません。

使用しない入力は、ADDR23-0、DATA31-0、FLAG11-0、SWおよび、内部プルアップ、プルダウン抵抗を持つ入力(CPA、ACK、DTxX、DRxX、

TCLKx、RCLKx、TMSとTDI)を除き、VDDかGNDに接続しておきます。上記で除いたピンは開放したままにしておきます。これらのピ

ンはロジック・レベル保持回路を持ち、入力が内部的にフローティングになるのを防ぎます。

I=入力

S=同期

P=電源

(O/D)=オープン・ドレイン

O=出力

A=非同期

G=グラウンド

(A/D)=アクティブ・ドライブ

T=スリーステート(SBTSが与えられたとき、またはADSP-2106xがバス・スレーブの時)

ピン

タイプ

機能

ADDR23-0

I/O/T

外部バス・アドレス。ADSP-21065Lは、このピンから外部メモリや周辺素子にアドレスを出力します。マ

ルチプロセッサ・システムにおいては、バス・マスターが他のADSP-21065LのIOPレジスタの読み書きの

ためのアドレスを出力します。ホスト・プロセッサやマルチプロセッシングのバス・マスターがIOPレジ

スタを読み書きしている時、そのADSP-21065Lのアドレスは入力となります。

DATA31-0

I/O/T

外部バス・データ。ADSP-21065Lは、このピンからデータや命令を入出力します。外部データ・バスは、

32ビット単精度浮動小数点データと32ビット固定小数点データをビット31-0を使って転送します。

16ビッ

トのショート・ワードは、バスのビット1 5 - 0 を使って転送されます。使用していないD A T A

ピンにプルアップ抵抗を使う必要はありません。

MS3-0

I/O/T

メモリ・セレクト。対応する外部メモリのバンクのチップ・セレクトとして使われます。内部アドレ

スADDR25-24がデコードされてMS3-0になります。

MS3-0線はデコードされたメモリ・アドレス線で、

他のア

ドレス線と同時に変化します。外部メモリへのアクセスが起こらないときは、MS3-0は動作しません。し

かし、条件付きのメモリ・アクセス命令が実行されると、その条件の真偽にかかわらず、MS3-0は動作し

ます。さらに、SDRAMにマッピングされているMS3-0も、SDRAMアクセスがアクティブでなくても動作

することがあります。マルチプロセッサ・システムにおいては、MS3-0線はバス・マスターによって出力

されます。

RD

I/O/T

メモリ読み出しストローブ。

ADSP-21065Lが、外部メモリ・デバイスや他のADSP-21065LのIOPレジスタ

から読み出しを行うときに使われます。

(他のADSP-21065Lを含めて)外部デバイスは、ADSP-21065Lの

IOPレジスタから読み出すときは、

RDを使用しなければなりません。マルチプロセッサ・システムでは、

RDはバス・マスターによって出力され、他のADSP-21065Lによって入力されます。

WR

I/O/T

メモリ書き込みストローブ。

ADSP-21065Lが、外部メモリ・デバイスや他のADSP-21065LのIOPレジスタ

に書き込みを行うときに使われます。外部デバイスがADSP-21065LのIOPレジスタに書き込むときは、

WRを使用しなければなりません。マルチプロセッサ・システムでは、WRはバス・マスターによって出

力され、他のADSP-21065Lによって入力されます。

SW

I/O/T

同期書き込みセレクト。ADSP-21065Lが(他のADSP-21065Lも含めて)同期式メモリ・デバイスとイン

ターフェースするのに使われます。ADSP-21065Lは、差し迫った書き込みサイクルを早期に知らせる

ためにSWを使用します。この書き込みは、

(例えば、条件付き書き込み命令等で)WRが後で与えられな

ければ中止されます。マルチプロセッサ・システムでは、SWはバス・マスターによって出力され、他の

ADSP-21065Lによって入力され、マルチ・プロセッサ・アクセスが読み出しか書き込みかを決定します。

SWはアドレス出力と同時に出力されます。

ACK

I/O/S

SBTS

I/S

IRQ2-0

FLAG11-0

I/A

I/O/A

メモリ・アクノレッジ。外部デバイスはACKをローにすることで、外部メモリ・アクセスにウエイトを

加えることができます。ACKは、I/Oデバイスやメモリ・コントローラ、その他の周辺素子等が外部メ

モリ・アクセスを遅らせるために使われます。ADSP-21065Lは、IOPレジスタの同期アクセスにウエイ

トを加えるためにACKをローにします。マルチプロセッサ・システムでは、スレーブのADSP-21065Lは

バス・マスターのACK入力をローにして、

そのIOPレジスタのアクセスにウエイトを挿入します。バス・

マスターはACKピンにキーパー・ラッチを持ち、最後に与えられた入力レベルを保ちます。

延長バス・スリーステート。外部デバイスはSBTSをローにすることで、外部バス・アドレス、データ、

セレクト信号、各ストローブ(ただしSDRAM コントロール・ピンは除く)を次のサイクルまでハ

イ・インピーダンス状態に保ちます。もし、A D S P - 2 1 0 6 5 L がS B T S 使用時に外部メモリにア

クセスしようとすると、プロセッサはSBTSが解除されるまで停止し、メモリ・アクセスは終了しませ

ん。SBTSは、ホスト・プロセッサ/ADSP-21065Lのデッドロックからの復帰にのみ使用してください。

割込み要求ライン。エッジ検出でもレベル検出でも使えます。

フラッグ・ピン。各ピンはコントロール・ビットを介して、入力にも出力にも設定できます。入力

としては、

条件判断の条件として使用できます。

出力としては、

外部周辺素子への信号として使えます。

REV.A

−7−

ADSP-21065L

ピン

タイプ

機能

HBR

I/A

ホスト・バス・リクエスト。ADSP-21065Lの外部バスのコントロールを要求するために、ホストから

与えられます。マルチプロセッシング・システムでHBRが与えられると、バス・マスターのADSP-2

1065Lはバスを放棄してHBGを出力します。バスを放棄するために、ADSP-21065Lはアドレス、デー

タ、セレクト、ストローブをハイ・インピーダンス状態にしますが、SDRAMコントロール・ピンはド

ライブし続けます。マルチプロセッサ・システムでは、HBRはすべてのADSP-21065Lのバス・リクエ

スト(BR2-1)に優先します。

HBG

I/O

ホスト・バス・グラント。HBRバス・リクエストを承認して、ホスト・プロセッサが外部バスをコ

ントロールできることを示します。HBGは、HBRが解除されるまでADSP-21065Lによって出力され

ます。マルチプロセッサ・システムにおいては、HBGはADSP-21065Lバス・マスターによって出力さ

れます。

CS

I/A

チップ・セレクト。ADSP-21065Lを選択するために、ホスト・プロセッサによって使われます。

REDY(O/D)

O

ホスト・バス・アクノレッジ。ADSP-21065LはREDYをローにすることで、内部メモリやIOPレジスタ

へのホストによる非同期アクセスにウエイトを挿入します。初期設定ではオープン・ドレイン(O/

D)出力で、SYSCONレジスタのADREDYビットでアクティブ・ドライブ(A/D)にもプログラミング

できます。REDYは、CSとHBRの入力時のみ出力されます。

DMAR1

I/A

DMAリクエスト1(DMAチャンネル9用)。

DMAR2

I/A

DMAリクエスト2(DMAチャンネル8用)。

DMAG1

O/T

DMAグラント1(DMAチャンネル9用)。

DMAG2

O/T

DMAグラント2(DMAチャンネル8用)。

BR2-1

I/O/S

マルチプロセッシング・バス・リクエスト。マルチプロセッシングADSP-21065Lで、バスのマスター

シップの調停に使われます。各ADSP-21065Lは自分のBRx線(各ID2-0入力の値に対応したもの)のみ

を出力し、その他の線はモニターしています。プロセッサ1個のシステムでは両方のBRxピンをVDD

に接続してください。

ID1-0

I

マルチプロセッシングID。どのマルチプロセッサ・バス・リクエスト(BR 1−BR 2)がADSP-21065

Lによって使われるかを定義します。ID=01がBR1に対応し、ID=10がBR2に対応します。単一プロセッ

サ・システムでは、ID=00です。この線はシステム構成時に選択され、固定してしまうか、リセット

時にのみ変更します。

CPA(O/D)

I/O

コア優先アクセス。CPAピンを出力することで、ADSP-21065Lバス・スレーブのコア・プロセッサは

バックグランドDMA転送に割込みをかけ、外部バスにアクセスできます。CPAはオープン・ドレイン

出力で、

システム中の両方のADSP-21065Lの線と繋がれます。

CPAピンは5 kΩのプルアップ抵抗を内

蔵しています。コア優先アクセスを必要としないシステムでは、

CPAピンは開放状態にしておきます。

DTxX

O

データ送信。

(シリアル・ポート0、1;チャンネルA、B)。各DTxXピンは内部に50 kΩのプルアップ

抵抗を持っています。

DRxX

I

データ受信。

(シリアル・ポート0、1;チャンネルA、B)。各DRxXピンは内部に50 kΩのプルアップ

抵抗を持っています。

TCLKx

I/O

送信クロック。

(シリアル・ポート0、1)。各TCLKピンは内部に50 kΩのプルアップ抵抗を持ってい

ます。

RCLKx

I/O

受信クロック。

(シリアル・ポート0、1)。各RCLKピンは内部に50 kΩのプルアップ抵抗を持ってい

ます。

TFSx

I/O

送信フレーム同期。

(シリアル・ポート0、1)。

RFSx

I/O

受信フレーム同期。

(シリアル・ポート0、1)。

BSEL

I

EPROMブート・セレクト。BSELがハイのときは、

ADSP-21065Lは8ビットのEPROMからブートするよ

うに構成されます。

BSELがローのときは、BSELとBMS入力でブート・モードが決まります。詳しくは

BMSの欄を参照してください。この信号はシステム構成の選択ですので、固定しておいてください。

−8−

REV.A

ADSP-21065L

ピン

タイプ

機能

BMS

I/O/T*

ブート・メモリ・セレクト。出力:(BSEL=1のとき)ブートEPROMデバイスのチップ・セレクト

として使用されます。マルチプロセッサ・システムにおいては、BMSはバス・マスターによって出力

されます。入力:ローのとき、ブートが発生しないことを示し、ADSP-21065Lは外部メモリからの実

行命令を開始します。後掲の表を参照してください。この入力はシステム構成の選択ですので、固定

しておいてください。

*EPROMブート・モード(BMSが出力)時にのみスリー・ステートにできます。

BSEL BMS

CLKIN

I

ブート・モード

1

出力

EPROM(BMSはEPROMのチップ・セレクトに接続)

0

(

1 入力)

ホスト・プロセッサ(HBW[SYSCON]ビットでホストのバス幅を選択)

0

(

0 入力)

ブート無し。プロセッサは外部メモリから実行。

クロック入力。XTALピンと一緒に使用され、ADSP-21065Lが内部クロック・ジェネレータを使う

か外部クロック源を使うかを設定します。外部クリスタルは1xレートの周波数のものを使います。

必要な部品をCLKINとXTALに接続すると、内部クロック・ジェネレータがイネーブルになります。A

DSP-21065Lの内部クロック・ジェネレータは1xクロックを倍にして、コアやSDRAMのために2xク

ロックを生成します。2xクロックは、SDRAMインターフェースで使えるようにSDCLKxピンから

出力されます。

SDCLKxも参照してください。

1x外部クロックをCLKINに接続してXTALは開放状態にしておくと、ADSP-21065Lは外部クロック

源を使う構成になります。命令サイクル・レートは2x CLKINに等しくなります。CLKINは停止した

り、変更したり、規定周波数以下で動作させたりしないでください。

RESET

I/A

プロセッサ・リセット。ADSP-21065Lを初期状態にリセットし、ハードウエア・リセット・ベクト

ル・アドレスからプログラムの実行を開始します。電源投入時にはリセットをローにしなければな

りません。

TCK

I

テスト・クロック(JTAG)。JTAG境界スキャンのための非同期クロックを供給します。

TMS

I/S

テスト・モード・セレクト(JTAG)。テスト状態の機械のコントロールに使われます。TMSは内部

に20 kΩのプルアップ抵抗を持っています。

TDI

I/S

テスト・データ入力(JTAG)。境界スキャン・ロジックのためのシリアル・データを供給します。 T

DIは内部に20 kΩのプルアップ抵抗を持っています。

TDO

O

テスト・データ出力(JTAG)。境界スキャン・パスのシリアル・スキャン出力です。

TRST

I/A

テスト・リセット(JTAG)。テスト状態の機械をリセットします。TRSTは、ADSP-21065Lの正常動作

のためには電源投入後にローにするか、最初からローに保っておかなければなりません。TRSTは内

部に20 kΩのプルアップ抵抗を持っています。

EMU(O/D)

O

エミュレーション・ステータス。ADSP-21065L EZ-ICEのターゲット・ボード・コネクタだけに接続

します。

BMSTR

O

バス・マスター出力。マルチプロセッサ・システムにおいて、このADSP-21065Lが現在、共有外部バス

のバス・マスターであるかどうかを示します。

ADSP-21065Lは自分がバス・マスターの間のみBMSTRを

ハイにドライブします。単一プロセッサ・システム(ID=00)では、そのプロセッサがこのピンをハイ

にドライブします。

CAS

I/O/T

SDRAM列アクセス・ストローブ。列アドレスを提供します。RAS、MSx、SDWE、SDCLKxおよび、たま

にSDA10と一緒に、SDRAMの操作を規定します。

RAS

I/O/T

SDRAM行アクセス・ストローブ。行アドレスを提供します。CAS、MSx、SDWE、SDCLKxおよび、たま

にSDA10と一緒に、SDRAMの操作を規定します。

SDWE

I/O/T

SDRAM書き込みイネーブル。CAS、RAS、MSx、SDCLKxおよび、たまにSDA10と一緒に、SDRAMの操

作を規定します。

DQM

O/T

SDRAMデータ・マスク。書き込みモードで、DQMはレテンシーがゼロであり、書き込み操作をブ

ロックするのに使われます。

SDCLK1-0

I/O/S/T

SDRAM 2x クロック出力。複数のSDRAMデバイスが並列に接続されているシステムで、増加する

クロック負荷要求をサポートし、

外部クロック・バッファを使わずにすみます。SDCLK1または両方の

SDCLKxピンをスリーステートにできます。

SDCKE

I/O/T

SDRAM クロック・イネーブル。CLK信号をイネーブルやディスエーブルにします。詳細については、

使用するSDRAMデバイスのデータシートを参照してください。

REV.A

−9−

ADSP-21065L

ピン

タイプ

機能

SDA10

O/T

SDRAM A10ピン。ホスト・アクセスに並行したSDRAMをリフレッシュするアプリケーションを、

XTAL

O

イネーブルにします。

クリスタル・オシレータ端子。CLKINと一緒に使用して、ADSP-21065Lの内部クロック・ジェネレー

タをイネーブルにしたり、外部クロック源を使うためにディスエーブルにしたりします。CLKINを

参照してください。

PWM_EVENT1-0

PWM出力/イベント・キャプチャ。PWMOUTモードでは出力ピンとなり、タイマーカウンタとし

I/O/A

て機能します。WIDTH_CNTモードでは入力ピンとなり、パルス・カウンタ/イベント・キャプ

チャとして機能します。

VDD

P

電源ピン。通常はDC+3.3 Vを与えます(33ピン)。

GND

G

グラウンド・ピン。

(37ピン)。

接続禁止。接続せず開放状態にしておかなければいけないピンです(7)。

NC

クロック信号

EZ-ICEプローブ用ターゲット・ボード・コネクタ

ADSP-21065Lは外部クロックやクリスタルを使用できます。

ADSP-2106x EZ-ICEエミュレータは、エミュレーションの間、

CLKINピンの項を参照してください。必要な部品をCLKINとXTAL

ターゲット・ボードのプロセッサを監視・制御するために、ADSP-

ピンに接続すると、

ADSP-21065Lを内部クロック・ジェネレータを

2106xのIEEE1149.1 JTAGテスト・アクセス・ポートを使います。

使う構成にできます。

クリスタルは基本周波数モードでも、倍音で

EZ-ICEのプローブは、図6に示すような14ピン・コネクタ(2行×7

も動作させることができます。図4は基本周波数モードのクリスタ

ピン・ストリップ・ヘッダ)を介してターゲット・システム上の

ルのための部品接続を示し、

図5は倍音で動作させるクリスタルの

ADSP-2106xのCLKIN、TMS、TCK、TRST、TDI、TDO、EMUおよ

ための部品接続を示します。

びGND信号にアクセスします。

EZ-ICEプローブをこのコネクタに

直接結合することでボード上のチップのエミュレーションを行い

CLKIN

ます。ADSP-2106x EZ-ICEを使いたい場合は、ターゲット・ボード

XTAL

の設計時に、このコネクタを付けておかなければなりません。

×1

動作を保証するために、

EZ-ICEコネクタと、EZ-ICE JTAGピンを

共有しているデバイスで最も離れているものとの間の合計のト

C2

C1

レース長は、最大でも15インチ以内にしてください。この長さの制

限には、複数の2106xや、チェーン上につながった2106xと他の

30MHz動作用の推奨部品

ECLIPTEK EC2SM-33-30.000M (SURFACE MOUNT PACKAGE)

ECLIPTEK EC-33-30.000M (THRU-HOLE PACKAGE)

C1 = 33pF

C2 = 27pF

注: C1、C2はX1のクリスタル専用です。

詳細は水晶メーカーにお問い合わせください。

なければなりません。

14ピンで2列のピン・ストリップ・ヘッダはピン3で向きを示し

ます。ピン3はヘッダから取り除いておいてください。ピンは0.025

図4.30 MHz動作(基本周波数モード・クリスタル)

CLKIN

JTAGデバイスとの組み合わせを通るEZ-ICE JTAGピン信号を含め

インチ角で0.20インチ以上の長さが必要です。ピン間の隙間は0.1

×0.1インチです。ピン・ストリップ・ヘッダは3 MやMcKenzie、

Samtec等のメーカーで扱っています。

XTAL

RS

×1

C3

C1

1

2

3

4

5

6

7

8

9

10

GND

C2

EMU

L1

KEY (NO PIN)

30MHz動作用の推奨部品

ECLIPTEK EC2SM-T-30.000M (SURFACE MOUNT PACKAGE)

ECLIPTEK ECT-30.000M (THRU-HOLE PACKAGE)

C1 = 18pF

C2 = 27pF

C3 = 75pF

L1 = 3300nH

RS = SEE NOTE.

注: C1、C2、C3、L1はX1のクリスタル専用です。

詳細は水晶メーカーにお問い合わせください。

CLKIN (オプション)

BTMS

TMS

BTCK

TCK

9

BTRST

図5.30 MHz動作(3倍音クリスタル)

TRST

11

12

13

14

BTDI

TDI

GND

TDO

上面図

図6.ADSP-2106x EZ-ICE用ターゲット・ボード・

コネクタ(JTAGヘッダ)

− 10 −

REV.A

ADSP-21065L

BTMS、BTCK、BTRSTおよびBTDI信号が供給されるので、テス

CLKINをEZ-ICEヘッダのピン4に接続するのはオプションです。

ト・アクセス・ポートはボード・レベルのテストにも使用できま

エミュレータは、2つのADSP-21065Lを同期させて操作するとき、

す。コネクタがエミュレーションのために使用されていない場合

例えばスタート、ストップ、シングル・ステップ等の操作時にの

は、Bxxxピンとxxxピンをジャンパー線で結んでください。ボード

み、CLKIN信号を使用します。2つのプロセッサが同期してこれら

のテストにテスト・アクセス・ポートを使用しないときは、BTRST

の動作をする必要がなければ、EZ-ICEヘッダのピン4は単にグラウ

をGNDに繋ぎ、BTCKをVDDに接続またはプルアップしてくださ

ンドに繋げておいてください。

い。ADSP-2106xを正しく動作させるため、TRSTピンは電源投入後

内部クロック・ジェネレータと外部の別個のクリスタルを使う

は(コネクタのBTRSTを介して)ローに落とすか、最初からローに

システムでは、CLKINピンを直接JTAGプローブに接続しないでく

しておいてください。どのBxxxピン(ピン5、7、9、11)も、EZ-ICE

ださい。接続してしまうとオシレータ回路に負荷を与え、発振がで

プローブには接続しません。

きなくなることがあります。JTAGプローブのかわりに、CLKINは

JTAG信号はEZ-ICEプローブ上で、以下のように終端されます。

高インピーダンス・バッファを介したXTALピンによってドライブ

することができます。

信号

もし同期マルチプロセッサ動作が必要でCLKINが接続されてい

終端

TMS

22Ωの抵抗を通してドライブされる(16 mAドライバ)

TCK

22Ωの抵抗を通して10 MHzでドライブされる(16 mA

ドライバ)

TRST*

のクロックのズレは最小でなければなりません。ズレが大きすぎ

ると、

プロセッサ間の同期動作が1サイクルずれることがあります。

同期マルチプロセッサ動作では、TCK、TMS、CLKINおよびEMU

22Ωの抵抗を通してドライブされる(16 mAドライバ)

(内部20 kΩ抵抗でプルアップ)

はズレに対して厳密な信号として扱い、

ボード上では配線ができる

限り短くなるように設計してください。

TDI

22Ωの抵抗によってドライブされる(16 mAドライバ)

TDO

1TTL負荷、分割終端(160/220)

CLKIN

1TTL負荷、分割終端(160/220)

もし、同期マルチプロセッサ動作が必要でない(すな わち、

CLKINを接続しない)場合は、TCKとTMSに適当な並列終端をし

てください。TDI、TDO、EMU、TRSTは、ズレに関してはあまり厳

密でない信号です。

(注意:内部XTALオシレータを使うときは、CLKIN

SHARC EZ-ICEに関しての完全な情報は、ADSP-21000ファミ

に接続しないこと)

EMU

ると、複数のADSP-2106xプロセッサとEZ-ICEヘッダのCLKINピン

リー JTAG EZ-ICE ユーザーズ・ガイドおよびリファレンスを参照

アクティブ・ロー4.7 kΩプルアップ抵抗。1TTL負荷

してください。

(ADSP-2106xからオープン・ドレイン出力)

* TRSTは、ソフトウエアの立ち上げ時にエミュレータによってEZ-ICEプローブがオンに

なるまで、ローでドライブされます。ソフトウエアが立ち上がった後、TRSTはハイにド

ライブされます。

REV.A

− 11 −

ADSP-21065L―仕様

推奨動作条件

Cグレード

パラメータ

テスト条件

Kグレード

Min

Max

Min

Max

単位

3.13

3.60

3.13

3.60

V

+85*

℃

VDD

電源電圧

TCASE

ケース動作温度

−40

+100

0

VIH

ハイレベル入力電圧

@VDD=max

2.0

VDD+0.5

2.0

VIL1

ローレベル入力電圧1

@VDD=min

−0.5

0.8

VIL2

ローレベル入力電圧2

@VDD=min

−0.5

0.7

VDD+0.5

V

−0.5

0.8

V

−0.5

0.7

V

注

温度規定に関しては「環境条件」を参照してください。

電気特性

C、Kグレード

パラメータ

VOH

テスト条件

ハイレベル出力電圧

3

3

VOL

ローレベル出力電圧

IIH

ハイレベル入力電流5

IIL

ローレベル入力電流

5

ローレベル入力電流

6

IILP

@V DD=min、IOH=−2.0 mA

@V DD=min、IOL=4.0 mA

7、8、9、10

4

Max

単位

2.4

4

V

0.4

V

@VDD=max、VIN=VDD max

10

μA

@V DD=max、VIN=0 V

10

μA

@V DD=max、VIN=0 V

150

μA

@VDD=max、VIN=VDD max

10

μA

IOZL

スリーステート・リーク電流

7

@V DD=max、VIN=0 V

8

μA

IOZLS

スリーステート・リーク電流8

@V DD=max、VIN=0 V

150

μA

IOZLA

スリーステート・リーク電流11

IOZH

IOZLAR

IOZLC

CIN

スリーステート・リーク電流

Min

@V DD=max、VIN=0 V

350

μA

10

@VDD=max、VIN=1.5 V

4

mA

9

@V DD=max、VIN=0 V

1.5

mA

fIN=1 MHz、TCASE=25℃、

VIN=2.5 V

8

pF

スリーステート・リーク電流

スリーステート・リーク電流

入力容量

12, 13

注

1 入力、および両方向ピンに適用:DATA31-0、ADDR23-0、BSEL、RD、WR、SW、ACK、SBTS、IRQ2-0、FLAG11-0、HBG、CS、DMAR1、DMAR2、BR2-1、ID2-0 、RPBA、CPA、TFS0、TFS1、RFS0、

RFS1、BMS、TMS、TDI、TCK、HBR、DR0A、DR1A、DR0B、DR1B、TCLK0、TCLK1、RCLK0、RCLK1、RESET、TRST、PWM_EVENT0、PWM_EVENT1、RAS、CAS、SDWE、SDCKE。

2 入力ピンCLKINに適用。

3 出力、および両方向ピンに適用:DATA 31-0、ADDR23-0、MS3-0、RD、WR、SW、ACK、FLAG11-0、HBG、REDY、DMAG1、DMAG2、BR2-1、CPA、TCLK0、TCLK1、RCLK0、RCLK1、TFS0、TFS1、

RFS0、RFS1、DT0A、DT1A、DT0B、DT1B、XTAL、BMS、TDO、EMU、BMSTR、PWM_EVENT0、PWM_EVENT1、RAS、CAS、DQM、SDWE、SDCLK0、SDCLK1、SDCKE、SDA10。

4 代表的なドライブ電流能力については「出力ドライブ電流」を参照してください。

5 入力ピンに適用:ACK、SBTS、IRQ2-0、HBR、CS、DMAR1、DMAR2、ID1-0、BSEL、CLKIN、RESET、TCK。(ID 1-0=01で他のADSP-2106Xがバスのマスターシップを要求していないときで、

でマルチプロセッサ・システムでのリセット中には、ACKは2 kΩで内部的にプルアップされていることに注意して下さい。)

6 内部プルアップを持った入力ピンに適用:DR0A、DR1A、DR0B、DR1B、TRST、TMS、TDI。

7 スリーステートになるピンに適用:DATA31-0、ADDR23-0、MS3-0 、RD、WR、SW、ACK、FLAG11-0、REDY、HBG、DMAG1、DMAG2、BMS、TDO、RAS、CAS、DQM、SDWE、SDCLK0、

SDCLK1、SDCKE、SDA10およびEMU。

(ID 1-0=01で他のADSP-2106Xがバスのマスターシップを要求していないときで、マルチプロセッサ・システムでのリセット中には、ACKは2 kΩで

内部的にプルアップされていることに注意して下さい。)

8 内部プルアップを持ちスリーステートにできるピンに適用:DT0A、DT1A、DT0B、DT1B、TCLK0、TCLK1、RCLK0、RCLK1。

9 CPAピンに適用。

10 プルアップ時のACKピンに適用。

11 キーパ・ラッチがイネーブル時のACKピンに適用。

12 保証されますがテストされてはいません。

13 すべての信号ピンに適用。

仕様は予告なく変更されることがあります。

絶対最大定格*

保管温度範囲 …………………………………… −65 ∼ +150℃

電源電圧 ………………………………………… −0.3 ∼ +4.6 V

ピン温度(5秒)……………………………………………… +280℃

入力電圧 …………………………………… −0.5 V ∼ VDD+0.5 V

* 絶対最大定格を越えるストレスはデバイスに永久破壊をもたらすことがあります。この

定格はデバイスの単なるストレスの度合であり、基本的な動作あるいは動作の項に示す

他の条件においてこの定格は考慮されていません。デバイスをある項目についての絶対

最大定格の状態に長時間さらすとデバイスの信頼性に影響を与えます。

出力電圧振幅 ……………………………… −0.5 V ∼ VDD+0.5 V

負荷容量 ……………………………………………………

200 pF

バイアスの下の接合温度 …………………………………… 130℃

注意

ESD(静電放電)の影響を受けやすいデバイスです。4000 Vもの高圧の静電気が人体やテスト装置に容易に帯電し、検知さ

れることなく放電されることもあります。このADSP-21065Lには当社独自のESD保護回路が備えられていますが、高エネ

ルギーの静電放電にさらされたデバイスには回復不能な損傷が残ることもあります。したがって、性能低下や機能喪失を

避けるために、適切なESD予防措置をとるようお奨めします。

− 12 −

WARNING!

ESD SENSITIVE DEVICE

REV.A

ADSP-21065L

ADSP-21065Lの電力消費

この仕様はVDDの内部電力部にのみ適用されます。

外部電源電流およびトータルの供給電流の計算については、このデータシートの電力

消費の項を参照してください。電力消費の計測に使われたコードに関する完全な議論については、SHARC電力消費計測 のテクニカル・ノー

トを参照してください。

各仕様は、以下の動作を前提にしています。

表.Ⅱ 内部電流計測

ハイ活動

ロー活動

(IDDINPEAK)

ピーク活動

(IDDINHIGH)

(IDDINLOW)

命令タイプ

マルチ機能

マルチ機能

単機能

命令フェッチ

キャッシュ

内部メモリ

内部メモリ

コア・メモリ・アクセス

サイクル当たり2つ(DMおよびPM)

サイクル当たり1つ(DM)

無し

内部メモリDMA

サイクル当たり1つ

2サイクルに1つ

2サイクルに1つ

動作

特定のアプリケーションでの電力消費を推測するには、以下の式を使ってください。%は、プログラムがその状態にある時間の量を示し

ます。

%PEAK × IDDINPEAK + %HIGH × IDDINHIGH + %LOW × IDDINLOW + %IDLE16 × IDDIDLE16 = 電力消費

表.Ⅲ 内部電流計測方法

パラメータ

IDDINPEAK

IDDINHIGH

1

電源電流(内部)

電源電流(内部)2

3

IDDINLOW

電源電流(内部)

IDDIDLE

電源電流(IDLE)4

IDDIDLE16

5

電源電流(IDLE16)

テスト条件

MAX

単位

tCK = 33 ns, VDD = max

470

mA

tCK = 30 ns, VDD = max

510

mA

tCK = 33 ns, VDD = max

275

mA

tCK = 30 ns, VDD = max

300

mA

tCK = 33 ns, VDD = max

240

mA

tCK = 30 ns, VDD = max

260

mA

tCK = 33 ns, VDD = max

105

mA

tCK = 30 ns, VDD = max

110

mA

VDD = max

20

mA

注

1 IDDINPEAKの計測に使われるテスト・プログラムはプロセッサ動作の最悪の場合で、通常のアプリケーション下ではずっと続けられません。典型的なアプリケーションを用いて行われた実際の

内部電力計測は、仕様値よりも小さくなります。

2 IDDINHIGH はハイ活動コード範囲での合成された平均値です。

3 IDDINLOW はロー活動コード範囲での合成された平均値です

4 IDLEはIDLE命令を実行しているときのADSP-21065Lの状態を示します。

5 IDLE16はIDLE16命令を実行しているときのADSP-21065Lの状態を示します。

タイミング仕様

一般的な注意事項

ADSP-21065Lは、60 MHzおよび66MHz

(プロセッサの命令レート)の2つのグレードを用意しています。以下の仕様は、

30 MHzのCLKIN

周波数(tCK=33.3 ns)を基本にしています。DTを利用して(tCKの有効範囲内の仕様で。下記の「クロック入力」を参照)他のCLKIN周波数

での仕様を求める事ができます。DTとは、実際のCLKIN周期と33.3 nsのCLKIN周期との差です。

すなわち、

DT=(tCK −33.3)/32 です。

必ず記載されたタイミング値を使用し、他のパラメータから加算や減算をして値を算出しないでください。個々のデバイスにおいては

各パラメータを加算したり減算したりして求めた値は意味のある値ですが、データシートに記載されている値は統計値に基づく最悪値で

す。従って、加算や減算によって有効な値を導き出すことはできません。

基準電圧レベルについては、図26「AC計測のための等価デバイス負荷(すべての備品を含む)を参照してください。

REV.A

− 13 −

ADSP-21065L

スイッチング特性は、プロセッサが信号をどのように変化させるかを規定しています。従って、ユーザーがこのタイミングを制御する

ことはできません。プロセッサ周辺の外部回路は、この信号特性と合致するように設計しなければなりません。スイッチング特性とは、与

えられた環境の下でプロセッサがどのように動作するのかを示すものです。スイッチング特性を、プロセッサに接続される(メモリ等の)

デバイスのタイミング特性を保証するために使用することもできます。

タイミング要求は、

例えば読み出し時のデータ入力のように、プロセッサ外部の回路によって制御される信号に対して適用されます。タ

イミング要求は、プロセッサが他のデバイスと正しく動作するのを保証するものです。

(O/D)=オープン・ドレイン

(A/D)=アクティブ・ドライブ

66 MHz

パラメータ

60 MHz

Min

Max

100

Min

Max

33.33

100

単位

クロック入力

タイミング要求:

tCK

CLKIN周期

30.00

tCKL

CLKINのロー幅

7.0

tCKH

CLKINのハイ幅

5.0

tCKRF

CLKINの立上り/立下り(0.4 −2.0 V)

7.0

ns

ns

5.0

ns

3.0

3.0

ns

t CK

CLKIN

t CKH

t CKL

図7.クロック入力

パラメータ

Min

Max

単位

リセット

タイミング要求:

tWRST

tSRST

RESETのローパルス幅 1

CLKINがハイになる前のRESETのセットアップ

2

2 tCK

ns

23.5+24 DT tCK

ns

注

1 電源投入手順が完了した後に適用。電源投入時、プロセッサの内部フェイズ・ロック・ループは、RESETがローでVDD とCLKINが安定だと仮定して、3000 CLKINサイクル以下の時間を必要

とします(外部クロック発振器のスタート・アップ時間を除く)。

2 複数のADSP-2106xがリセットをCLKINに同期させてプログラム・カウンタ(PC)も等しくする時(すなわちSIMDシステム)にのみ必要とされるタイミング。共有バスを用いて(外部ポー

トを通って)通信を行うADSP-2106xのマルチプロセッサ・システムでは必要ありません。なぜなら、バス調停回路はリセット後に自動的に同期するからです。

CLKIN

t SRST

t WRST

RESET

図8.リセット

パラメータ

Min

Max

単位

割込み

タイミング要求:

tSIR

CLKIN ハイまたはローの前のIRQ2-0のセットアップ時間1

tHIR

CLKIN ハイまたはローの前のIRQ2-0のホールド時間 1

tIPW

IRQ2-0のパルス幅

2

11.0+12 DT

ns

0.0+12 DT

2.0+tCK/2

ns

ns

注

1 次のサイクルでのIRQxの認識にのみ必要となります。

2 tSIRとtHIRの要求が合わないときにのみ適用されます。

− 14 −

REV.A

ADSP-21065L

CLKIN

t SIR

t HIR

IRQ2-0

t IPW

図9.割込み

パラメータ

Min

Max

単位

タイマ

タイミング要求:

tSTI

SDCLK ハイの前のタイマー・セットアップ

0.0

ns

tHTI

SDCLK ハイの後のタイマー・ホールド

6.0

ns

スイッチング特性:

tDTEX

SDCLK ハイの後のタイマー遅延

1.0

tHTEX

SDCLK ハイの後のタイマー・ホールド

ns

−5.0

パラメータ

Min

ns

Max

単位

フラッグ

タイミング要求:

SDCLK ハイの前のFLAG11-0入力セットアップ1

tSFI

1

SDCLK ハイの後のFLAG11-0入力ホールド

tHFI

−2.0

ns

6.0

ns

スイッチング特性:

tDFO

SDCLK ハイの後のFLAG11-0出力遅延

tHFO

SDCLK ハイの後のFLAG11-0出力ホールド

−4.0

1.0

ns

ns

tDFOE

SDCLK ハイからFLAG11-0出力イネーブル

−4.0

ns

tDFOD

SDCLK ハイからFLAG11-0出力ディスエーブル

−1.75

ns

注

1 これらのセットアップおよびホールド時間を満たすフラッグ入力は、次の命令サイクルでの条件付き命令に影響します。

SDCLK

t DFOE

t DFO

t HFO

FLAG11–0OUT

FLAG OUTPUT

SDCLK

t SFI

t HFI

FLAG11–0IN

図10.フラッグ

REV.A

− 15 −

t DFO

tDFOD

ADSP-21065L

メモリ読み出し−バス・マスター

メモリ(やメモリ・マップされた周辺素子)への非同期なインターフェースについては、CLKINではなく、こちらの仕様を利用してくだ

さい。この仕様は、ADSP-21065Lがバス・マスターとして外部メモリ空間にアクセスする場合に適用されます。このスイッチング特性は、

バス・マスターの同期リード/ライト・タイミングにも適用されます(後掲の「同期リード/ライト−バス・マスター」を参照)。もし、こ

のタイミング要求が満たされるならば、

同期リード/ライトのタイミングは無視できます

(逆に同期の方のタイミングを満たせば、こちら

のタイミングを無視する事ができます)。ACKピンのタイミング要求は、下記の注に記したように、例外となります。

パラメータ

Min

Max

単位

28.0+32 DT +W

ns

24.0+26 DT +W

ns

タイミング要求:

tDAD

tDRLD

アドレス、セレクト遅延からデータ有効まで1, 2

RD立下がりからデータ有効まで

1

tHDA

アドレス、セレクトからのデータのホールド

tHDRH

RD立上がりからのデータのホールド3

tDAAK

アドレス、セレクトからのACK遅延2, 3

tDSAK

3

0.0

ns

0.0

ns

3

RD立下がりからのACK遅延

24.0+30 DT +W

ns

19.5+24 DT +W

ns

スイッチング特性:

tDRHA

RD立上がりの後のアドレス、セレクトのホールド

−1.0+H

ns

tDARL

アドレス、セレクトからRD立下がりまで2

3.0+6 DT

ns

tRW

RDパルス幅

25.0+26 DT+W

ns

tRWR

RD立上がりからWR, RD, の立下がり

4.5+6 DT+HI

ns

tRDGL

RD立ち上がりからDMAGxの立ち下がり

11.0+12 DT+HI

ns

W=(WAITレジスタで規定されるウエイト・ステートの数)×tCK

HI=t CK(もしWAITレジスタで規定されるアドレス・ホールド・サイクルまたはバス・アイドル・サイクルが発生したとき;それ以外ではHI=0)

H=t CK(もしWAITレジスタで規定されるアドレス・ホールド・サイクルが発生したとき;それ以外ではH=0)

注

1 データ遅延/セットアップ:ユーザーはtDAD またはtDRLDまたは同期仕様のtSSDATIを満たさなければなりません。

2 MSx、SW、BMSの立ち下がりエッジで規定されます。

3 ACKは、内部ウエイト・ステート・モードを使う外部メモリ・アクセスではサンプルされません。新しい外部メモリ・アクセスの最初のCLKINサイクルに対し、外部、どちらか、または両

方(内部ウエイト・ステートがゼロの場合は、両方)のウエイト・ステート・モードでは、ACKはtDAAK、tDSAK 、または同期仕様tSACKCによって有効になる必要があります。ウエイト・ステー

ト状態の外部メモリ・アクセスの2番目以後のサイクルに対し、外部、どちらか、または両方(内部ウエイト・ステートが完了した後は、両方)のウエイト・ステート・モードでは、同期仕

様t SACKC、tHACKCが一致しなければなりません。

ADDRESS

MSx , SW

BMS

t DRHA

t RW

t DARL

RD

t HDA

t DRLD

t DAD

t HDRH

DATA

t DSAK

t RWR

t DAAK

ACK

WR

DMAG

t RDGL

図11.メモリ読み出し−バス・マスター

− 16 −

REV.A

ADSP-21065L

メモリ書き込み−バス・マスター

メモリ(やメモリ・マップされた周辺素子)への非同期なインターフェースについては、CLKINではなく、こちらの仕様を利用してくだ

さい。この仕様は、ADSP-21065Lがバス・マスターとして外部メモリ空間にアクセスする場合に適用されます。このスイッチング特性は、

バス・マスターの同期リード/ライトにも適用されます(後掲の「同期リード/ライト−バス・マスター」を参照)

。もし、このタイミン

グ要求が満たされるならば、同期リード/ライトのタイミングは無視できます

(逆に同期の方のタイミングを満たせば、こちらのタイミン

グを無視する事ができます)。ACKピンのタイミング要求は、下記の注に記したように、例外となります。

パラメータ

Min

Max

単位

24.0+30 DT+W

ns

19.5+24 DT+W

ns

タイミング要求:

tDAAK

tDSAK

アドレスからのACK遅延1, 2

1

WRの立下がりからのACK遅延

スイッチング特性:

tDAWH

アドレス、セレクトからWR解除まで2

29.0+31 DT+W

ns

tDAWL

アドレス、セレクトからWRの立下がり2

3.5+6 DT

ns

tWW

WRパルス幅

24.5+25 DT+W

ns

tDDWH

WR立上がりまでのデータのセットアップ

15.5+19 DT+W

ns

tDWHA

WR解除後のアドレス・ホールド

0.0+1 DT+H

tDATRWH

WR解除後のデータ・ディスエーブル3

1.0+1 DT+H

tWWR

WR立上がりからWR, RDの立下がり

4.5+7 DT+H

ns

tWRDGL

WR立ち上がりからDMAGxの立ち下がり

11.0+13 DT+H

ns

tDDWR

WRやRDの立下がりまでのデータ・ディスエーブル

3.5+6 DT+I

ns

tWDE

WR立下がりからデータ・イネーブル

4.5+6 DT

ns

ns

4.0+1 DT+H

ns

W=(WAITレジスタで規定されるウエイト・ステートの数)×tCK

H=tCK(もしWAITレジスタで規定されるアドレス・ホールド・サイクルが発生したとき;それ以外ではH=0)

I=tCK(もしWAITレジスタで規定されるバス・アイドル・サイクルが発生したとき;それ以外ではI=0)

注

1 ACKは、内部ウエイト・ステート・モードを使う外部メモリ・アクセスではサンプルされません。新しい外部メモリ・アクセスの最初のCLKINサイクルに対し、外部、どちらか、または両

方(内部ウエイト・ステートがゼロの場合は、両方)のウエイト・ステート・モードでは、ACKはtDAAK、tDSAK、または同期仕様t SACKCによって有効になる必要があります。ウエイト・ステート

状態の外部メモリ・アクセスの2番目以降のサイクルに対し、外部、どちらか、または両方(内部ウエイト・ステートが完了した後は、両方)のウエイト・ステート・モードでは、同期仕様

tSACKC、tHACKCが一致しなければなりません。

2 MSx、SW、BMSの立ち下がりエッジで規定されます。

3 与えられた容量性負荷およびDC負荷におけるホールド時間の計算には、

「テスト条件」の「システム・ホールド時間の計算」を参照してください。

ADDRESS

MSx , SW

BMS

t DWHA

t DAWH

t WW

t DAWL

WR

t WWR

t DDWH

t WDE

t DATRWH

t DDWR

DATA

t DSAK

t DAAK

ACK

RD

DMAG

t WRDGL

図12.メモリ書き込み−バス・マスター

REV.A

− 17 −

ADSP-21065L

同期リード/ライト−バス・マスター

CLKINと関連したタイミングが必要な外部メモリ・システムへのインターフェースや、

(マルチプロセッサ・メモリ空間で)スレーブの

ADSP-2106Xへのアクセスには、この仕様を使用してください。この同期スイッチング特性は、非同期のメモリ読み出しや書き込みにも有

効です(「メモリ読み出し−バス・マスター」、

「メモリ書き込み−バス・マスター」を参照)。

スレーブのADSP-21065Lにアクセスする場合、

スイッチング特性はスレーブの同期リード/ライトのタイミングを満足しなければなり

ません(「同期リード/ライト−バス・スレーブ」を参照)。スレーブのADSP-21065Lの方は、データとアクノレッジのセットアップやホー

ルド時間のための(バス・マスターの)タイミング要求を満足しなければなりません。

パラメータ

Min

Max

単位

タイミング要求:

tSSDATI

CLKINまでのデータのセットアップ

tHSDATI

CLKINの後のデータのホールド

tDAAK

0.25+2 DT

ns

4.0−2 DT

ns

1, 2

アドレス、MSx、SW、BMSの後のACK遅延

tSACKC

CLKINまでのACKセットアップ

tHACK

CLKIN後のACKホールド

1

24.0+30 DT+W

ns

2.75+4 DT

ns

2.0−4 DT

ns

スイッチング特性:

tDADRO

CLKINの後のアドレス、MSx、BMS、SW遅延1

tHADRO

CLKINの後のアドレス、MSx、BMS、SWホールド

7.0−2 DT

0.5−2 DT

ns

ns

tDRDO

CLKINの後のRD立上がり遅延

0.5−2 DT

6.0−2 DT

ns

tDWRO

CLKINの後のWR立上がり遅延

0.0−3 DT

6.0−3 DT

ns

tDRWL

CLKINの後のRD/WR立下がり遅延

7.5+4 DT

11.75+4 DT

ns

tDDATO

CLKINの後のデータ遅延

22.0+10 DT

ns

7.0−2 DT

ns

3.0

ns

tDATTR

CLKINの後のデータ・ディスエーブル

tDBM

CLKINの後のBMSTR遅延

tHBM

CLKINの後のBMSTRホールド

3

1.0−2 DT

−4.0

ns

W=(WAITレジスタで規定されるウエイト・ステートの数)×tCK

注

1 データ・ホールド:ユーザーはtHDA またはtHDRHまたは同期仕様のtHDATIを満たさなければなりません。与えられた容量性負荷およびDC負荷におけるホールド時間の計算には、

「テスト条件」

の「システム・ホールド時間の計算」を参照してください。

2 ACKは、内部ウエイト・ステート・モードを使う外部メモリ・アクセスではサンプルされません。新しい外部メモリ・アクセスの最初のCLKINサイクルに対し、外部、どちらか、または両

方(内部ウエイト・ステートがゼロの場合は、両方)のウエイト・ステート・モードでは、ACKはtDAAK、tDSAK または同期仕様tSACKCによって有効になる必要があります。ウエイト・ステート

状態の外部メモリ・アクセスの2番目以降のサイクルに対し、外部、どちらか、または両方(内部ウエイト・ステートが完了した後は、両方)のウエイト・ステート・モードでは、同期仕様

tSACKC、tHACKCが一致しなければなりません。

3 与えられた容量性負荷およびDC負荷におけるホールド時間の計算には、

「テスト条件」の「システム・ホールド時間の計算」を参照してください。

− 18 −

REV.A

ADSP-21065L

CLKIN

t HADRO

t DAAK

t DADRO

ADDRESS

SW

t HACKC

t SACKC

ACK

(IN)

読み出しサイクル

t DRWL

t DRDO

RD

t HSDATI

t SSDATI

DATA

(IN)

書き込みサイクル

t DWRO

t DRWL

WR

t DATTR

t DDATO

DATA

(OUT)

図13.同期リード/ライト−バス・マスター

REV.A

− 19 −

ADSP-21065L

同期リード/ライト−バス・スレーブ

ADSP-21065Lバス・マスターによる、スレーブのIOPレジスタや(マルチプロセッサ・メモリ空間の)内部メモリへのアクセスには、こ

の仕様を使用してください。バス・マスターは、この(バス・スレーブ)タイミング要求を満足しなければなりません。

パラメータ

Min

Max

単位

タイミング要求:

tSADRI

CLKINまでのアドレス、SWのセットアップ

tHADRI

CLKINまでのアドレス、SWのホールド

tSRWLI

CLKINまでのRD/WRローのセットアップ1

21.0+21 DT

tHRWLI

CLKINの後のRD/WRローのホールド

−2.50−5 DT

tRWHPI

RD/WRパルスハイ

2.5

ns

tSDATWH

WR立上がりまでのデータ・セットアップ

4.5

ns

tHDATWH

WR立上がりの後のデータ・ホールド

0.0

ns

24.5+25 DT

ns

4.0+8 DT

ns

ns

7.5+7 DT

ns

スイッチング特性:

tSDDATO

CLKIN後のデータ遅延

tDATTR

CLKIN後のデータ・ディスエーブル2

tDACK

CLKIN後のACK遅延

tACKTR

CLKIN後のACKディスエーブル2

31.75+21 DT

1.0−2 DT

1.0−2 DT

ns

7.0−2 DT

ns

29.5+20 DT

ns

6.0−2 DT

ns

注

1 マルチプロセッサ・メモリ空間ウエイト・ステート(WAITレジスタのMMSWSビット)がディスエーブルのとき、tSRWLIが規定されます。MMSWSがイネーブルのときはtSRWLI(min)=17.5+

18DT。

2 与えられた容量性負荷およびDC負荷におけるホールド時間の計算には、

「テスト条件」の「システム・ホールド時間の計算」を参照してください。

マスターおよびスレーブとして二つのADSP-21065Lが同期を取って通信するためには、

一定のマスターおよびスレーブの仕様の組み合

わせが満足されなければなりません。

マスター/スレーブのクロック・スキューのマージンを計算するために、下のリストの仕様値を直接

比較することはしないでください。次の表は適切なクロック・スキューのマージンを示しています。

表Ⅳ.バス・マスターとスレーブのスキュー・マージン

マスターの仕様

スレーブの仕様

スキュー・マージン

tSSDATI

tSDDATO

tCK=33.3 ns

tCK=30.0 ns

+2.25 ns

+1.50 ns

tSACKC

tDACK

tCK=33.3 ns

tCK=30.0 ns

+3.00 ns

+2.25 ns

tDADRO

tSADRI

tCK=33.0 ns

tCK=30.0 ns

N/A

+2.75 ns

tDRWL(Max)

t SRWLI

tCK=33.3 ns

tCK=30.0 ns

+1.50 ns

+1.25 ns

(Max)

tDRDO

t HRWLI

(Max)

tCK=33.3 ns

tCK=30.0 ns

N/A

3.00 ns

tDWRO(Max)

t HRWLI

(Max)

tCK=33.3 ns

tCK=30.0 ns

N/A

3.75 ns

− 20 −

REV.A

ADSP-21065L

CLKIN

t SADRI

t HADRI

ADDRESS

SW

t DACK

t ACKTR

ACK

読み出しアクセス

t SRWLI

t HRWLI

t RWHPI

RD

t SDDATO

t DATTR

DATA

(OUT)

書き込みアクセス

t SRWLI

t HRWLI

WR

t SDATWH

DATA

(IN)

図14.同期リード/ライト−バス・スレーブ

REV.A

− 21 −

t HDATWH

t RWHPI

ADSP-21065L

マルチプロセッサ・バス・リクエストとホスト・バス・リクエスト

この仕様は、バスのマスターシップをマルチプロセッシングADSP-21065L(BRx)やホスト・プロセッサ(HBR、HBG)で受け渡すとき

に使用してください。

パラメータ

Min

Max

単位

タイミング要求:

tHBGRCSV

HBG立下がりからRD/WR/CS有効1

tSHBRI

CLKINまでのHBRセットアップ2

tHHBRI

CLKINまでのHBRホールド2

tSHBGI

CLKINまでのHBGセットアップ

tHHBGI

CLKIN立上がりまでのHBGホールド

20.0+36 DT

12.0+12 DT

6.0+12 DT

6.0+8 DT

3

tSBRI

CLKINまでのBRx、CPAセットアップ

tHBRI

CLKIN立上がりまでのBRx、CPAホールド

ns

ns

ns

ns

1.0+8 DT

ns

1.0+8 DT

ns

8.0−2 DT

ns

7.0+8 DT

ns

スイッチング特性:

tDHBGO

CLKIN後のHBG遅延

tHHBGO

CLKIN後のHBGホールド

tDBRO

CLKIN後のBRx遅延

tHBRO

CLKIN後のBRxホールド

tDCPAO

CLKIN後のCPA立下がり遅延

tTRCPA

CLKIN後のCPAディスエーブル

tDRDYCS

tTRDYHG

tARDYTR

1.0−2 DT

ns

7.0−2 DT

ns

11.5−2 DT

ns

5.5−2 DT

ns

13.0

ns

1.0−2 DT

1.0−2 DT

CSとHBR立下がりからのREDY(O/D)または(A/D)立下がり

4

HBGからのREDY(O/D)ディスエーブルまたはREDY(A/D)立上がり

CSまたはHBR立上がりからのREDY(A/D)ディスエーブル

4

4

ns

44.0+43 DT

ns

10.0

ns

注

1 HBRとCSが与えられた後の最初の非同期アクセスのためには、ADDR23-0は、RDやWRが立下がる1/2t CK前か、またはHBGがローになったtHBGRCSV 後までに、MMSではない値にならなければ

なりません。これはHBGが与えられているときに上位アドレス信号をHIにドライブすることで、簡単に達成できます。ADSP-21065L SHARC ユーザーズ・マニュアル、第2版のADSP21065Lのホスト・プロセッサ・コントロールの項を参照して下さい。

2 現在のサイクル中に認識される必要があるときのみ要求されます。

3 CPAはCLKINへのセットアップを満足するように与えなければなりません。CPAの解除はCLKINへのセットアップを満足する必要はありません。

4 (O/D)はオープン・ドレインを、

(A/D)はアクティブ・ドライブを表します。

− 22 −

REV.A

ADSP-21065L

CLKIN

t SHBRI

t HHBRI

HBR

t HHBGO

t DHBGO

HBG

(OUT)

t DBRO

t HBRO

BRx

(OUT)

t DCPAO

t TRCPA

CPA (OUT)

(O/D)

t SHBGI

t HHBGI

HBG (IN)

t SBRI

t HBRI

BRx (IN)

CPA (IN) (O/D)

HBR

CS

t TRDYHG

t DRDYCS

REDY (O/D)

t ARDYTR

REDY (A/D)

t HBGRCSV

HBG (OUT)

RD

WR

CS

O/D = オープン・ドレイン, A/D = アクティブ・ドライブ

図15.マルチプロセッサ・バス・リクエストとホスト・バス・リクエスト

REV.A

− 23 −

ADSP-21065L

非同期リード/ライト−ホストからADSP-21065L

この仕様は、ホストがCSやHBR(ロー)を出力した後の、ホスト・プロセッサのADSP-21065Lへの非同期アクセスに使用してください。

ADSP-21065LからHBGが返された後、ホストはADSP-21065LのIOPレジスタにアクセスするためにRDおよびWRをドライブすることがで

きます。このタイミングではHBRとHBGはローと仮定されます。書き込み操作は最小(1/2)tCKの間隔で発生できます。

パラメータ

Min

Max

単位

読み出しサイクル

タイミング要求:

tSADRDL

RD立下がりまでのアドレス・セットアップ/CS立ち下がり*

0.0

ns

tHADRDH

RD立ち上がり後のアドレス・ホールド/CSホールド立ち下がり

0.0

ns

tWRWH

RD/WR ハイの幅

6.0

ns

tDRDHRDY

REDY(O/D)ディスエーブル後のRDの立ち上がり遅延

0.0

ns

tDRDHRDY

REDY(A/D)ディスエーブル後のRDの立ち上がり遅延

0.0

ns

1.5

ns

スイッチング特性:

tSDATRDY REDYがローからディスエーブルになるまでのデータ有効

tDRDYRDL RD立下がり後のREDY(O/D)または(A/D)立ち下がり遅延

13.5

tRDYPRD

読み出しのREDY(O/D)または(A/D)ローのパルス幅

28.0+DT

tHDARWH

RD立上がり後のデータ・ディスエーブル

2.0

ns

ns

10.0

ns

書き込みサイクル

タイミング要求:

tSCSWRL

WR立下がりまでのCS ローのセットアップ

0.0

ns

tHCSWRH

WR立上がりの後のCS ローホールド

0.0

ns

tSADWRH

WR立上がりまでのアドレス・セットアップ

5.0

ns

tHADWRH

WR立上がりの後のアドレス・ホールド

2.0

ns

tWWRL

WR ローの幅

7.0

ns

tWRWH

RD/WR ハイの幅

6.0

ns

tDWRHRDY

REDY(O/D)または(A/D)ディスエーブルの後のWR ハイ遅延

0.0

ns

tSDATWH

WR立上がりまでのデータ・セットアップ

5.0

ns

tHDATWH

WR立上がり後のデータ・ホールド

1.0

ns

スイッチング特性:

tDRDYWRL

WR/CS立下がりの後のREDY(O/D)または(A/D)ロー遅延

tRDYPWR

書き込みのREDY(O/D)または(A/D)ローのパルス幅

13.5

7.75

ns

ns

注

* HBGがローになったt HBGRCSV後にRDとアドレスが有効であれば必要でありません。HBRが与えられた後の最初のアクセスでは、ADDR23-0は、RDやWRが立下がる1/2t CLK前か、またはHBG

がローになったtHBGRCSW後までに、MMSではない値にならなければなりません。これは、HBGが与えられたときに上位アドレス信号をHIにドライブすることで容易に達成できます。ADSP21065L SHARCユーザーズ・マニュアル第2版のホスト・インターフェースの項を参照してください。

− 24 −

REV.A

ADSP-21065L

読み出しサイクル

ADDRESS/CS

tHADRDH

tSADRDL

tWRWH

RD

tHDARWH

DATA (OUT)

tSDATRDY

tDRDYRDL

tDRDHRDY

tRDYPRD

REDY (O/D)

REDY (A/D)

書き込みサイクル

ADDRESS

tSADWRH

tSCSWRL

tHADWRH

tHCSWRH

CS

tWWRL

tWRWH

WR

tHDATWH

tSDATWH

DATA (IN)

tDWRHRDY

tDRDYWRL

tRDYPWR

REDY (O/D)

REDY (A/D)

O/D = オープン・ドレイン, A/D = アクティブ・ドライブ

図16.非同期リード/ライト−ホストからADSP-21065L

REV.A

− 25 −

ADSP-21065L

スリーステート・タイミング−バス・マスター、バス・スレーブ、HBR、SBTS

この仕様は、CLKINとSBTSピンとの関連で、どのようにメモリ・インターフェースがディスエーブル(ドライブを停止する)されたり

イネーブル(ドライブを始める)されたりするかを示します。このタイミングはSBTSピンと同様に、バス・マスター遷移サイクル(BTC)

とホスト遷移サイクル(HTC)にも応用できます。

パラメータ

Min

Max

単位

タイミング要求:

tSTSCK

CLKINまでのSBTSセットアップ

tHTSCK

CLKINまでのSBTSホールド

7.0+8 DT

ns

1.0+8 DT

ns

スイッチング特性:

tMIENA

CLKIN後のアドレス/セレクト・イネーブル

1

1.0−2 DT

ns

tMIENS

CLKIN後のストローブ・イネーブル

−0.5−2 DT

ns

tMIENHG

CLKIN後のHBGイネーブル

2.0−2 DT

ns

tMITRA

CLKIN後のアドレス/セレクト・ディスエーブル

tMITRS

CLKIN後のストローブ・ディスエーブル

tMITRHG

CLKIN後のHBGディスエーブル

tDATEN

CLKIN後のデータ・イネーブル

2

tDATTR

CLKIN後のデータ・ディスエーブル

tACKEN

CLKIN後のACKイネーブル2

tACKTR

CLKIN後のACKディスエーブル2

tMTRHBG

tMENHBG

1

3.0−4 DT

ns

4.0−4 DT

ns

5.5−4 DT

ns

10.0+5 DT

2

1.0−2 DT

ns

7.0−2 DT

7.5+4 DT

1.0−2 DT

HBG立下がりまでのメモリ・インターフェース・ディスエーブル

HBG立上がり後のメモリ・インターフェース・イネーブル

3

3

ns

ns

6.0−2 DT

ns

2.0+2 DT

ns

15.75+DT

ns

注

1 ストローブ=RD、WR、SW、DMAG、

2 バス・マスター遷移サイクルに加えて、この仕様はバス・マスターとバス・スレーブの同期リード/ライトにも適用されます。

3 メモリ・インターフェース=アドレス、RD、WR、MSx、SW、DMAGx、BMS(EPROMブート・モード)

− 26 −

REV.A

ADSP-21065L

CLKIN

t STSCK

t HTSCK

SBTS

t MITRA, t MITRS, t MITRHG

t MIENA, t MIENS, t MIENHG

MEMORY

INTERFACE

t DATTR

t DATEN

DATA

t ACKTR

t ACKEN

ACK

HBG

tMTRHBG

t MENHBG

MEMORY

INTERFACE

メモリ・インターフェース = アドレス, RD, WR, MSx, SW, DMAGx. BMS (EPROM ブート・モード)

図17.スリーステート・タイミング

REV.A

− 27 −

ADSP-21065L

DMAハンドシェイク

この仕様は、3つのDMAハンドシェイク・モードについて説明しています。3つのモードすべてで、DMARが転送の開始に使用されます。

ハンドシェイク・モードでは、外部的にデータをラッチしたりイネーブルしたりするのを、DMAGがコントロールします。外部ハンドシェ

イク・モードでは、データ転送はADDR23-0、RD、WR、SW、MS 3-0、ACKおよびDMAG信号によってコントロールされます。外部モードは

SDRAMとの転送には使用できません。ペース・マスター・モードでは、データ転送はADDR23-0、RD、WR、MS3-0、および(DMAGではなく)

ACKによってコントロールされます。ペース・マスター・モードでは「メモリ読み出し−バス・マスター」

、

「メモリ書き込み−バス・マ

スター」

「同期リード/ライト−バス・マスター」のADDR23-0、RD、WR、MS3-0、SW、DATA31-0、ACKのタイミング仕様も適用されます。

パラメータ

Min

Max

単位

タイミング要求:

tSDRLC

CLKINまでのDMARx ローのセットアップ゚1

tSDRHC

CLKINまでのDMARx ハイのセットアップ

tWDR

DMARxローの幅(非同期)

1

5.0

ns

5.0

ns

6.0

ns

2

tSDATDGL

DMAGx立下がり後のデータ・セットアップ

tHDATIDG

DMAGx立上がり後のデータ・ホールド

15.0+20 DT

tDATDRH

DMARx立上がり後のデータ有効2

tDMARLL

DMARx ローエッジからローエッジまで

18.0+14 DT

ns

tDMARH

DMARx ハイの幅

6.0

ns

0.0

ns

ns

25.0+14 DT

ns

スイッチング特性:

tDDGL

CLKIN後のDMAGx ロー遅延

14.0+10 DT

20.0+10 DT

tWDGH

DMAGx ハイの幅

10.0+12 DT+HI

ns

tWDGL

DMAGx ローの幅

16.0+20 DT

ns

tHDGC

CLKIN後のDMAGx ハイ遅延

0.0−2 DT

tDADGH

アドレス・セレクト有効からDMAGx ハイ

28.0+16 DT

tDDGHA

DMAGx 立ち上がり後のアドレス・セレクト・ホールド

−1.0

ns

tVDATDGH

DMAGx立上がりまでのデータ有効3

16.0+20 DT

ns

tDATRDGH

DMAGx立上がり後のデータ・ディスエーブル4

0.0

4.0

ns

tDGWRL

DMAGx立下がりまでのWRロー

5.0+6 DT

8.0+6 DT

ns

tDGWRH

WR立上がりまでのDMAGxロー

18.0+19 DT+W

tDGWRR

DMAGx立上がりまでのWR立上がり

0.75+1 DT

3.0+1 DT

ns

tDGRDL

DMAGx立下がりまでのRD立下がり

5.0

8.0

ns

tDRDGH

DMAGx立上がりまでのRD立下がり

24.0+26 DT+W

tDGRDR

DMAGx立上がりまでのRD立上がり

0.0

tDGWR

DMAGx立上がりからWR, RD立下がり

5.0+6 DT+HI

6.0−2 DT

ns

ns

ns

ns

ns

2.0

ns

ns

W=(WAITレジスタで規定されるウエイト・ステートの数)×tCK

HI=t CK(もしWAITレジスタで規定されるアドレス・ホールド・サイクルまたはバス・アイドル・サイクルが発生したとき;それ以外ではHI=0)

注

1 現在のサイクル中に認識される必要があるときのみ要求されます。

2 tSDATDGLは、書き込みの完了を阻止するためにDMARxが使われない場合のデータ・セットアップ要求です。もしくは、DMARxローで書き込みの完了が阻止される場合には、DMARxがハイ

にされた後、tDATDRHでデータがドライブされます。

3 DMARxが読み出しの完了を阻止するために使用されない場合、tVDATDGHは有効です。もしDMARxが読み出しを延長するために使用された場合は、tVDATDGH=8+9 DT+(n×tCK)で、nはアク

セスが延長される余分なサイクル数に等しい数です。

4 与えられた容量性負荷およびDC負荷におけるホールド時間の計算には、

「テスト条件」の「システム・ホールド時間の計算」を参照してください。

− 28 −

REV.A

ADSP-21065L

CLKIN

t SDRLC

t DMARLL

t SDRHC

t WDR

t DMARH

DMARx

t HDGC

t DDGL

t WDGL

t WDGH

DMAGx

ADSP-2106x内部メモリと外部デバイスとの転送

t VDATDGH

t DATRDGH

DATA (FROM

ADSP-2106x TO

EXTERNAL DEVICE)

t DATDRH

t HDATIDG

t SDATDGL

DATA (FROM

EXTERNAL DEVICE

TO ADSP-2106x)

外部デバイスと外部メモリとの転送*(外部ハンドシェイク・モード)

t DGWRL

WR

(EXTERNAL DEVICE

TO EXTERNAL

MEMORY)

t DGWRH

t DGRDR

t DGRDL

RD

(EXTERNAL

MEMORY TO

EXTERNAL DEVICE)

t DGWRR

t DRDGH

t DADGH

ADDRESS

SW, MSx

* 「メモリ読み出し − バス・マスター」、「メモリ書き込み− バス・マスター」「同期リード/ライト − バス・マスター」の

ADDR23–0, RD, WR, SW, MS3–0, ACKのタイミング仕様も、ここで適用されます。

図18.DMAハンドシェイク・タイミング

REV.A

− 29 −

t DDGHA

ADSP-21065L

SDRAMインターフェース − バス・マスター

ADSP-21065LのSDRAMのバス・マスター・アクセスには、この仕様を使ってください。

パラメータ

Min

Max

単位

タイミング要求:

tSDSDK

SDCLK前のデータ・セットアップ

2.0

ns

tHDSDK

SDCLK後のデータ・ホールド

1.25

ns

スイッチング特性:

tDSDK1

CLKIN後の最初のSDCLK立ち上がり遅延

9.0+6 DT

12.75+6 DT

ns

tDSDK2

CLKIN後の2番目のSDCLK立ち上がり遅延

25.5+22 DT

29.25+22 DT

ns

tSDK

SDCLK周期

16.67

tCK /2

ns

tSDKH

SDCLK ハイの幅

7.5+8 DT

ns

tSDKL

SDCLK ローの幅

6.5+8 DT

ns

tDCADSDK

SDCLK後のコマンド、アドレス、データ・遅延

1

tHCADSDK

SDCLK後のコマンド、アドレス、データ・ホールド

tSDTRSDK

SDCLK後のデータ・スリーステート

10.0+5 DT

1

2

4.5+5 DT

ns

ns

9.5+5 DT

ns

tSDENSDK

SDCLK後のデータ・イネーブル

6.0+5 DT

tSDCTR

CLKIN後のSDCLK、コマンド・スリーステート1

5.0+3 DT

9.75+3 DT

ns

tSDCEN

CLKIN後のSDCLK、コマンド・イネーブル1

5.0+2 DT

10.0+2 DT

ns

tSDATR

CLKIN後のアドレス・スリーステート

−1.0−4 DT

3.0−4 DT

ns

tSDAEN

CLKIN後のアドレス・イネーブル

1.0−2 DT

7.0−2 DT

ns

ns

注

1 コマンド=SDCKE、MSx、RAS、CAS、SDWE、DQM、およびSDA10

2 SDRAMコントローラは、次に書き込みが行われる読み出しにおいて、1 SDRAM CLKスリーステート・サイクル遅延(t CK/2)を加えます。

SDRAMインターフェース−バス・スレーブ

このタイミング要求で、バス・スレーブはバス・マスターのSDRAMコマンドを取り込み、リフレッシュの発生を検出します。

パラメータ

Min

Max

単位

6.50+16 DT

17.5+16 DT

ns

23.25

34.25

ns

タイミング要求:

tSSDKC1

CLKIN後の最初のSDCLK立ち上がり

tSSDKC2

CLKIN後の2番目のSDCLK立ち上がり

tSCSDK

tHCSDK

1

SDCLKの前のコマンド・セットアップ

1

SDCLK後のコマンド・ホールド

0.0

ns

2.0

ns

注

1 コマンド=SDCKE、RAS、CASおよびSDWE

− 30 −

REV.A

ADSP-21065L

CLKIN

t DSDK2

t DSDK1

t SDKH

t SDK

SDCLK

t SDSDK

t SDKL

t HDSDK

DATA

(IN)

t SDTRSDK

t DCADSDK

t SDENSDK

t HCADSDK

DATA

(OUT)

t DCADSDK

CMND1

ADDR

(OUT)

t HCADSDK

t SDCEN

t SDCTR

CMND1

(OUT)

ADDR

(OUT)

t SDAEN

t SDATR

CLKIN

t SSDKC2

t SSDKC1

SDCLK

(IN)

t SCSDK

CMND2

(IN)

t HCSDK

注意

1 コマンド=SDCKE、MSX、RAS、CAS、SDWE、DQM、およびSDA1O。

2 SDRAMコントローラは、次に書き込みが行われる読み出しにおいて、1 SDRAM CLKスリーステート・サイクル遅延(tCK/2)を加えます。

図19.SDRAMインターフェース

REV.A

− 31 −

ADSP-21065L

シリアル・ポート

パラメータ

Min

Max

単位

外部クロック

タイミング要求:

tSFSE

TCLK/RCLKまでのTFS/RFSのセットアップ1

4.0

ns

tHFSE

TCLK/RCLK後のTFS/RFSのホールド1

4.0

ns

tSDRE

RCLKまでの受信データ・セットアップ1

1.5

ns

tHDRE

RCLK後の受信データ・ホールド1

4.0

ns

tSCLKW

TCLK/RCLK幅

9.0

ns

tSCLK

TCLK/RCLK周期

tCK

ns

内部クロック

タイミング要求:

tSFSI

TCLKまでのTFSセットアップ2;RCLKまでのRFSセットアップ1

8.0

ns

tHFSI

TCLK/RCLK後のTFS/RFSホールド1

1.0

ns

tSDRI

RCLKまでの受信データ・セットアップ1

3.0

ns

tHDRI

RCLK後の受信データ・ホールド1

3.0

ns

外部または内部クロック

スイッチング特性:

tDFSE

RCLK後のRFS遅延(内部生成RFS)2

tHOFSE

RCLK後のRFSホールド(内部生成RFS)2

13.0

3.0

ns

ns

外部クロック

スイッチング特性:

tDFSE

TCLK後のTFS遅延(内部生成TFS)2

tHOFSE

TCLK後のTFSホールド(内部生成TFS)2

tDDTE

TCLK後の送信データ遅延2

tHDTE

13.0

3.0

12.5

2

TCLK後の送信データ・ホールド

ns

ns

4.0

ns

ns

内部クロック

スイッチング特性:

tDFSI

TCLK後のTFS遅延(内部生成TFS)2

tHOFSI

TCLK後のTFSホールド(内部生成TFS)2

tDDTI

TCLK後の送信データ遅延2

tHDTI

TCLK後の送信データ・ホールド2

tSCLKIW

TCLK/RCLK幅

4.5

ns

7.5

ns

−1.5

ns

0.0

(tSCLK/2)−2.5

ns

(tSCLK/2)+2.5

ns

イネーブル&スリーステート

スイッチング特性:

tDTENE

tDDTTE

外部TCLKからデータ・イネーブル2

外部RCLKからデータ・ディスエーブル2

5.0

tDTENI

内部TCLKからデータ・イネーブル2

0.0

tDDTTI

内部TCLKからデータ・ディスエーブル2

3.0

ns

tDCLK

CLKINからTCLK/RCLK遅延

18.0+6 DT

ns

tDPTR

CLKIN後のSPORTディスエーブル

14.0

ns

10.0

ns

ns

ns

外部の遅いフレーム同期

tDDTLFSE

MCE=1、MFD=0で遅い外部TFSまたは外部RFSからのデータ遅延3, 4

tDTENLFSE

遅いFSまたはMCE=1、MFD=0からのデータ・イネーブル3, 4

tDDTLSCK

遅い外部TFSのためのTCLK/RCLKまたはMCE=1、MFD=0

10.5

3.5

での外部RFSからのデータ遅延3, 4

tDTENLSCK

ns

ns

12.0

ns

遅い外部FSのためのRCLK/TCLKまたはMCE=1、MFD=0

からのデータイネーブル3, 4

4.5

ns

注

クロック・スピードnで、ふたつのデバイス間の通信が可能かどうかを判断するには、次に挙げる仕様を確認しなければなりません:1)フレーム同期遅延とフレーム同期のセットアップと

ホールド、2)データ遅延とデータのセットアップとホールド、3)SCLK幅。

1 サンプル・エッジからが基準になります。

2 ドライブ・エッジからが基準になります。

3 MCE=1、TFSイネーブルとTFS有効はtDDTLFSEとtDDTENFSに従います。

4 もし外部RFS/TFSセットアップが RCLK/TCLK> tSCLK/2 ならば、tDDTLSCKとt DTENLSCKが適用されます。その他の場合はtDDTLFSEとtDTENLFSが適用されます。

* I2Sモードでワードが選択されるタイミングは、TFS/RFSタイミングと同じです(通常フレーミングのみ)。

− 32 −

REV.A

ADSP-21065L

データ受信−内部クロック

データ受信−外部クロック

SAMPLE

EDGE

DRIVE

EDGE

DRIVE

EDGE

SAMPLE

EDGE

tSCLKIW

tSCLKW

RCLK

RCLK

tDFSE

tHOFSE

tSFSI

tDFSE

tHOFSE

tHFSI

RFS

tSFSE

tHFSE

tSDRE

tHDRE

RFS

tSDRI

tHDRI

DR

DR

注意:RCLK、TCLKの立ち上がり、立ち下がりエッジのいずれかを、アクティブ・サンプリング・エッジとして使えます。

データ送信−内部クロック

データ送信−外部クロック

SAMPLE

EDGE

DRIVE

EDGE

DRIVE

EDGE

SAMPLE

EDGE

tSCLKIW

tSCLKW

TCLK

TCLK

tDFSI

tHOFSI

tSFSI

tDFSE

tHOFSE

tHFSI

TFS

tSFSE

TFS

tHDTI

tDDTI

tHDTE

tDDTE

DT

DT

注意:RCLK、TCLKの立ち上がり、立ち下がりエッジのいずれかを、アクティブ・サンプリング・エッジとして使えます。

DRIVE

EDGE

DRIVE

EDGE

TCLK (EXT)

TFS ("LATE", EXT.)

TCLK / RCLK

tDDTEN

tDDTTE

DT

DRIVE

EDGE

TCLK (INT)

TFS ("LATE", INT.)

DRIVE

EDGE

TCLK / RCLK

tDDTIN

tDDTTI

DT

CLKIN

tDPTR

TCLK, RCLK

TFS, RFS, DT

SPORT DISABLE DELAY

FROM INSTRUCTION

SPORT ENABLE AND

THREE-STATE

LATENCY

IS TWO CYCLES

tDCLK

TCLK (INT)

RCLK (INT)

LOW TO HIGH ONLY

図20.シリアル・ポート

REV.A

− 33 −

tHFSE

ADSP-21065L

外部RFSでMCE=1、MFD=0

DRIVE

DRIVE

SAMPLE

RCLK

tHOFSE/I

tSFSE/I

RFS

tDDTE/I

tHDTE/I

tDTENLFSE

1ST BIT

DT

2ND BIT

tDDTLFSE

遅い外部TFS

DRIVE

DRIVE

SAMPLE

TCLK

tHOFSE/I

tSFSE/I

TFS

tDDTE/I

tHDTE/I

tDTENLFSE

1ST BIT

DT

2ND BIT

tDDTLFSE

図21.外部の遅いフレーム同期(フレーム同期セットアップ<tSCLK/2 )

外部RFSでMCE=1、MFD=0

DRIVE

SAMPLE

DRIVE

RCLK

tHOFSE/I

tSFSE/I

RFS

tDDTE/I

tHDTE/I

tDTENLSCK

DT

1ST BIT

2ND BIT

tDDTLSCK

遅い外部TFS

DRIVE

SAMPLE

DRIVE

TCLK

tHOFSE/I

tSFSE/I

TFS

tDDTE/I

tHDTE/I

tDTENLSCK

DT

1ST BIT

2ND BIT

tDDTLSCK

図22.外部の遅いフレーム同期(フレーム同期セットアップ>tSCLK/2 )

− 34 −

REV.A

ADSP-21065L

JTAGテスト・アクセス・ポートとエミュレーション

パラメータ

Min

Max

単位

タイミング要求:

tTCK

TCK周期

tCK

ns

tSTAP

TCK立上がりまでのTDI, TMSセットアップ

3.0

ns

tHTAP

TCK立上がり後のTDI, TMSホールド

3.0

ns

7.0

ns

12.0

ns

4 tCK

ns

tSSYS

TCK立下がりまでのシステム入力セットアップ

tHSYS

TCK立下がり後のシステム入力ホールド

tTRSTW

TRSTパルス幅

1

1

スイッチング特性:

tDTDO

tDSYS

TCK立下がりからのTDO遅延

TCK立下がり後のシステム出力遅延

2

11.0

ns

15.0

ns

注

1 システム入力=DATA31-0、ADDR23-0、RD、WR、ACK、SBTS、SW、HBR、HBG、CS、DMAR 1、DMAR2、BR2-1、ID 1-0、IRQ 2-0、FLAG11-0、DR0x、DR1x、TCLK0、TCLK1、RCLK0、RCLK1、TFS0、

TFS1、RFS0、RFS1、BSEL、BMS、CLKIN、RESET、SDCLK0、RAS、CAS、SDWE、SDCKE、PWM_EVENTx。

2 システム出力=DATA31-0、ADDR23-0、MS 3-0、RD、WR、ACK、SW、HBG、REDY、DMAG1、DMAG2、BR2-1、CPA、FLAG11-0、PWM_EVENTx、DT0x、DT1x、TCLK0、TCLK1、RCLK0、RCLK1、

TFS0、TFS1、RFS0、RFS1、BMS、SDCLK0、SDCLK1、DQM、SDA10、RAS、CAS、SDWE、SDCKE、BM、XTAL。

t TCK

TCK

t STAP

t HTAP

TMS

TDI

t DTDO

TDO

t SSYS

SYSTEM

INPUTS

t DSYS

SYSTEM

OUTPUTS

図23.JTAGテスト・アクセス・ポートとエミュレーション

REV.A

− 35 −

t HSYS

ADSP-21065L

出力ドライブ電流

システム・ホールド時間の計算の例

特定のシステムにおけるデータ出力ホールド時間を求めるため

には、まず前述の式を使ってtDECAYを計算します。ΔVは、ADSP-

80

60

3.6V, –408C

40

3.3V, +258C

ソース電流 – mA

20

VOH

21065Lの出力電圧とホールド時間を要求しているデバイスの入力

3.1V, +858C

スレッシュホールドの差になるように選択します。典型的なΔVは

0.4 Vです。CLは(データ線あたりの)バス容量の合計で、ILは(デー

タ線あたりの)

もれ電流やスリーステート電流の合計です。ホール

3.1V, +1008C

ド時間はtDECAYに最小のディスエーブル時間(すなわち、書き込み

0

–20

サイクルではtDATRWH)を加えたものです。

3.1V, +1008C

–40

3.3V, +258C

3.6V, –408C

–60

3.1V, +858C

–80

REFERENCE

SIGNAL

VOL

–100

–120

0

0.50

1.00

1.50

2.00

ソース電圧 – V

2.50

3.00

t MEASURED

3.50

t ENA

t DIS

VOH (MEASURED)

図24.典型的なドライブ電流

OUTPUT

VOH (MEASURED) – ∆ V

2.0V

VOL (MEASURED) + ∆ V

1.0V

VOL (MEASURED)

テスト条件

VOH (MEASURED)

VOL (MEASURED)

t DECAY

出力ディスエーブル時間

出力ピンがドライブを停止し、ハイ・インピーダンス状態にな

OUTPUT STARTS

DRIVING

OUTPUT STOPS

DRIVING

り、

ハイまたはロー出力電圧からゆっくりと遷移を開始したとき、

ハイ・インピーダンス状態。

テスト条件では、約1.5 V。

ディスエーブルになったと考えます。

バス上の電圧がΔVだけ遷移

する時間は、容量性負荷CLと負荷電流ILに依存します。この遷移時

図25.出力イネーブル

間は、以下の式より概算できます。

CL×ΔV

tDECAY=――――

IL

IOL

図25に示すように、出力ディスエーブル時間t DIS はt MEASURED と

tDECAYの差になります。tMEASUREDは、参照する信号がスイッチして

TO

OUTPUT

PIN

から計測するハイまたはローの出力電圧からΔVだけ遷移するまで

の間隔です。

tDECAYはテスト負荷CLとILから計算され、ΔVは0.5 Vと

+1.5V

50pF

しています。

出力イネーブル時間

IOH

出力ピンが、ハイ・インピーダンス状態からドライブを開始し

たとき、イネーブルになったと考えます。出力イネーブル時間tENA

図26.AC測定のための等価デバイス負荷(すべての部分を含む)

は、出力イネーブル図で示されるように、参照信号がハイまたは

ロー電圧レベルになった時から、

出力が規定したハイやローの遷移

INPUT OR

OUTPUT

点に達するまでの間隔を示します。もし(データ・バスのように)

複数のピンがイネーブルにされたときには、

最初にドライブを開始

したピンの値が計測値になります。

1.5V

1.5V

図27.AC測定のためのリファレンスレベル(出力イネーブル/

ディスエーブルを除く)

− 36 −

REV.A

ADSP-21065L

容量性負荷

出力遅延およびホールドは、すべてのピンに対して50pF の標準

的容量性負荷を基準としています。遅延とホールドの仕様は、50 pF

以外の値の負荷に対しては1.8 ns/50 pFの割合で悪化します。図28

8.0

するかを示しています。図30は、

負荷容量によってどのように出力

遅延とホールドが変化するかを示しています

(このグラフや係数は

出力ディスエーブル遅延には適用されないことに注意してくださ

い。前述の「テスト条件」の「出力ディスエーブル時間」を参照)。

図28、29、30のグラフに示されていない範囲では、直線とは限りま

せん。

立ち上がり/立ち下がり時間 – ns

と図29は、容量の値によってどのように出力の立上がり時間が変化

7.0

6.0

5.0

RISE TIME

4.0

3.0

FALL TIME

2.0

1.0

18

0

0

20

40

60

14

80

100 120

負荷容量 – pF

140

160

180

200

図29.代表的な立ち上がりと立ち下がり時間(0.8 ∼2.0 V)

12

RISE TIME

10

6

8

5

FALL TIME

6

出力遅延またはホールド – ns

立ち上がり/立ち下がり時間 – ns

16

4

2

0

0

20

40

60

80

100 120

負荷容量 – pF

140

160

180

200

図28.代表的な立ち上がりと立ち下がり時間

(10∼90% VDD)

4

3

2

1

0

–1

–2

0

20

40

60

80

100 120

負荷容量 – pF

140

160

180

図30.代表的な出力遅延またはホールド

REV.A

− 37 −

200

ADSP-21065L

電力消費

代表的な電力消費は、以上の値に代表的な内部電力消費を加え

合計としての電力消費は2つの部分、

内部回路による消費分と外

部出力ドライバのスイッチング分とからなります。内部電力消費

は、

命令の実行シークエンスや使われる演算データに依存します。

内部電力消費は、以下の式で計算されます。

PINT=IDDIN×VDD

れば求められます。

(IDDINは電気的特性の項の計算を参照):

PTOTAL=PEXT+(IDDIN×VDD)

PEXTの最大値が発生する条件とPINTの最大値が発生する条件が同

じではない事に注意してください。最大のPINTは、100%の出力ピン

がオール1からオール0へスイッチングしているときには起こりえま

外部に関る部分の電力消費は、出力ピンのスイッチングにより

せん。通常のアプリケーションでは、出力のスイッチングが、100%

はおろか50%でさえ、同時に発生することはめったにありません。

起こります。その大きさは以下の事項に依存します。

−各サイクルでスイッチングされる出力ピンの数(O)

−ピンがスイッチングできる最高周波数(f)

環境条件

−出力ピンの負荷容量(C)

温度特性

−出力ピンの電圧振幅(VDD)

ADSP-21065Lは208ピンのMQFPおよび、196ピンのMini−BGA

パッケージで提供されています。

これを使って、

PEXT=O×C×VDD2×f と計算されます。

負荷容量にはプロセッサのパッケージ容量(CIN)も含めてくだ

さい。周波数fは負荷をハイにドライブし、再びローに戻すものを

含みます。アドレスとデータ・ピンは、SDRAMバースト・モード

ADSP-21065Lはケース温度(TCASE)が規定されています。TCASE

がオーバーにならないように、エア・フローが必要になることもあ

ります。

TCASE=TAMB+(PD×θCA)

TCASE =ケース温度(パッケージの上面で計測)

PD =Wで表現した電力消費(この値はアプリケーションに依

存します。PDの計算方法は「電力消費」で示していま

す)。

θJC =7.1℃/W (208ピンMQFP)

θJC =5.1℃/W (196ピンMini−BGA)

では、最大1/tCKのレートでハイとローにドライブできます。

例:

以下の条件で、PEXTを推測してみます。

−システムは1バンクの外部データ・メモリ(32ビット)を持つ。

−2 つの1 M ×1 6 のS D R A M チップを使用。各チップは

3 pFのコントロール信号負荷と4 pFのデータ信号負荷を持つ。

−外部データ・メモリの書き込みはバースト・モードで1/tCKサイ

クルに2回、つまり1/tCKサイクル/秒のレートで発生する。ピ

エア・フロー

表. ⅤI 温度特性(208ピンMQFP)

ンのスイッチングは50%とする。

−外部SDRAMクロック・レートは60 MHz(2/tCK)。

(リニア・フィート/分)

以上の仮定からPEXTは、

各ドライブできるピンの種類によって計

算されます。

θCA

(℃/W)

0

100

200

400

600

24

20

19

17

13

表. ⅤII 温度特性(196ピンMini−BGA)

表. V 外部電力消費の計算

(リニア・フィート/分)

ピンの

ピン スイッチング

タイプ

数

%

×C

アドレス 11

50

×10.7 ×30 MHz ×10.9 V =0.019 W

MS0

1

0

×10.7 −

×10.9 V =0.000 W

SDWE

1

0

×10.7 −

×10.9 V =0.000 W

データ

32

50

×7.7

SDRAM

CLK

1

−

×10.7 ×30 MHz ×10.9 V =0.007 W

×f

×VDD2

θCA

(℃/W)

=PEXT

0

200

400

38

29

23

×30 MHz ×10.9 V =0.042 W

PEXT=0.068W

− 38 −

REV.A

ADSP-21065L

208ピンMQFPのピン構成

ピン番号 記号

ピン番号

記号

ピン番号 記号

ピン番号 記号

ピン番号 記号

1

VDD

43

CAS

85

VDD

127

DATA28

169

ADDR17

2

RFS0

44

SDWE

86

DATA3

128

DATA29

170

ADDR16

3

GND

45

VDD

87

DATA4

129

GND

171

ADDR15

4

RCLK0

46

DQM

88

DATA5

130

VDD

172

VDD

5

DR0A

47

SDCKE

89

GND

131

VDD

173

ADDR14

6

DR0B

48

SDA10

90

DATA6

132

DATA30

174

ADDR13

7

TFS0

49

GND

91

DATA7

133

DATA31

175

ADDR12

8

TCLK0

50

DMAG1

92

DATA8

134

FLAG7

176

VDD

9

VDD

51

DMAG2

93

VDD

135

GND

177

GND

10

GND

52

HBG

94

GND

136

FLAG6

178

ADDR11

11

DT0A

53

BMSTR

95

VDD

137

FLAG5

179

ADDR10

12

DT0B

54

VDD

96

DATA9

138

FLAG4

180

ADDR9

13

RFS1

55

CS

97

DATA10

139

GND

181

GND

14

GND

56

SBTS

98

DATA11

140

VDD

182

VDD

15

RCLK1

57

GND

99

GND

141

VDD

183

ADDR8

16

DR1A

58

WR

100

DATA12

142

NC

184

ADDR7

17

DR1B

59

RD

101

DATA13

143

ID1

185

ADDR6

18

TFS1

60

GND

102

NC

144

ID0

186

GND

19

TCLK1

61

VDD

103

NC

145

EMU

187

GND

20

VDD

62

GND

104

DATA14

146

TDO

188

ADDR5

21

VDD

63

REDY

105

VDD

147

TRST

189

ADDR4

22

DT1A

64

SW

106

GND

148

TDI

190

ADDR3

23

DT1B

65

CPA

107

DATA15

149

TMS

191

VDD

24

PWM_EVENT1

66

VDD

108

DATA16

150

GND

192

VDD

25

GND

67

VDD

109

DATA17

151

TCK

193

ADDR2

26

PWM_EVENT0

68

GND

110

VDD

152

BSEL

194

ADDR1

27

BR1

69

ACK

111

DATA18

153

BMS

195

ADDR0

28

BR2

70

MS0

112

DATA19

154

GND

196

GND

29

VDD

71

MS1

113

DATA20

155

GND

197

FLAG0

30

CLKIN

72

GND

114

GND

156

VDD

198

FLAG1

31

XTAL

73

GND

115

NC

157

RESET

199

FLAG2

32

VDD

74

MS2

116

DATA21

158

VDD

200

VDD

33

GND

75

MS3

117

DATA22

159

GND

201

FLAG3

34

SDCLK1

76

FLAG11

118

DATA23

160

ADDR23

202

NC

35

GND

77

VDD

119

GND

161

ADDR22

203

NC

36

VDD

78

FLAG10

120

VDD

162

ADDR21

204

GND

37

SDCLK0

79

FLAG9

121

DATA24

163

VDD

205

IRQ0

38

DMAR1

80

FLAG8

122

DATA25

164

ADDR20

206

IRQ1

39

DMAR2

81

GND

123

DATA26

165

ADDR19

207

IRQ2

40

HBR

82

DATA0

124

VDD

166

ADDR18

208

NC

41

GND

83

DATA1

125

GND

167

GND

42

RAS

84

DATA2

126

DATA27

168

GND

REV.A

− 39 −

ADSP-21065L

VDD

RSF0

GND

RCLK0

DR0A

DR0B

TFS0