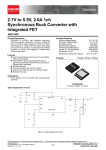

Download Zoom X5V 1613 Datasheet

Transcript