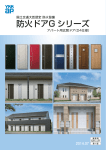

Download User Manual

Transcript