Download A3HCPU - User`s Manual

Transcript

REVISIONS

<-.

%Themanualnumber

is givenonthebottom

Revision

Print Date

*ManualNumber

Aug., 1987

I6 (NA) 66132-A

First edition

Jan., 1989

I6 (NA) 86132-6

"Instructions for Strategic Materials" added

left of the back cover.

INTRODUCTION

Thank you for choosing the Mitsubishi MELSEC-A Series of GeneralPurposeProgrammqblt?Controllers. Please read this manual carefully so that the equipment is used to its optimum.

A copy of this manual should be forwarded to the end User.

.

1.1

1.2

GONTENTS

"

r

;

*'

.I

.

2 SYSTEM CONFIGURATION

2.1Overall

2.2System

2.2.1

2.3General

2.4

.

.............................. 1-1 N1-6

How t o Use This Manual . . . . . . . . . ....................... .< ................ 1-2

1.1.1 A3HCPU features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-3

Comparison between A3HCPU and Al(E). A2(E). A3(E)CPUs. . . . . . . . . . . . . . . . . . . . . . 1-5

'INTROOUCT+ON........................

............................................

2-1 N 2 - 9

Configuration .....................................................

Equipment .......................................................

Notes on compatibility with other ME LSEC-A series equipment

Description of System Configuration ...................................

..............

SystemDesignConsiderations ...............................................

2.4.1 Safety circuit ......................................................

2.4.2 Unit selection ....................................................

3. SPECIFICATIONS.

2.1

2.3

2-4

2-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

.

3.1General

Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2

A3HCPU Unit Performance Specifications .....................................

-

2-7

2.7

-2-9

.c

.

3-76

3.1

3.2

3.2.1 A3HCPU unit performance specifications ................................

3-2

3.2.2 User memory assignment

3.5

.

3.2.3

list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.2.4 Instruction list ....................................................

3.18

3.2.5 Timer processingandaccuarcy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-.3 - 3 5

3.38

3.2.6 Maximum counting speed of normal counter ............................

3.2.7Self.diagnosis

..................................................... 3.39

3.2.8Parameteranddevicerange

setting ....................................

3.40

3.40

3.2.8.1 File registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

.............................................

.............................

(directhefresh)

switching

3-43

3.2.9 1/0control mode

3.2.10 Constantscan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

348

3.49

3.2.1 1 Program types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 2 Subsequence program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.50

3.2.13 Notes on writing subsequence programs ................................

3-51

3.2.14 Subroutine program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.53

3.2.15 Interrupt program and interrupt counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-54

.

3.2.16 Microcomputer program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3.59

3.2.1 7 Status latch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.60

3.2.1 8 Sampling trace. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

-3-60

3.61

3.2.19 Pause function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.20 Step run . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.63

3.63

3.2.21 Remote run . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.22 Assignment of 1/0 numbers. .........................................

3.64

3.2.23 Entry code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3.67

..

3.2.24 Print title entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.67

3.3Power

Supply Unit Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.68

3.3.1 Power supply unit specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-68

3.3.2 Selection of power supply unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-69

.

IB INA) 66132-A

I

f5:

L -

..................................................

.........................................

.......................................

....................

.............................................

...................................................

................................

............................................

...

i

.

-971

Base Unit Specifications

371

3.4.1 Main base unit specifications

3-71

3.4.2 Extension base unit specifications

372

3.4.3 Notes on the use of the.A56Bwd A588 extension bases

374

3.5

Extension Cable Specifications

375

3.6MemorySpecifications

i . . . . . . 3-75

3.6.1 Memory cassette specifications

375

3.6.2 IC memory specsifications

3.7

Fuse Specifications ......................................................

3-76

3-76

3.8

BatterySpecifications

3.4

....................................................

4.HANDLING

4.1

4.2

4.3

4.4

4.5

4.6

.

.......................................................

.....................................................

.........................................................

HandlingInstructions

4-1

4.1.1 Rnainunit

4-1

4.1.2 Memory (Memory cassette) ...........................................

4-1

4.1.3 Battery

42

Nomenclature

4-3

Memory Cassette Nomenclatwe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-5

Memory Cassette Preparation ...............................................

49

4.4.1 Memory i.c. installation

4-9

4.4.2 Memory protect switch setting

4.11

4.4.3 Batteryinstallation

4.12

4.13

Power Supply Unit

4.13

4.5.1 Nomenclature

4.5.2 Power

supply unit input voltage designation .............................

4.17

:.'4-18

Baseunits ...........................................................

4.6.1 Nomenclature ....................................................

4.18

4.6.2 Extension stage number assignment ...................................

4.21

..........................................................

...........................................................

..............................................

........................................

................................................

......................................................

.....................................................

5 LOADING AND INSTALLATION

5.1

5.2

5.3

5.4

5.5

. . 4 - 1 - 4.21

.......................................

51

hl

5-12

...................................................

51

InstallationEnvironment

52

Base UnitMounting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 Mountinginstructions .......................................

: . . . . . . . .5 2

5.2.2 Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

53

5.2.3 PC generatedheat calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

54

Installation andRemoval of Rack Mounted Modules ......................

. . . . . .5 6

Installation of Dustproof Cover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

58

Wiring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

59

5.5.1 Wiringinstructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

59

5-12

5.5.2 Power supply and grounding wirihg example.............................

.

.

6 PRE-START-UP ANDTEST PROCEDURES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6.1 m 6 - 2

6.1

6.2

Pretest Check List .......................................................

6.1

Test Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

:. . . . . . . . . . . .6.2

IB (NA) 661326

1. INTRODUCTION

1. INTRODUCTION

1. ,I~WODUGTION~.:'

i, ..

/MELSEC

.

.

ThisI'rnmkJal includes specifications, functions, and handling instructiohs for the A W C P U general. .

purpo3e programmable controller.

The M M C P U is, a high speed PC for use with standard A4eries .I& modulesand the majority

of the.&$eries special function modules, I t is programmed in the same way%as the other%A-Series

CPUs with some minor changes.

\

.

t

I

1. INTRODUCTION

1.1 How to Use This Manual.

This manual is divided up intosections as follows:

-Section 2:

Section 3:

W p a t i b i l i t y o t pmgramming p e r i p k a k , special

and utility aftware packages.

functionunits

General informationon

system configurations.

Hardware, software and performance specifi-

caticins.

Definitions and explanations of A3HCPU

ware features.

,

-

soft-

Section 4:

Nomenclatures for A3HCPW and. associated

hardware.

Hardware preparation, switch settinge@.

Section 5:

installationinstructions,environmental

ations, power supply requirementsetc.

Section 6:

Prestart-up test and c h d procedures.

Section 7:

Troubleshooting. List and definitionsof

codes. Troubleshooting digital I/O\wiring.

Section 8:

Periodic maintenance and inspection

requitements. Battery and fuse replacement.

consider-

error

Appendices

The following manuals

may

also be required

A1 (E), A2(E), A3(E) CPU 1/0 unit user's manual

A l ( E ) , A 2 E ) , A3(E) CPU Programming manual

A3HCPU P21/R21 Data Link Unit User's M m a l

Data Link Unit User's Manual

In this manual the AGGPP, AGPHP and AGHGP are

referred to as GPP/PHP/HGP respectively.

.

.

.

1. INTRODUCTION

.

/

.

.

.

1.2 Comparison between A3HCPU and Al(E), A2(E), A3(E)CPUs

I

tI

II

Control

method

1/0 control

mode

I

Programming language

Use with MELSAP language

1

Number of

inStNCtionS

Sequence instruction

I

Number of 110 poifits

I

I

Language decbkted

sequence control

(Relay s y w i , logic

y m b o l i c Ienguege)

I

No

I

Direst m a :

I

0.2 to 2 IWstep

0.2 to 0.4 pS/step

Refresh mode:

256

2048

Can be set between 10 and 19Oms

in 1Oms increments.,

Watch dog timerWDT)

2o(ms only

I

failure

power

Weight kg (Ib)

I

I

Memory capacity Max. 144K bytes

132 types

I

$32.

Within 2Oms

I

0.9 (1.98)

1

Within

1.65 (3.63)

Main sequence program

Max. 6K steps

Subsequence program

Max. 30K steps

Microcomputer program

Max. 58K bytes

(

"Fs!

Link relay ( 6 )

I

0.7 (1.54)

parameters

,

0.8 (1.76)

de^^,$^^^ 1

in the parameters

(L1000 to 2047)

Unavailable

I

I

I

d

t

lOOms timer: set time 0.1 to 3276.7 sec (TO to 199)

10ms timer: set time 0.01 to 327.67 sec (T200 to 255)

l O O m s retentive timer: set time 0.1 to 3276.7 sec

256

256

Normal counter:

set value 1 to 32767 (CO t o 255)

count:i

Specifications

~ \ ~ ~ , " ~ u ~ t &(co

7 6to7255)

interrupt program counter:

set value 1 to 32767

*Counter used in interrupt program

Interrupt

value to 32767

7 G i K G 5 5 uwc specified)

Counts tha number of interrupt signals

received.

1024 points (DO to 1023)

1024 points (DO to 1023)

Link register (W)

1024 points (WO to 3FF)

1024 points (WO to 3FF)

Annunciator ( F )

i

256

Data register (DI

I

~

Max. 30K steps

256

Number of points

Counter (12)

I

1024 points (BO to 3FF)

1024 points (BO to 3FF)

Specifications

I

I

s t e p s Max. 30K bytes Max. 14K

Unavailable

Number of points

Timer ( T )

I

Max. 10K bytes Max. 26K bytes Max. 58K bytes

(LlOOO to 2047)

0 point

(defaults to no value) '

2048

2Oms

Internal relay (M)

IS)

I

Can be set between 10 and 2 0 0 0 m r

in l O m s increments.

Max. 16K bytes

Step relay

'-

A3ECPU only

Max. 30K steps

Latch relay ( L )

I

1.25 to 2.25 pShtep

I

Max. 144K bytes

Program

capacity

I

1

2 2 ..t L

types 131

Constant scan function

(Program start +.qpecified intervals)

Iinstantaneous

Allowable

Yes

132 types

I

1

I

~

Language dedicated t o sequence control

(Relay symbol,logic symbdic Iangume)

- -

-

22 types

I

Basic instruction

Processing speed

(Sequence instruction)

.~~

Stored

Drwram.

. . r e.i a t e d oDeration

A l , A2, A3CPUs direct

A l E , A S , A ~ E C P U refresh

J

Refresh/direct (selectable)

I

to

11

Stored

program,

repeated

operation

I

(FO to 255)

points

256

I

points

256

255)

(FO to

I

I

I

I

I

.

-

., .. _,

.

1-5

IB lNAl €6132-A

i

1. INTRODUCTION

ABHCPU

File register ( R )

comments

,-

of

Max. 4032

Number

I

latch

I

function

switch

Offline

Status

I

function

F number indication

Annunciator display function

1

Unavailable

I

1

Available

( Y , M , L, B, F )

I

Available

Available

Output mode switching

at change from STOP to RUN'

Available

Available

7

I

Print title

~~

~~

Available

~~

Software I/O assignment

,

1

I

Using GPP/ PHP/HGP

F: "

*

F number

indiehion

Unavailable

Available

Entry code

I

Available

Operation mode switching

during error occunence

~~

I

1

UnavailaMe

Available

setting contactrunlpaute

Remote

Ientry

Availabla-

Max. 4032 points

I

4"+;*"I:...ik+,

Available

Available

Using GPP/PHP/HGP

I

I

.F'

'.

.I

.

.

.._

..

.

.

1-6

.. IB INAI €6132-A

1. INTRODUCTION

2.2 System Equipment

I

TYPI

Unit

I

I

1

tIcor:

I

MHCPUP21

A3MCA-O

.

o - 0 0 0

o--

e)

Without IC-RAM mernorv

0 0'0

bvtes h e x . 30K s t e m )

I

lemory

IC-RAM

I

I

'4KRAM

'4KROM

EP-ROM

8KROM

1

I

I

bytes (max. 60K steps)

I

I

8Kbvtestmax.3KrtbDs)

8Kbytes(max.3K

16K

bvtes

Imax.

Remarks

i

0

A 3 H C P U ~ 2 1 Far coexWdata link

(Master, local selectable)

For optical data link

(Master, local w l h l

I

t

Program

30K steps,

I/O p o t n t s : 3048 points

M, L total:2048points,

T : 266 poims

C: 256 points, D: 1024 points

A3HCPU

sw e m

1

Description

cawty:

CPU unit

Applimlbl

- beMemory

cassatte to

arranged separately.

0

O

I

steps)

7K stead

-.

O /

~~

TaMe 2.1 L i s t of Equipment

*With two memory

sockets

ABMAC-0 can be

loaded with IC-RAM

or EP-ROM memory.

ASMCA-2 to -18can

be loaded with only

EP-ROM memory.

1. INTRODUCTION

2.2.1 Notes on compatibility with other MELSECd sariesequipwt

.

,

1) All digital I10 modules are curnpat-wewith the A3HCPU.

2) All special function units (includinganalog I/O modules) are compatible with the A W W U with

the following exceptions:

a) AJ71C13

b)

AD57

c) AD58

d)

AJ71C24

e) AD51

Versioq

with

. .

Incompatibb.

Incompatible.

Incompatible.

Veroiqty with

compatible.

compatible.

H @receding the

serialnumber,

as shown below, are

H preceding the serial number, as shown below, are

I

58

Compatible with

3) The following microcomputer software packages are incompatible with theA3HCPU:

a) SWOC-UTLP-PID

b) SWOC-UTLP-FNO

C) SWO-AD57P

4) The followingrestrictions

A3HCPU:

a) AGGPP/AGPHP

b) AGHGP

c ) A7PU

d ) AGWU

Incompatible.

Incompatible.

Incompatible.

apply to the use of peripheralprogrammingequipment

with the

Use software package SWSGP-GPPAL?!:I-1/2, or subsequent versions.

Use software packageSW3-HGPAI:IKI-1/2, or subsequentversions.

Versions with H preceding the serialnumber, as shown below, are

compatible.

Versions with H preceding the serial

number,

as shown below, are

compatible.

A7PU

I

DATE

H

702 AC

I

Y

2-4

IB INAl 86132-A

1. INTRODUCTION

2.4 SysQm Design Considerations

_.

2.4.1 Safety circuit

Note the following:

On switching on the PC power supply, there is a short but fin$&time before the DC levels

operate normally. The same

reach their operating values. During this period, the unit will

applies when the power is cut as the D€ levels d r 6 below thdkbperating values. The following circuit will overcome any problems which may arise in output control due t o this phenomenon.

i

i

1

I

2-7

I

IB INN €81324

I

f

A

1. INTRODUCTION

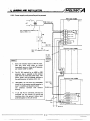

I System design circuit example 1

All AC

POWER

TRANSFORME

POWER

Mixed AC and DC

TRANSFORM

FUSE

1

*5

**1

recommended

*2

/*3

*\ MC

TC

*A

1

' 1 : Runhtop circuit interlocked withR A l (run monitor relay)

'2: Battery lowalarm

'3: R A I switched on by M9039 (run monitor relay)

' 4 : Power to outputequipment switchedoff when stop signal given.

*5: Input switched when power supply established.

'6: Set time for DC power supply to be established.

' 7 : On when run by M9039

'8: Interlock circuit as neccessary.

The power-on procedure is as follows:

For AC

1)

2)

Switch on power.

Set CPU t o RUN.

3) Switch on the start switch.

4 ) When the magnetic contactor (MC) comes in, output equipment is powered and may be driven from the program.

For ACJDC

1)

2)

Switch on power.

Set CPU t o RUN.

3) When DC power is established, RA2 turns on.

4 ) Timer (TM) times out after the DC power reaches 100%.

(The set value of TM should be the period o f time from when RA2 switches on t o the establishment of 100%

DC voltage. Set the s e t value t o approximately 0.5 seconds.)

5) Switch on the start switch.

6) When the magnetic contactor (MC) comes in, the output equipment is powered and may be driven by the

program.

2-8

IB lNAi 66132-A

1. INTRODUCTION

2.4.2 Unit selection

(1 Power supply unit

(a) Select the power supply according to the 5 V P C current requiredin the systw.

If the capacity is to6zmall, there will be 8 &qp in the DC 5V, resulting i n % W shutdown,

erroneous I/O signals, etc.

(b) The 5V DC power to an A556 or A586 extension base, is suppJid.;from the power supply

on the main base unit. WhenUsing either of these extension bases'ensure t h a t the power

supply selected has sufficient capacity for bothbases.

(c) When using the 24V DC output from the

is never exceeded.

power supply ensure thqt the current capacity

? r

(d) When using an A66P power supply unit, instalh it a t the right e,nd,of thebase unit.

The unit located t~ the left of the A M P must be selected according t o Section 3.3.2 (3) as

the 24V DC output from theA66P varies according to this unit,

(e) Power supply specifications can be, found in Section 3.3.

(2) Extension base unit

For base units

(A556,

A5861

not

requiring

their

own

power supply unit,

5V

DC is supplied

from the power supply unit in the main base unit via the extension c a ~ g as

, described in (2) (a)

above. In this case, a voltage drop occurs

over the extension cable SD thatthe voltage at the

receiving end is less than that at the source end.

Since a t least 4.75V DC i s required a t the receiving end, it is neccessary to select the base unit

so that the voltage does not drop to less than 4.75V DC. For information on selecting the A556

or A586, refer to Section 3.4.3.

,

7

!

I

i

For information on 1/0 units, refer to the A l , A2, ABCPU I/O Unit User's Manual.

I

f

c

3. SPECIFICATIONS

3.1 General Specifications

Itam

1

I

Spedfications

Operating ambient

temperature

0 to 55OC

Storage ambient

temperature

-10 to 75OC

Operating ambient

humidity

10 to 90%RH, non-condensing

Storage ambient

humidity

10 to 90%RH, non-condensing

Frequency

Conforms to JIS C 091 1

Vibration resistance

I

I

10 to 55Hz

-

0.075mm

55 to 150Hz

lg

-

Sweep Count

10 times

" ( 1 octave/minute)

Shock resistance

Conforms to JIS C 091 2 ( l o g x 3 times in 3 directions)

Noise durability

By noise simulator of 1OOOVpp noise voltage,

1p.s noise width and 25 to 60Hz noise frequency

15OW AC for 1 minute across AC external terminals and ground

m v AC for 1 minute across DC external terminalsand ground

Dielectric withstand

voltage

Insulation resistance

Grounding

Operating ambience

-

Acceleration Amplitude

I

5MS2 or larger by 500V DC insulation resistance tester across

AC external terminals and ground

Class 3 grounding

(Grounding

not

neccessary for PC operation)

Free of corrosive gases. Dust should be minimal.

Cooling method

Self-cooling

Table 3.1 General Specifications

One octave marked indicates a change from the initial frequency to double or half frequency. For example, any

of the changes from 10Hz to 20H2, from 20Ht to 40Hz, from 40Hz to 20Hz, and 20Hz to 10Hz are referred to as

one octave.

3-1

I8 (NA) 66132-A

3.2 A3HCPU Unit Performance Specifications

3.2.1 A3HCPU unit performance specifications

Items marked *. in the table are enabled, or their ranges assigned, in the PC parmeters using the

peripheral quipment (PU, GPP, PHP or HGP, but partly restricted in the case of PU). 'For details

of parameter setting, refer to Section 3.2.8 "Parameterandrange

setting". The following table

shows default settings:

Item

I

I

Performance

I

I

Control system

Stored

repeated

program,

I

1/0control method

(I/Ocontrol

setting)

Direct/refresh method

Sequence instruction

22 types

Basic instruction

132 types

Application instruction

107 types

Direct mode

Processing

speed

Sequence instruction 0.2 to 2 p/step

Refresh mode

I

Constant scan

(program start at specified intervals)

Memory

capacity

and

memory type

II

Language dedicated to sequence control

(Combined use of relay symbol type, logic symbolic language)

Programming language

Instruction

operation

Sequence instruction 0.2 to 0.4 p/step

Can be set between 1Oms and 19Oms in 10ms

increments

Memory capacity

Max. 144K bytes

Memory type

(Memory cassette type)

Memory cassette A3MCA-0 to A3MCA-18

(For memory cassette details, refer to Section 3.8.)

* Main sequence program capacity

6K steps

(Can be s e t to max. 30K steps)

1/0 points

2048 points

* Internal relay (M)

* Latch relay (L)

1000 points (1000 bits)

I

1048 points ( 1048 bits)

I

*Step relay (S)

Link relay (B)

Defaults to no value.

Used in the same manner

as theinternal relays

1

The number of M+L+S

devices is 2048

t

BO to 3FF 1024 points (1024 bits)

Table 3.2 Performance Specifications

-

3-2

IB INN 66132-A

Item

Number o f points

I

I

Performance

256 points

TO to 199, 1 0 h s timer:

setting time 0.1 t o 3276.7 sec

*Timer

Specifications

* Counter

Number of points

OSet values can be changed

by parameters.

OTimer accuracy

t 2 scan times

, -1 scan time

T200 to255, 1 ( x n s timer:

setting time 0.01 t o 327.67 sec

I

I

Specifications

1 o O m s retentive timer:

depending on setting

(setting time 0.1 t o 3276.7 sec)

256 points

CO t o 255, normal counter: setting range 1 t o 32767

(C224 t o C255 may be used as interrupt counters. See Section 3.2.15.)

Data register ( D l

DO to 1023, 1024 points (16 bits per word)

Link register (W)

WO to 3FF, 1024 points (16 bits per word)

Annunciator ( F )

FO t o 255, 256 points (256 bits)

I

* File register ( R )

Depending on setting (Max. 8192 points)

AO, A l , 2 points (2 words)

Accumulator ( A )

Index register (V, 2 )

Pointer (P)

(I)

Pointer

interruption

for

Special relay (M)

I

I

I

V,

PO t o 255, 256 points

IO to 3 1 , 3 2 points

M9000 to 9255,

256

* Status latch

Set in parameters (Max. 24K bytes)

*Sampling trace

Set in parameters (Yes.

* Comment

* Subsequence program capacity

* Latch

I

Set in parameters (Max. 30K steps)

L1000 t o L2047 (1048 points)

* Link range

Set in parameters

* Remote runlpause contact

Set in parameters

* Operation mode a t the time oferror

I

1/0 error : STOP

Software instruction error : CONTINUE

F number display

*Annunciator display mode

* Entry code

* Print title entry

mode

. . . .8K bytes)

Set in parameters (Max. 4032 points)

(power failure compensation) range

+. RUN

output

points (256 bits)

D9000 to 9255, 256 points (256 words)

Special register ( D l

*STOP

Z,2 points (2 words)

1

I

Output data a t time of STOP is restored.

Set in parameters

I

Set in parameters

Table 3.2 Performance Specifications (Continued)

3-3

IB (NAI 66132-A

Item

Performance

* 1/0 assignment

The number of 1/0 points allocated to each dot is dictated by the

individual l/O units used. An emptyslot mupies 16 points.For

details, refw toSection 3.2.22.

* Selfdiagnoftlc functions

M o c y error dewthan, CPU error detection, 1/0 error detection,

Watch dog error monitor (watchdog timer 2 0 h s only)

battery error detection,etc.

(For deteils, refer to Section 3.2.7.)

__

At power-on, a t power restoration

after power failure

Automatic restart when “RUN” switch is moved t o ON position

(Initial start)

I

IC-RAM backup

I

Break point setting and run per instruction can be executed using

peripheral equipment (not PU) connected to the CPU unit.

Step run

I

Other

functions

*

I

lctequpt program can be run in response to a signal from

Interrupt processing

I

rupt unit or bya constantcycle interrupt signal.

an inter-

Data link

* Microcomputer mode

Depending on setting

power failure time

Within 2Oms

Current consumption (A)

3.0

Weight kg (Ib)

0.9 (1.98)

External dimensions

mm (inches)

250 x 79.5 x 121

(9.84) (3.13) (4.76)

r

1

Items marked in this table are set in parameter mode using any of

the peripheral programmingdevices.

Parameters

I

By lithium battery

Battery guaranteed for 5 years.

For total power failure guarantee time, refer to Section 8.3.

t

Table 3.2 Performance Specifications

POINT

MELSAP (MELSEC Flow diagram programming language) cannot be used to write A3HCPU

programs.

I

.

.

3-4

IB (NAI €6132-A

ct

4

i

*

1

3.2.2 User memory assignment

The user memory may be arranged as required to suit the individual application. Memory allocation is made using any of the peripheral programming devices. Where memory allocation has not

been made, the PC uses i t s default settings as described in paragraph (1 ) below.

(1 ) User memory not assigned by parameter setting,

The following memory maps are the default settings adopted by the PC when parameter setting

has not been made.

1

I

I LROM operation J

RAM ODeration I

Parameter

T/C set value

Memory cassette

capacity

(Max. 144K bytes)

REMARKS

I

Main

sequence

program

memory

cassettes

IA3MCA4 to 18.1

3K bytes

K

1 bytes

I

I

Parameter

I

I

ROM memory

capacity

(Max. 64K bytes)

I

I

Max. 6K

I

steps

I

( 12K bytes) I

I

I

,

I

Memory cassette

capacity

(Max.144Kbytes)

3K bytes

1K bytes

Main

sequence

program

Max. 6K

steps

(12K bytes)

for memory

cassettes

I

1

(1) The parameter and T/C set value areas (4K bytes) are assigned t o the user memory automatically.

(2) The main sequence program includes the main routine, subroutines and interrupt programs.

(3) When the sequence program capacity is less than the user memory (memory cassette) capacity, a vacant

area is l e f t as shown above.

,

3-5

18 (NAI 66132-A

(2) User memory assigned in parameters.

In ocder to dnable some of the PC functions, memory areas must be allmated acmrding to the

function required using any of the peripheral programing devices (use of thaPU, h o w e r , is

limited). Memory areas to which allmation may k

m

&

e are shown below. MW-that the total

amount of memory usedmust not be greater than the capacity of the memory cassette used.

I

I

Parameter

4K bytes are always required from the user memory

area for storing the parameter settings.

T/C set value

Microcomputer program

Memory cassette

RAM area

1 1

:;:7

Can be set between 1 and 30K steps (2 and 60K

bytes) in 1 Kstep (2K byte) increments.

1

Data area

File register

No (OK byte) or yes (8K bytes) can be selected.

No (OK byte) or yes (8K bytes) can be selected.

No (OK byte) or yes (bytes set for file registers)can

be selected.

Canbe set between 0 and 16K bytes (0and 8192

points) in 2K byte (1024 point) increments.

Canbe set between 0 and 64K bytes (0and 4032

points) in 1K byte ( 6 4 point) increments.

File register

Comment

I ROM operation 1

Parameter

Memory cassette

ROM area

4K bytes are always required from the user memory

area for storing the parameter settings.

TIC s e t value

Sequence program

1

Microcomputer program

I :a I

~

Sampling trace

I

-1

Memory cassette

RAM area

1

1

i

I

Data area

File register

File register

'

Canbe set between 1 and 30K steps ( 2 and 60K

bytes) in 1K step (2K byte) increments.

No (OK byte) or yes (8K bytes) canbeselected.

No (OK byte) or yes (8K bytes) can be selected.

No (OK byte) or yes (bytes set for file registers) can

be selected.

Canbe set between 0 and 16K bytes (0and 8192

points) in 2K byte (1024 point) increments.

Canbe set between 0 and 64K bytes (0and 4032

points) in 1 K byte (64 point) increments.

3-6

IB (NAJ €6132-A

The A3HCPU memorymay

cassette used.

be assigned within the following rangesdepending

onthememory

A3MCA-2

1 RAM operation 1

II

Memory

cassette

capacity

Max. 16K

bytes

(IC-RAM

memory

Parameter

I 3K bytes

Parameter

3K bytes

1 K byte

Max. 6K steps

(1 2Kbytes)

Max. 10K bytes

1 K byte

Max. 2K steps

(4K bytes)

Max. 2K bytes

)I1

11

Unused

Sampling trace

File register

~ROM

operation

I

Parameter

1.

!I

5K bytes

8K bytes

Max.

byte'

10K

(5120 points)

Max. 10K byte!

(576 points)

1 R O M operation I

ROM

memory

capacity

Max. 64K

bytes

(32K steps)

Memory

cassette

capacity

Max. 16K

bytes

3K bytes

bytes

3K bytes

1K byte

W X . 30K steps

(60K bytes)

Max. 58K bytes

1 K byte

Max. 5K steps

(10K bytes)

Max. 8K bytes

5K bytes

8K bytes

Max. 16K bytes

Max. 16K bytes

bytes

(8192 points)

Max. 16K bytes

(960 p o ~ n t s )

3-7

IB INAI 66132-A

1

A3MCA-4

A~MCA-~

I RAM operation

m

r

y

'

cassette

capacity

Max. 32K

bv

bytes

.

I RAM operatioh]

3K bytes

1K byte

Max. 14K steps

(28K bytes)

Max. 26K bytes

1K byte

Max. 1OKsteps

(20K bytes)

Max. 18K bvtes

3K bytes

1K byte

Max. 30K steps

(60K bytes)

Max. 58K bytes

1K byte

Max. 26K steps

(52K byte9

Max. 30K bytes

5K

5K bytes

8K bytes

8K bvtes

Max. 24K bytes

Max. 24K bytes

Max. 16K bytes

M a x . 16K bytes

Max. 26K bytes

Max. 58K bytes

L36_4-~p_oi

(8192 points)

ROM

memory

capacity

Max. 64K

bvt-

(32K step3

Memory

cassette

capaclty

Max. 32K

bvtes

p r

'-

(8192 points)

2sL -

3K bytes

1K byte

Max. 30K steps

(60Kbytes)

Max. 58K bytes

1K byte

Max. 13K steps

(26K bytes)

Max. 24K b v t e s

memory

program

Memory

cassette

capacity

Max. 64K

bytes

5K bytes

8K bytes

I

+1

3K bytes

1K b y t e

Max. 30K steps

,(60K bytes)

Max. 58K bytes

1K byte

Max. 29K steps

(58K bytes)

Max. 56K bytes

i

i

5K bytes

Unused

Samphng trace

8 K bytes

Max. 24K bytes

M a x . 16K bytes

(8192 points)

Max. 64K bytes

Max. 16K bytes

18192 polntsl

M a x . 32K bytes

(1984 polnts)

(4032 points)

f

I

3.8

r

1

IB lNAl 66132-A

I

1I

ABMCA- 18

A3MCA- 12

j

RAM operation

RAM operation

3K bytes

1K byte

Max. 30K steps

Unused

/I 1-1

I

ROM

II

File register Max. 24K bytes

Max. 16K bytes

(8192 points)

Max. 64K bytes

14032 Dointr)

Parameter

--__ -_

I t 3K bytes

capacity

capacity

Max. 64K

bytes

(32K steps

I

Memory

caSsette

S i Z K

bytes

‘FIl

II

Ilnused

cassette

I

bytes

Comment

64K

Max.

bytes

Max. 24K bytes

I’

\I

Comment

--- --

Max. 16K bytes

(8192 points)

11bytes

64K

Max.

- 14032 mints1

J

3K bytes

1K byte

Max. 30K steps

(60K bytes)

Max. 58K bytes

1K byte

Max. 30K steps

(60K bytes)

Max. 58K bytes

5K bytes

0K bytes

8K b

by

y tt e

e

8K

File register

REMARKS

5K bytes

8K bytes

File register

memory

Memory

cassette

capacity

Max. 144K

bvtes

5K bytes

II

3K bytes

1 K byte

Max. 30K steps

(60K bytes)

Max. 58K bytes

1 K byte

Max. 30K steps

(60K bytes)

Max. 58K bytes

Parameter

1K byte

Memory

cassette

capacity

Max. 96K

bytes

1

Max. 24K bytes

Max. 16K bytes

(8192 points)

Max. 64K bytes

(4032 points)

Max. 16K bytes

(8192 points)

(4032 points)

I

(1) 4K bytes of user memory are always required for parameter and timerhounter set value storage.

(2) ”sequence program” includes subroutine and interrupt programs.

(3)Note the following when assigning memory protect areas:

Parameter, sequence program and subsequence program areas are assigned, in order, t o the beginning

of t h e memory map.

Comment, file register, status latch, and sampling trace areas are assigned to the end of the memory

map as indicated above. There is therefore an unused memory range between the two areas. Memory

protect should therefore be assigned t o the first part ofthe memory map.

(4) The maximum values for items shown above indicate the maximum value for that item taken on its

own.

(5) When mixing ROM and RAM, any item other than the sequence program may be assigned to RAM.

(6) The capacities shown above for microcomputer and submicrocomputer programs are the maximum

possible with thecorresponding sequence program areaset t o 1K steps (=2K bytes). Sequence

program + microcomputer program must be 60K bytes.

<

3 -9

IB (NAJ 66132-A

3.2.3 Device list

Thissectiongives the namesandaddressranges

of the devices availableon the A3HCPU. Items

marked* in the table are enabled, or their ranges assigned, in the PC parameters using the peripheral

equipment (PU, GP?, PHP or HGP, butpartly restricted in the case of PU). For detairs otparameter

setting, see Section 3.2.8 "Parameter and range setting."

Points

Remarks

X, YO to 7FF

(X, Y total 2048 points)

X, Y numbers are in

Device

X

Input

~

Y

I

I

Output

Special relay

*

1 1

Internal relay

*

L

Latch relay

*

I

I

I

1

s

F

I

1

I

T

Step relay

Annunciator

looms timer

I

1

j

I

I

M9000 to 9255 points)

(256

MO to(1000

999

D

II w 1i

R

IA I

V

1

~

I

ber of

c:S=2048

Set in parameters

DDOOO to 9255 (256 point)

Link register

WO to 3FF (1024 points)

I

I

K

Decimal constant

H

Hexadecimal constant

II

POINT 1

I

I

There are 256 points

of timers and counters,

respectively.

I

Set in parameters (0point)

~

2 (1 point)

I

I

I

V (1 point)

(8

NO to 7

W numbers are in

hexadecimal

I

points)

(2

AO, A1

~

Index register

Pointer

interruption

for

,

(0point)

Special register

Pointer

...

CO to 255 (256 points)

DO to 1023 (1024 points)

I P I

M+

Set in parameters (0point)

Data register

Nesting

___

T200 to 255 (56 points)

Interrupt counter

Accumulator

~~

-

TO to 199

points)

(200

Counter

File register

num-

FO to 255 (256 points)

1Oms timer

I N 1

II1

I

I

Set in parameters (0point)

~~~

Z

points)

L1ooo t o 1024 ( 1024 points)

1 Wms retentive timer

C

hexadecimal

I

levels)

I

PO topoints)

255 (256

I

IO t o 131points)

(32

K32768 to 32767 (16-bit instruction)

K2147483648 to 2147483647 (32-bit instruction)

HO to FFFF (16 bitinstruction)

HO to FFFFFFFF (32-bit instruction)

Table 3.3 Device List

I

The function of step relays (S) is identical to that of internal relays (M).

3-10

. .

IB (NA) €6132-A

r

( 1 ) Special relay list

The special relays are internal relays with spwial functions, They are mostly used as contacts

to provide interlocks, timing pulse chains, etc. Table 3.4 shows the special relay list.

M9200 and following are used in conjunction with theMELSEC-NET data link system.

Number

I 2- I

I

I

1

1

.

II

I

I

I

I

I

k'9002

k'9005

~'9006

hb007

Name

I

Fuse blown

I

Battery low

I

I

It0 unit

Error

ON:

error

verify

detection

1

OFF:Normal

ON: Fus.?biown in an

1/0 module

1

I gLF:

OFF: AC supply normal

ON: AC is down

Battery low

OFF:

Normal

latch

ON:

Annunciator

detection

*1

Operation

error

Error

M9011 ON:

flag

M9017

M9020

M9021

M9023

M9024

II

I

I

1

Battery

low

No error

Turned on by a power failure of within 10ms. Reset when PCCPU

is reset.

0

Turned on when battery voltage drops below that specified.

Turned off when battery voltage i s restored.

0

Turned on when battery voltage drops below that specified.

Remains on after battery voltage is restored.

0

Turned on byself-diagnosed error.

OFF: No annunciator

detected

ON: Annunciator

detected

.Turned on when OUT F or SET F instruction is executed.

Switched off when all annunciators ( F ) are switched off.

OFF:

No

0

Turned on by an application instruction processing error.

Remains on after normal status is restored.

0

Carry flag used i n application instructions.

error

@Clearsthe data memory(otherthan

special relays and special

etc. when M9016

registers) in remote run mode from computer,

OFF: Ignore

clear flag

ON:

Output

clear

Data memory

Clears the unlatched data memory (other than special relays and

special registers) in remote run mode from computer, etc. when

M9017 i s on.

User timing

clock No. 0

User timing

clock

No.

1

I

I

0 Scan dependent clock pulse.

0After poweronor

CPUreset, thedutclockcontacts

On and off periods are specified i n the

instruction.

-n

clock No. 2

User timing

clock No. 3

User timing

clock No. 4

M9032

1 second

clock

M9034

Turned on when one or more output unitfuses have blown.

Remains on after normal status i s restored.

clear

0.2 second

clock

I

I

low

ON:

Output

M9031

M9033

0

.Turned on when an 1/0 unit is removed from,or added to the

system while the power is switched on. Remains on after normal

status is restored.

OFF:Normal

Self-diagnostic

OFF:

Error ON: error

M9009

Details

Description

2 second

clock

1 minute

clock

I+++

n l scans

1

-

0.1

seconds1 seconds

o.l

DUTY

I

nl

n2

are open.

M9020

*Time dependent clock pulse: 0.1 second, 0.2 second, 1 second,

2 second, and 1 minute clocks.

@ N o t scan dependent (i.e. will be switchedduring scan if corresponding time has elapsed).

0 Starts when power is turned on or CPU is reset.

0.5

seconds seconds

loa5

I

secnndc

s30 e

d

zondz

Table 3.4 Special Relay List

3-1 1

IB (NAl €6132-A

I

I

Number

Name

I

I

bription

~_____

Details

as dummy

contacts

forinitialization

and

application

ructiqw,

$%36

arid )3;$037 are turned on and off indepwdently of the

&?switcH

on'thc

. .

q h q n m d w n d i n q o n t h gppfivh Wsition.

8 and M 9 are d t c h e d off If the key swlfch isfn'STOP

position.

M9038 is switched off (on for one scan onlv) and M9039 switchon(offfor

one scan only) ifthekey&itch

is n o t in STOP

position.

.Used

rv

fl8.andm

MbR

Q

M9039

RUN flag (off

ON

only for 1 scan :

M9040

PAUSE enable

coil

M9041

.

PAUS@M u s

,

Stop status

OFF: During stop

ON : Otherthan

canted3

Sampling tr=

complete

I

Sampling trace

1

trace

I

M9051

1

*When RUN key

witch is a t PAUSE position orremote

contact has tuon and i f M9040 is on, the PC enters PAUSE

mode and M9041 i s turned on.

,

stap

OFF:During=mpting

trace

' ,

ON: Samplingtmte

complete

OFF: Trece

inaceiue

ON: Trace actlve

I

o F F : Sampling traCe

oN: Sampling trge

witching

Main program

M9056 OFF:p,

Other

I set than

request

,

OFF: Decode function to

7-segment display

data

ON: Partial refresh

function

*The SEG instruction function is changed byswitchingM9052

onloff in the sequence program.

ON:

.Turned

P, I set request

P, I set

request

ON:

During P, I set

-request

OFF: Except during P, I

set request

M9057

Subpidgram

P, I set request

M9058

Main program

P, I set

complete

Pulsed on completion

Subprogram P, I

set completion

Pulsed on completion

of P, I setting

'2

M9084

Switched on during sampling trace.

.Sampling trace is startedbyswitchingon

M 9 w 7 in theprogram.

M9047 is automatically

switched

on

if sampling is started from

the GPP. By turning off "7,

sampling trace i s stopped,

I

M9059

,unecl un ru

the specified

Reset when

. '

M9055

Status

latch

OFF:

Not

complete

Complete

instruction.

ON: flag

complete

!

.

CMG instruction

ON:

Disable

disable

OFF: Enable

SEG instruction

M9052

1

I

I

~~~

OFF:PAUSE d&Ibd

ON: PAUSE enabled

OFF:Duringpaur).

ON: Omerthan pauao

oorreect

M9043

M-

1 scan

afterrun)

M9042

I

- _.

mu.

Error check

of P, I setting

OFF: Checksenabled

ON: Checks disabled

on when status latch is completed.

Turned

off by reset

C

Provides P, I q t requestafter completion of program correction

when correction of the,qthergrogram (for example subprogram

when main probram i s being run) is made during run.

Turned off after setting is complete.

.

, 0

Pulsed on after c o m p w o n

I

1

of P. I setting.

.Specify whether the YOllowlng errors are to be checked or not

after the END instruction is executed (to reduce END processing

time):

. Fuse blown

1/0 unit verify error

Batteryerror

i

.

.

I

I

Table 3.4 Special Relay List (Continued)

c

3-12

I

+

i

*

IB INA) 56132-A

f

POINT

*

(1) S m a l relays marked 1 above, are a

lW

h

d "on" and will remain on after normal status

is restored. S w i M then off as follows:

1) From the user program

Use circuit

the

shown on the right and turn on

the reset command contact to clear the special

relay M.

Reset command

RST M - 0 4

-$-

Specify the device to be reset.

2) From the peripheral equipment(PU,GPP,PHP

or HGP)

Use the test function to forcereset the device. For the operation procedure, refer to

the appropriate manual.

3) RESET the PC CPU using the key switch. Thiswill reset the special relay.

(2) M9084 marked *2 is switched on/off in the sequence program.

3-13

18 I N N 661324

. .

.

(2) Special register list

data registers with spedal functions: Data should not kwittei.l to

these registers (except those marked * in the table).D a t a mav bemad ftom th8)spedat registers

and used as appropriate imthe program. Table 3.5 shows the special register list.

D92QO a@?foHowing are used in conjunction with the MELSECNET data link system.

The sp&t~;registem.are

..

I

Number

I

Name

I

Data

I

D9000

Stored

I

Lowest unit number

lobation with blown fuse

I

Explanation

0

I h c a t e s the he&: 110

&

e

nof

th6 l o w e s t I/O unit number in

which tho fuse hwjblow% Jika the hWdec-1 monitor function

on the peripheral equipment to read the data.

(Cleared by resetting D9100 t o W107 t o 0.)

I

Indicates the head I/O address of the lowest 1/0 unit number for

vVhkh

t I 0 onlt verify wrar.has been detectlcl k u r a of error:

0

Lowest unit number

location with 1/0

verify error

l/O unit

D9002

verify error

0

I

.D9008

I

Selfdiagnostic

error

I

Self-diagnostic

number error

I

0

gn

addition or removal of an 1/0 unit while the power is on). Use the

hexadecimal monitor function on the peripheral equipment toread

the data.

(Cleared by resetting D9116 to D9123 to 0.)

1 is added each time the input voltagedrops to 80% or less of

rated while the CPU unit is operating, and the value stored in BIN.

Records the self-diagnosed error number.

Records the number (in BIN) of the earliest annunciator coil (F)

to be switched on by1 - 1

or

0 09009 can be cleared by executing the

or m

j

CPU front. If

instructionor

pressing INDICATORRESETon

another F number has been detected, the clearing of 09009 causes

the next number to be stored in D9009.

0

D9009

Annunciator

detection

Earliest annunciator

number detected

D9011

Error step

Step number

location of

operation error

0

r

+

,

Records the step number (in BIN) a t which an application instruction processing erroroccured.Errordatacannot

be overwritten

until special relay M9011 i s reset by the user program.

Table 3.5 Special Register List

..

.,

.

3-14

IB (NA) 66132-A

V

/MELsEC-A

-

3. SPECIFICATIONS

Number

Name

Stored Data

D9015

CPU operating

status

Operation status

of CPU

Explanation

Theoperating

below:

status of the CPU is stored i n D9015 as shown

t

CPU Operating mode

0

1

2

*PAUSE

3

STEP RUN

-0

1

STOP

2

*PAUSE

Program status

I

1 - 1

0

1

I

I: Malnprogram

IROM)

I : Main program I R A M J

2 . Subprogram ( R A M )

D9016

Program

number

D9017

Scan time

Mlnimum scan time

( I n units of 1Oms!

D9018

Sqan t i m e

( i n units o f 10msi

D9019

Scan time

Maximum scan time

( I n units of 1 Oms)

that

below

i

I

1 m]instruction executed

I

Remote RUNiSTOP from host computer

I o

':

Other

than

1

I

I

I

1

RUN

STOP

When M9040 (Pause enable) i s o f f , and the CPUkcmyswitch

moved to PAUSE, the CPU remains in RUN mode.

Indicates which sequence program i s currentlyrunning

number; 0.1 or 2.

is

As a B I N

~

Scan tlme

Records the minimum program scan time a s a BIN integcr multiple

of 10ms.

Records the previous

of 10ms.

program scan time as a BIN Integl?r multlple

*Records the maximum program scan time as a BIN r t e g e r multiple of 10ms.

Table 3.5 SpecialRegisterList

(Continued)

/MELSEC

3. SPECIFICATIONS

Number

l l

Stored D a t a

Name

I

I

'D9020

Constant scan

Constant scan

time

(Set by user in

lOms Increments)

D9044

For sampling

Step or time for

sampling trace

I

trace

Explanation

I

Sets theinterval

betweenconsecutive program starts inmultiplesof

0: No setting

1 to 19: Set. Program is executed at intervals of ( s e t value) x 10rns.

(See Section 3.2.10.)

Determines

the

sampling

trace

0

For scan

For time -Time

operating conditions a s a BIN number.

~

Indicatesthe

10ms.

( i n units of 10rns)

output unit numbers with blown fuses. Indication i s in blocks

of 16 110 points and parameter 110 assignment is valid.

1 5 1 4 1 3 1 2 1 1 1 0 9

8

1

1

r

'D9102

'D9103

Blt map of 110

units with

blown fuses

Fuse blown unlt

"D9104

F-7

'D9105

0 0 ,:: 0

7

o,,,o

6

5

4

2

1

0

0 0 0 0

D9100

0

D9101

,1 , , o o o o . o o o o o o o o o o

D9107

0

0 0 0

3

1

/-

-0 0

I

0 0;i.

0

0 0

0

0

0

0

1.

4

0 0 0

4

Indicates blown fuse.

(Data i s latched and must be cleared from the user program)

'D9107

0

Indicates the 110 unit numbers with 110 unit verlfy errors. (Cause of error:

addition orremoval of an 110 unltwhile the power i s on) Parameter 110

assignment is valid.

151413121110 9

'D9118

110 unit

1

~

D9116

Bit map of 110

units with

verify errors

D9117

D9123

'D9121

0 0

0

0

//=

.

0

8

0 0 0 0 0

0 0 0 0

7

6

0 0

0 , ; . 0

5

4

010

3

2

0 0

1

0

1

o,.,

0 0 0 0 0 0 0

F_

O , ' : , O 0

0

0 0

0

0 0 0 0 0

0 0

0

t

Indicates I10 unit verlfy error.

'D9122

*

D9123

Dg124

I

(Data i s latched and must be cleared from the user program.)

,

I

Number of

detected an.

nunciator signals

1

1

I

i

Number of un.

processed

1

,

I I S add to the contents ofD9124

each tlme any of the annunciator ( F i

coils i s swltched on (by 1 or [ S E T ] 1. 1 i s subtracted from the

contentsD9124

of

each time an F coil i s reset (by

,

or

INDICATOR R E S E T ) .

e l h e number i s shored

BIN in

Table 3.5 SpecialRegister

and i s

<8

List (Continued)

/MELSEC

3. SPECIFICATIONS

1

Number

_

_

,--..

Name

. ...

Stored Data

1

-D9126

.-

~

I *Registers D9125 to D9132 record the annunciator

1

D9125

Explanation

~.

iF1 numbers in B I N in the

order In which they occur on a Flrst in Flrst out basis.

*Annunciator numbers are removed from anyplace in the queue b y applying

the

Instruction. Subsequent entries then move u p one

*The annunciator number a t the head of the queue I S cleared by t t e &'

Instruction or INDICATIOR R E S E T and subseauent entries rnovc' u p bv one

place.

*The9thannunciator

number i s ignored until there i s room inthe queue.

~

D9127

.

D9128

Detected

annunciator

numbers

D9129

.

.

.

.

.

.

.

.

*

.

.

.

Records and

queues

detected

annunciattr

numbers

...

D9130

D9131

'

D9132

Table 3.5 Special Register List (Continued)

POINT

I

(1) Special registers marked * above, are latched and their data will remain unchangecl after

normal status i s restored. Clear the registers as follows:

1 ) From the user program

Use the circuit shown on the right and turn on

the

clear

command

contact to clear the register

contents.

I- -

Clear command

{ - I

RST D 9 0 0 5 4

-T-

Specify the registel, t o be reset

2) From the peripheral equipment (PU, GPP,PHP or HGP)

Use the test function to change the present value of the register to 0. For the (operation procedure, refer to the appropriate manual.

3) By movingthe RESET keyswitch

special register is set to "0".

a t the CPU front to

the RESET position,the

/MELSEC

3. SPECIFICATIONS

3.2.4 Instruction list

Instructions available for the A3HCPUprogrammable controller may be classified into sequence

instructions, basic instructions, and application instructions as shown in Table 3.6.

Classification of instructions

Description

Instructions for relay control circuit

Sequence instructions

Comparison instructions

Comparisons such as

Arithmetic instructions

Basic

instructions

BCD * BIN conversion

instructions

>, and <

Addition, subtraction, multiplication, and division

of BIN and BCD

Conversions from BCD to BIN and BIN to BCD

Transfer of specified data

Program branch instructions

Sequence program conditional and unconditional

branch instructions

Display onto indicator on front of CPU unit

Logical operation instructions

Logical operations such a s logical sumand logical product

Rotation instructions

Rotation of specified data

Shift instructions

Shift of specified data

Data processing instructions

I

7

I

Data transfer instructions

Display instructions

Application

instruction

I

=,

Data processing such as 16-bit data search, decode, and encode

F I F O instructions

Read/write of F I F O table

ASCII conversion instruction

Conversion of ASCI I characters into ASCI I code

Special unit instructions

Data transfer to and from special unit

Others

Instructions which are not included in the above classification,

such as WDT reset, and carry flag s e t / r e s e t ,

Table 3.6 Classification of instructions

A list of all the instructions i s given in the following pages in the order given above,

/MELS:EC

3. SPECIFICATIONS

( 1 ) How to use the instruction list.

The instructions listed in Section (2) t o (4) are given in the following format.

1

1-

Valid Devices

0

l

6

0.

. . . Classifies the instruction byapplication.

0.

. . . Indicates whether the instruction processes bit, word or double-word data.

Unit of

Processing

16 bits

3 2 bits

Device

x, y , M ,

1

Number of devices required

L, F, B

Max.

16

points

in

units

of

T,C,D,W,R,AO,Al,Z,V

I

d

-

x, Y , M, L, F, B

4

1 point

of 4

Max. points

32units

in

T, C, D, W, R, AO, Z

2 points

0.. . Indicates the instruction symbol used during programming.

,

The instruction set which operates on numericaldata,

instructions. These may be modified as follows:

isbased on 16 bit dataprocessing

Add a D infront of (or, in some cases, after) the instruction symbol to define if as a 32

bit processing instruction.

Example:

+

t

p+

+

instruction

16-bit

instruction

32-bit

Add a P after the instruction to define it as being operated only by a leading edge in the

preceding contact continuity,

Example:

+I

4

Instruction executed

continuously by

preceding contact

continuity

+P $

F

Instruction executed only a t the

leading edge of preceding contact

continuity,

/MELSEC

3. SPECIFICATIONS

@ . . , , Indicates

-

the symbol used in the ladderdiagramand

instruction.

+

S

I

D

'

the significance of the data in the

d

Indicates destination.

Indicates source.

Indicates instruction symbol.

1

Indicates destination.

-Indicates source.

Indicates instruction symbol.

I

Destination:

Source :

Indicates the destination of the

operation result.

Indicates the source of the data for the operation.

-

@ . . . .Indicates the operation.

I

(D)+(S)+(D)

-Indicates

i

(D+1, D)+(S+l, S)+(D+l, D)

16 bits 16 bits

-Indicates

32 bits.

D+l

16 bits.

! Upper 16 bits

I

~

1

D

Lower 16 bits

D + l or S+l indicates the next device

number after D or S.

I

@ . . . . Indicates the condition

Symbol

No entry

1

of execution for each instruction as described below:

Execution Condition

Instruction is always executed. (i.e. no preceding contact logic)

The instruction is executed continuously all the time that the

contacts preceding i t allow

continuity. As soon as continuity ends, execution of the instruction stopsand it is not

processed.

The instruction is executedonce when continuity from the preceding contacts provides a

leading edge to the instruction "coil". Once the leading edgeis provided, the instruction is

executed Once only, even i f the preceding contact continuity is maintained, until continuity

is broken and then re-established.

The instruction is executed once only when continuity from the preceding contacts provides

a trailing edge to the instruction "coil". Once the trailing edgeis provided, the instruction i s

executed once only, even i f the preceding contact continuity remains broken, until continuity is re-established and then broken,

0,

. .Indicates the number of program steps required for each instruction. The number of steps

,

@

, , ,

changes depending on conditions for full details, refer to the instruction in the programming

manual.

. Indicates which devices may be used as source(s) and/or destination ( D l devices.

@...,A

0

tion.

in a device column, next to S and/or D indicates that the device is valid in that instruc-

/MEL~K

3. SPECIFICATIONS

( 2 ) Sequence instructions

7

22 sequence instructions: lasslfi- ,

:ation P n l t

LDI

!-{I

'

AND

,

-

- I

Valid Devices

IThe first, NIC contact

in a ladder

rung

(or block)

~

Logicai product

( N / O series contact)

~

1

I1 +

I

'

I

ANI

Logical product NOT

(NIC series contact)

Logical sum

i N i O parallel contact)

1

Logical sum NOT

OUT

~

~-e

~

~

c

Device coil

(OUT TIC m u s t include

I

D or K data)

L

Set device

1

MCR

PLF

~

-1 w v

c

+~

4

j

~

I

Master control start

Master control reset

Produces a pulse

lasting one program

scan time from the

specified device.

d z d1

Produces a pulse

lasting

one program

scan time

from the

specified

device

1-bit device shift

1

'u

NOP 1

No operation

-

1

MPS

'1

operations

Return to step 0

Must be wirtten a t the

end of Droaram.

Store result of

preceding

preceding operations

.~

t

t

I

L

t

1

I

1 ---+-+*

c

t

~

~

L

c

MRD,

Read and reset result of

preceding operations

3-21

- ,,,.'.

;r.,

2

/..

3. SPECIFICATIONS

( 3 ) Basic instructions

133 basic instructions:

llassifi

catlon

Jnit

Instruct~on

'

16

h t s

32

h t S

Symbol

,/MELSEC

/MELSEC-A

3, SPECIFICATIONS

ZlassifiJnit

cat ion

-

16

3ltS

-

32

3ltS

-

16

3ltS

-

32

bItS

-

16

h t 5

Instruction

Symbol

Symbol

1

Operation

/MELSEC

3. SPECIFICATIONS

lnstructlon

:lassif i

Unit

cation

Symbol

!

i

Symbol

Operation

I

16

blts

32

bits

16

blts

is1 +1,

s11 + is2+1, S2)

+

iD+l, D!

16

bits

32

bits

T

i

L

/MEL:FA

3. SPECIFICATIONS

Symbol

Valid Dwices

Operation

~

IS1 +1, s1i

iS2t1, S2)

'

-Quot~ent IDt1, Dl,

R e m a n d e l 1Dt3, D.21

-

iD!

4

- I

.~

-

1

-

IDi

I

CCY

E: : t

0

:

m -

c

!

i

r

t

_i_

c

q

I

D+1, D ) - 1

L

-

ID-1, D,

3 '

D

/MELSEC

3. SPECIFICATIONS

Execu-

:lassifi.

cation 1

Symbol

Symbol

tlon

Operation

.n

COndl.

t Ion

~

7

f

~-

a

c

c

t

t

c

I

I

J L

n

,

Valid Devices

~/MELSEC

3. SPECIFICATIONS

assifiation

bni t l

32

t

bits

Instruction

Symbol

Symbol

1 =(

I

DBlN

~

i

DDBBI N

l NP

1 S 1'

~

S

Operation

D

D

,!

t

B I N converslon

I S l t l , S1 ) - + i D t l , D )

'-BCD 10 . 999999991

L

i

/MELSEC

3. SPECIFICATIONS

1-

( 1 ) General data processing by the

instruction involves the following:

Batch write (buffer memory, sequence programs, parameters)

Batch read (buffer memory, sequence programs, parameters)

Monitoring

Test (set, reset)

Remoterun/stop/pause

I

/MELSEC-A

3. SPECIFICATIONS

(4) Application instructions

108 Application instructions:

c

3-29

I

,

.

3. SPECIFICATIONS

/MELSEC

/MELSEC-A

3. SPECIFICATIONS

-

T

:lassifi

lnstructlon

Unit

Symbol

cat Ion

I

~

Symbol

+

I

32

Valid Devices

tion

Co ndi.

Operation

L

"n" blt rotate to rlght

h I S

I

+

c

Carry

40

'5 #16-~1

I

"n" b l t r o t a t e t o l e f t

tL

"n" b l t r o t a t e t o l e f t

Carry

A1

15 16-n

A0

o 15

I

I

I

Carry

"n" b l t r o t a t e t o l e f t

t

t

-

3. SPECIFICATIONS

lassifiation

c

c

/MELSEC

/MELS.EC

-

3. SPECIFICATIONS

All 0 4bits

r

+

/MELSEC

3. SPECIFICATIONS

'

Jnit

Instruction

Operation

Symbol

Symbol

Qndi.

iEtion

:2:.

':I

.I!'

~

II

,,

X Y ". 81F

, L;d

il T C

Devices

Data i s read from

special function unit in

remote station.

. I

Data is written to

special function unit in

remote station.

I

WDT I S reset In

sequence program.

I i WDTP

!

+

I

I

c

!

I ,

4,

t

ti

SLT

I

3

, ,

ti

I

+

SLTR

~_I

parameters is written to

PC memory status

,

I

latch area

~

Resets the status latch 1

and re-enables the

1

instruction.

I

I Data

specified

In

parameters is written to

PC memory sampling

I

trace area

Resets the sampling tracl

and re-enables the

1instruction.

1

I

+

1

I

'

'

'

~1

I

S e t s upduty clock

I M9020

to M9024 only,

are valid for D.

Transfer of any number

of ASCII codes to

specified outouts.

I

-1

r

+

i-

+

1I

I

I+

7

~

Carry f l a g contact

(M9012)I S turned o n

1

4

1

e-

-4

+

I

c

+

c

c

L

c

L

L

L

L

- -+

Transfer of ASCI I

comment data to

specified outputs

The shaded C H G , PR and SEG instructions differ in specifications from those of the A l ( E ) ,

AZ(E), A3( E)CPUs. For further details, see Appendix 1.

/MELsEC-A

-

3. SPECIFICATIONS

3.2.5 Timer processing and accuracy

With continuity in front

of a timer coil, the timer

presentvalueand contact status are' updated

after the execution of the END (or FEND) instruction and the timer contacts close after the timer

has timed out. When the continuity is removed from in front of the timer coil, the present value

is reset to 0 (retentive timers retain their present value andare reset using the RST commijnd), and

the timer contacts open.

If a timer is jumped, as in the example below, after it has started timing, it continues to time even if

the preceding continuity is removed. (This i s because the PC is no longer scanning the jumped program area.)

Jumps to P31 when X2C is switched on

Sequence program

T99 coil i s switched on when X3 is switched

on and the timer begins timing.

U

n i

T~ step 0

Timer present value updated

Timer contact status updated

I f X2C is switched on while X3 is on (i.e. the

timer i s jumped while i t is timing) and ther

X3 is turned off, thetimer will continue'

timing and its contacts turn on after i t has,

timed out.

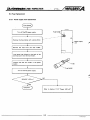

Fig. 3.1 Timer Processing

The timer present value update timing and accuracy in direct and refresh modes are explained on

the following pages.

When the input ( X ) isused as a condition contact in front of the timer coil, accuracy differs between modes. For any other device used as a condition contact, see direct mode processing.

3-35

IB 8hA 6E132-A

/MELSEC

3. SPECIFICATIONS

( 1 ) Present value update timing and accuracy in direct mode

Ladder example

-.

..

T203 contact i s switched

on

6

seconds

after

X0 is s w i t c h e do n .

iT203 i s a l O m s t l m e r . )

Timer timing I

~

Scan t i m e = 25ms

OUT

OUT

0 UT

END

T203

END T203

END

T203

0 UT

T203

END

END

END

X0

T203 coil

T203 c o n t a c t

l O r n s timer timing

T i m i n g s e t a t END

T203 present value

I

I,

l"2

J +I

0

~

i-

'2

0

-1 scan

Fig.

scan

i

-2

-- --