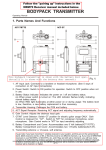

Download GRABADOR DE EPROMs AUT~NOMO

Transcript