Download 三菱QnA版 LtC Soft 機能説明書 TDG 東京電気技術工業株式会社

Transcript

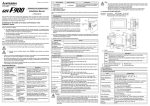

資料 No.0310087 三菱QnA版 LtC Soft 機能説明書 初版 TDG 東京電気技術工業株式会社 はじめに このたびは、当社製品の「三菱 QnA 版ラダープログラム→Cプログラム」へ変換するア プリケーションソフト(以下 LtC Soft と記載します)をご利用頂きありがとうございます。 本書では LtC Soft の仕様と対応コマンドについて解説します。 本書の内容をご理解した上で正しくご利用下さいますようお願い致します。 改訂履歴 日 付 版 改訂履歴 09 年 06 月 1 初版 -1 - 目次 1.概要 .................................................................. -3 2.アプリケーション動作環境............................................... -3 3.インストール方法説明................................................... -3 4.使用制限............................................................... -3 5.ラダープログラム作成時の特殊機能 ....................................... -3 6.ラダープログラム作成時の注意事項 ....................................... -4 7.PLC機種設定説明..................................................... -4 8.三菱QnA版LtC Soft対応コマンド一覧 ............................ -5 1)接点命令 ............................................................ -5 2)結合命令 ............................................................ -5 3)出力命令 ............................................................ -5 4)シフト命令 .......................................................... -6 5)マスタコントロール命令 .............................................. -6 6)終了命令 ............................................................ -6 7)BIN16ビットデータ比較演算命令................................... -6 8)BIN32ビットデータ比較演算命令................................... -6 9)ブロックデータ比較演算命令........................................... -6 10)BIN算術演算命令 ................................................ -6 11)BCD算術演算命令 ................................................ -7 12)ブロック算術演算命令 .............................................. -7 13)インクリメント/デクリメント命令................................... -7 14)BCD変換命令 .................................................... -7 15)BIN変換命令 .................................................... -7 16)2の補数変換命令 .................................................. -7 17)ブロック変換命令 .................................................. -7 18)データ転送命令 .................................................... -7 19)論理演算命令 ...................................................... -8 20)ローテーション命令 ................................................ -8 21)シフト命令 ........................................................ -9 22)ビット処理命令 ................................................... -10 23)繰り返し命令 ..................................................... -10 24)サブルーチン命令 ................................................. -10 25)8→256ビットデコード命令...................................... -10 26)256→8ビットエンコード命令.................................... -10 27)7セグメントデコード ............................................. -10 28)合計値算出命令 ................................................... -10 - -2 - 1.概要 本製品は三菱電機製ラダー作成ツール(以下 GXDeveloper と記載します)で作成し たラダープログラムの内容をCプログラムに変換を実行するアプリケーションツール です。 この変換されたファイルと、TDGシステムプログラム(CPU基板とのインター フェース機能を搭載したライブラリファイル)をリンクしたプログラムであらゆるC PU基板上でラダープログラムを動作する事が可能になります。 2.アプリケーション動作環境 詳細については「LtCTool 取扱説明書.pdf」を御参照下さい。 3.インストール方法説明 LtCTool のインストールCDを実行して下さい。LtC Soft も同時にインストールさ れます。 4.使用制限 LtC Soft は不正使用を防ぐ為、当社からご提供するUSBガードキーをPCに取り 付けずに実行するとエラーが発生し実行出来ません。 必ず実行する時はUSBガードキーを取り付けて実行して下さい。 備考)USBガードーキーを認識する為には、LtCTool インストールCDのアプリケ ーションをインストールする必要があります。 5.ラダープログラム作成時の特殊機能 ①ワードデバイスのビット指定 例) D10.4 ワードレジスタ10のビット4を指定 ②ビットデバイスのワードデバイス指定 a)MOV(P)、DMOV(P)、BMOV(P)命令については以下の機能が対応しています。 ■ワードコマンド XF XE XD XC XB XA X9 X8 X7 X6 X5 X4 X3 X2 X1 X0 K1 の指定範囲 4 点 K2 の指定範囲 8 点 K3 の指定範囲 12 点 K4 の指定範囲 16 点 ■ダブルワードコマンド X1F X1E X1D X1C X1B X1A X19 X18 X17 X16 X15 X14 X13 X12 X11 X10 XF XE XD XC XB XA X9 X8 X7 X6 X5 X4 X3 X2 X1 X0 K1 の指定範囲 4 点 K2 の指定範囲 8 点 K3 の指定範囲 12 点 K4 の指定範囲 16 点 K5 の指定範囲 20 点 K6 の指定範囲 24 点 K7 の指定範囲 28 点 K8 の指定範囲 32 点 注意)コマンドで異なる桁数の計算は出来ません。 -3 - b)上記以外の命令については以下の機能しか対応していません。 ■ワードコマンド XF XE XD XC XB XA X9 X8 X7 X6 X5 X4 X3 X2 X1 X0 K4 の指定範囲 16 点 ■ダブルワードコマンド X1F X1E X1D X1C X1B X1A X19 X18 X17 X16 X15 X14 X13 X12 X11 X10 XF XE XD XC XB XA X9 X8 X7 X6 X5 X4 X3 X2 X1 X0 K8 の指定範囲 32 点 ③インデックスレジスタ修飾 例)MOV K3 Z4 ;Z4に3を代入 MOV K4 1000Z4 ;D1003に4を代入 6.ラダープログラム作成時の注意事項 ①GX−Developerで作成するプログラムは1つのみで名称はデフォルト名 の「MAIN」を必ず使用してください。 《GXDeveloper》 ここの名称は変更しない ②ビットデバイスのワードデバイス指定でビットデバイスの指定を16で割り切れる 値を 指定してください。 例1)Xデバイスの時 X0、X10、X20、X30、 ・・・・・ 例2)Mデバイスの時 M0、M16、M32、M48、 ・・・・・ 備考)MOV(P)、DMOV(P)、BMOV(P)命令はデータの制限はありません。 7.PLC機種設定説明 この LtC Soft は以下の PLC 機種設定で正常動作します。必ず GXDeveloper の初期 設定で以下の設定を行って下さい。 ①メニュー「プロジェクト」→「プロジェクト新規作成」を実行して下さい。ウィンドウが 表示します。 ②設定内容 PCシリーズ:QnACPU PCタイプ:Q2AS(H)S1 プログラム種別:ラダー 備考)GXDeveloper の VER7 と VER8 は動作検証済みです。 -4 - 8.三菱QnA版LtC Soft対応コマンド一覧 三菱版LtC Soft(QnA対応版)が対応している命令を記します。 1)接点命令 No 命令記号 シンボル 内容 1 LD ├┤├─ a接点演算開始 2 LDI ├┤/├─ b接点演算開始 3 AND ├┤├─┤├─ a接点直列接続 4 ANDI ├┤/├─┤/├─ b接点直列接続 5 OR ├┤├┬─ a接点並列接続 ├┤├┘ 6 ORI ├┤/├┬─ b接点並列接続 ├┤/├┘ 7 LDP ├┤↑├─ 立ち上がりパルス演算開始 8 LDF ├┤↓├─ 立ち下がりパルス演算開始 9 ANDP ├┤├─┤↑├─ 立ち上がりパルス直列接続 10 ANDF ├┤├─┤↓├─ 立ち下がりパルス直列接続 11 ORP ├┤ ├┬─ 立ち上がりパルス並列接続 ├┤↑├┘ 12 ORF ├┤ ├┬─ 立ち下がりパルス並列接続 ├┤↓├┘ 2)結合命令 13 ANB 14 ORB ├┤├┬─┬┤├ 回路ブロック直列接続 ├┤├┘ └┤├ ├┤├┬┤├┬─ 回路ブロック並列接続 ├┤├┴┤├┘ 15 MPS ├──┬──── 演算結果プッシュ ├──── └──── 16 MRD ├──┬──── 演算結果読み出し ├──── └──── 17 MPP ├──┬──── 演算結果ポップ ├──── └──── 18 INV ―――/――― 演算結果の反転 19 MEP ―――↑――― 演算結果立上がりパルス化 20 MEF ―――↓――― 演算結果立下がりパルス化 3)出力命令 21 OUT ├┤├──< >┤ アウト命令 22 OUT T ├┤├──< >┤ タイマ 23 OUTH T ├┤├──< >┤ 高速タイマ 24 OUT C ├┤├──< >┤ カウンタ 25 SET ├┤├─[SET ①]┤ デバイスのセット 26 RST ├┤├─[RST ①]┤ デバイスのリセット 27 PLS ├┤├─[PLS ①]┤ 立ち上がり出力 28 PLF ├┤├─[PLF ①]┤ 立ち下がり出力 -5 - 4)シフト命令 29 SFT(P) ├┤├─[SFT ①]┤ ビットデバイスシフト 5)マスタコントロール命令 30 MC ├┤├─[MC n ①]┤ マスタコントロールセット 31 MCR ├┤├─[MCR n]┤ マスタコントロールリセット 6)終了命令 32 FEND ├───[FEND]┤ メインプログラム終了 33 END ├───[END]┤ シーケンスプログラム終了 7)BIN16ビットデータ比較演算命令 34 = ├[= ① ②]───┤ ①=② のとき導通状態 35 <> ├[<> ① ②]──┤ ①<>② のとき導通状態 36 > ├[> ① ②]───┤ ①>② のとき導通状態 37 <= ├[<= ① ②]──┤ ①<=② のとき導通状態 38 < ├[< ① ②]───┤ ①<② のとき導通状態 39 >= ├[>= ① ②]──┤ ①>=② のとき導通状態 8)BIN32ビットデータ比較演算命令 40 D= ├[D= ① ②]───┤ (①、①+1)=(②、②+1)のとき導通状態 41 D<> ├[D<> ① ②]──┤ (①、①+1)<>(②、②+1)のとき導通状態 42 D> ├[D> ① ②]───┤ (①、①+1)>(②、②+1)のとき導通状態 43 D<= ├[D<= ① ②]──┤ (①、①+1)<=(②、②+1)のとき導通状態 44 D< ├[D< ① ②]───┤ (①、①+1)<(②、②+1)のとき導通状態 45 D>= ├[D>= ① ②]──┤ (①、①+1)>=(②、②+1)のとき導通状態 9)ブロックデータ比較演算命令 46 BKCMP(P)= ├[BKCMP= ① ② ③ n]─┤ 47 BKCMP(P)<> ├[BKCMP<> ① ② ③ n]─┤ 48 BKCMP(P)> ├[BKCMP> ① ② ③ n]─┤ ①からn点分のデータと②からn点分のデータを①ワード単位で比較し、比較結果を③で指定し 49 BKCMP(P)<= ├[BKCMP<= ① ② ③ n]─┤ たビットデバイスからn点分に格納する。 50 BKCMP(P)< ├[BKCMP< ① ② ③ n]─┤ 51 BKCMP(P)>= ├[BKCMP>= ① ② ③ n]─┤ 10)BIN算術演算命令 52 +(P) ├[+ ① ②]───┤ ②+① → ② 53 +(P) ├[+ ① ② ③]───┤ ①+② → ③ 54 −(P) ├[− ① ②]───┤ ②−① → ② 55 −(P) ├[− ① ② ③]───┤ ①−② → ③ 56 D+(P) ├[D+ ① ②]───┤ (②+1、②)+(①+1、①) → (②+1、②) 57 D+(P) ├[D+ ① ② ③]───┤ (①+1、①)+(②+1、②) → (③+1、③) 58 D−(P) ├[D− ① ②]───┤ (②+1、②)−(①+1、①) → (②+1、②) 59 D−(P) ├[D− ① ② ③]───┤ (②+1、②)−(①+1、①) → (③+1、③) 60 *(P) ├[* ① ② ③]───┤ ①*② → ③ 61 /(P) ├[/ ① ② ③]───┤ ①/② → 商③、余り③+1 62 D*(P) ├[D* ① ② ③]───┤ (①+1、①)*(②+1、②) → (③+1、③) 63 D/(P) ├[D/ ① ② ③]───┤ 注意.計算結果は 32bit になります。32bit 以上の桁データは破棄になります。 (①+1、①)/(②+1、②) → 商(③+1、③)、余り(③+3、③+2) -6 - 11)BCD算術演算命令 64 B+(P) ├[B+ ① ②]───┤ ②+① → ② 65 B+(P) ├[B+ ① ② ③]───┤ ①+② → ③ 66 B−(P) ├[B− ① ②]───┤ ②−① → ② 67 B−(P) ├[B− ① ② ③]───┤ ①−② → ③ 68 DB+(P) ├[DB+ ① ②]───┤ (②+1、②)+(①+1、①) → (②+1、②) 69 DB+(P) ├[DB+ ① ② ③]───┤ (①+1、①)+(②+1、②) → (③+1、③) 70 DB−(P) ├[DB− ① ②]───┤ (②+1、②)−(①+1、①) → (②+1、②) 71 DB−(P) ├[DB− ① ② ③]───┤ (②+1、②)−(①+1、①) → (③+1、③) 72 B*(P) ├[B* ① ② ③]───┤ ①*② → ③ 73 B/(P) ├[B/ ① ② ③]───┤ ①/② → 商③、余り③+1 12)ブロック算術演算命令 74 BK+(P) ├[BK+ ① ② ③ n]───┤ ①からn点分のデータと②からn点分のデータを一括で加算する。 75 BK−(P) ├[BK− ① ② ③ n]───┤ ①からn点分のデータと②からn点分のデータを一括で減算する。 13)インクリメント/デクリメント命令 76 INC(P) ├[INC ①]───┤ ①+1 → ① 77 DEC(P) ├[DEC ①]───┤ ①−1 → ① 78 DINC(P) ├[DINC ①]───┤ (①+1、①)+1 → (①+1、①) 79 DDEC(P) ├[DDEC ①]───┤ (①+1、①)−1 → (①+1、①) 14)BCD変換命令 80 BCD(P) ├[BCD ① ②]───┤ ① →BCD変換→ ② 《①はBINの0∼9999》 81 DBCD(P) ├[DBCD ① ②]───┤ (①+1、①) →BCD変換→ (②+1、②) 《①はBINの0∼99999999》 15)BIN変換命令 82 BIN(P) ├[BIN ① ②]───┤ ① →BIN変換→ ② 《①はBCDの0∼9999》 83 DBIN(P) ├[DBIN ① ②]───┤ (①+1、①) →BIN変換→ (②+1、②) 《①はBCDの0∼99999999》 16)2の補数変換命令 84 NEG(P) ├[NEG ①]───┤ 85 DNEG(P) ├[DNEG ①]───┤ ① → ① 《①はBINデータ》 ((①+1、①) → (①+1、①) 《①+1、①BINデータ》) 17)ブロック変換命令 86 BKBCD(P) ├[BKBCD ① ② n]───┤ ①からn点分のBINデータを一括でBCDデータに変換し②以降に格納する。 87 BKBIN(P) ├[BKBIN ① ② n]───┤ ①からn点分のBCDデータを一括でBINデータに変換し②以降に格納する。 18)データ転送命令 88 MOV(P) ├[MOV ① ②]───┤ ① → ② 89 DMOV(P) ├[DMOV ① ②]───┤ (①+1、①) → (②+1、②) 90 CML(P) ├[CML ① ②]───┤ 91 DCML(P) ├[DCML ① ②]───┤ 92 BMOV(P) ├[BMOV ① ② n]───┤ ① → ② (①+1、①) → (②+1、②) ① ② n 93 FMOV(P) ├[FMOV ① ② n]───┤ ② ① 94 XCH(P) ├[XCH ① ②]───┤ ① ←→ ② 95 DXCH(P) ├[DXCH ① ②]───┤ (①+1、①) ←→ (②+1、②) -7 - n 96 BXCH(P) ├[BXCH ① ②]───┤ ① ② n 97 SWAP(P) ├[SWAP ① ②]───┤ ① b15 ② b8 b15 b7 b0 b8 b7 b0 19)論理演算命令 98 WAND(P) ├[WAND ① ②]───┤ ② ∧ ① → ② 99 WAND(P) ├[WAND ① ② ③]───┤ ① ∧ ② → ③ 100 DWAND(P) ├[DWAND ① ②]───┤ (②+1、②) ∧ (①+1、①) → (②+1、②) 101 DWAND(P) ├[DWAND ① ② ③]───┤ (①+1、①) ∧ (②+1、②) → (③+1、③) 102 BKAND(P) ├[BKAND ① ② ③ n]───┤ ② ① ③ n ∧ 103 WOR(P) ├[WOR ① ②]───┤ ② ∨ ① → ② 104 WOR(P) ├[WOR ① ② ③]───┤ ① ∨ ② → ③ 105 DWOR(P) ├[DWOR ① ②]───┤ (②+1、②) ∨ (①+1、①) → (②+1、②) 106 DWOR(P) ├[DWOR ① ② ③]───┤ (①+1、①) ∨ (②+1、②) → (③+1、③) 107 BKOR(P) ├[BKOR ① ② ③ n]───┤ ① ② ③ n ∨ 108 WXOR(P) ├[WXOR ① ②]───┤ ② ∀ ① → ② 109 WXOR(P) ├[WXOR ① ② ③]───┤ ① ∀ ② → ③ 110 DWXOR(P) ├[DWXOR ① ②]───┤ (②+1、②) ∀ (①+1、①) → (②+1、②) 111 DWXOR(P) ├[DWXOR ① ② ③]───┤ (①+1、①) ∀ (②+1、②) → (③+1、③) 112 BKXOR(P) ├[BKXOR ① ② ③ n]───┤ ① ② ③ n ∀ 113 WXNR(P) ├[WXNR ① ②]───┤ ② ∀ ① → ② 114 WXNR(P) ├[WXNR ① ② ③]───┤ ① ∀ ② → ③ 115 DWXNR(P) ├[DWXNR ① ②]───┤ (②+1、②) ∀ (①+1、①) → (②+1、②) 116 DWXNR(P) ├[DWXNR ① ② ③]───┤ (①+1、①) ∀ (②+1、②) → (③+1、③) 117 BKXNR(P) ├[BKXNR ① ② ③ n]───┤ ① ② ③ n ∀ 20)ローテーション命令 118 ROR(P) ├[ROR ① n]───┤ b15 119 RCR(P) ├[RCR ① n]───┤ b15 ① b0 SM700 b0 SM700 右へnビットローテーション ① 右へnビットローテーション -8 - 120 ROL(P) ├[ROL ① n]───┤ SM700 b15 ① 121 RCL(P) ├[RCL ① n]───┤ SM700 b15 122 DROR(P) ├[DROR ① n]───┤ b31 ①+1 b16 b15 123 DRCR(P) ├[DRCR ① n]───┤ b31 ①+1 b16 b15 124 DROL(P) ├[DROL ① n]───┤ 125 DRCL(P) ├[DRCL ① n]───┤ b0 左へnビットローテーション ① b0 左へnビットローテーション ① b0 SM700 b0 SM700 右へnビットローテーション ① 右へnビットローテーション SM700 b31 ①+1 b16 b15 ① b0 左へnビットローテーション SM700 b31 ①+1 b16 b15 ① b0 左へnビットローテーション 21)シフト命令 126 SFR(P) ├[SFR ① n]───┤ b15 bn b0 ① b15 b0 SM700 127 SFL(P) ├[SFL ① n]───┤ b15 bn b0 ① b15 b0 SM700 128 BSFR(P) 0∼0 n ├[BSFR ① n]───┤ ① SM700 0 129 BSFL(P) n ├[BSFL ① n]───┤ ① SM700 0 130 DSFR(P) n ├[DSFR ① n]───┤ ① 0 131 DSFL(P) n ├[DSFL ① n]───┤ ① 0 -9 - 22)ビット処理命令 132 BSET(P) ├[BSET ① n]───┤ b15 bn b15 bn b0 ① 1 133 BRST(P) ├[BSET ① n]───┤ b0 ① 1 134 TEST(P) b15 ├[TEST ① ② ③]───┤ b0 ③ ① ②で指定のビット 135 DTEST(P) ├[DTEST ① ② ③]───┤ b31 b0 ③ ① ②で指定のビット 136 BKRST(P) ├[BKRST ① n]───┤ ON OFF ① ① OFF OFF リセット 注意. システム構造上①にタイマデバイス、 カウンタデバイスは指定できません。 ON ON n OFF OFF 23)繰り返し命令 137 FOR ├───[FOR n]┤ 138 NEXT ├───[NEXT]─┤ 139 BREAK ├───[BREAK ① Pn]┤ FOR ∼ NEXTをn回実行する FOR、NEXT命令による繰り返し処理を強制終了し、Pnで指定したポインタに移動します。 ①には、強制終了した時点のFOR、NEXTの繰り返し実行回数の残数を格納します。 24)サブルーチン命令 140 CALL(P) ├[CALL Pn]───┤ 入力条件成立でPnのサブルーチンプラムを実行する。 注意:サブルーチンプログラムへの引数は対応していません。 141 RET ├[RET]───┤ サブルーチンプログラムからの復帰 25)8→256ビットデコード命令 142 DECO(P) ├[DECO ① ② n]───┤ ①で指定されたデバイスの下位nビットをデコードし、その結果を②で指定されたデバイスから n 2 ビットに格納します。 26)256→8ビットエンコード命令 143 ENCO(P) ├[ENCO ① ② n]───┤ ①から2n ビットのデータをエンコードし、②に格納します。 27)7セグメントデコード 144 SEG(P) ├[SEG ① ②]───┤ ①の下位4ビットで指定された0∼Fのデータを7セグメント表示データにデコードし ②に格納します。 28)合計値算出命令 144 WSUM(P) ├[WSUM ① ② n]───┤ ①で指定されたデバイスからn点分の 16 ビットBINデータを全て加算し②で指定した デバイスに格納する。 -10 - お問い合わせ先 電気・電子・コンピュータ応用 東京電気技術工業株式会社 自動制御の総合メーカー 〒152-0031 東京都目黒区中根 2-12-2 TEL03-3723-3631 FAX03-3723-9404 E−mail:[email protected] URL http://www.tdg-net.co.jp -11 -