Download S5U13A05P00C100 Evaluation Board User Manual

Transcript

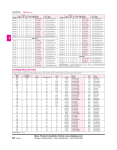

S1D13A05 LCD/USB Companion Chip S5U13A05P00C100 Evaluation Board User Manual Document Number: X40A-G-014-01 Status: Rev 1.01 Issue Date: 2006/11/01 © SEIKO EPSON CORPORATION 2006. All Rights Reserved. Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws. EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners. Rev 1.01 Page 2 Epson Research and Development Vancouver Design Center S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 3 Table of Contents 1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 3 Installation and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 3.1 Configuration DIP Switches . . . . . . . . . . . . . . . . . . . . . . . . . . 7 3.2 Configuration Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 4 CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 4.1 CPU Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . 11 4.2 CPU Bus Connector Pin Mapping . . . . . . . . . . . . . . . . . . . . . . 12 5 LCD Interface Pin Mapping 6 Technical Description . . . . . . . . . . . . . . . . . . . . . . . . . 6.1 PCI Bus Support . . . . . . . . . . . . . . . . . . . . . . 6.2 Direct Host Bus Interface Support . . . . . . . . . . . . . . . 6.3 S1D13A05 Embedded Memory . . . . . . . . . . . . . . . . 6.4 Software Adjustable LCD Backlight Intensity Support Using PWM . . 6.5 LCD Panel Support . . . . . . . . . . . . . . . . . . . . . 6.5.1 LCD Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.5.2 Extended LCD Connector . . . . . . . . . . . . . . . . . . . . . . 6.5.3 TFT Type 3 Extended LCD Connector . . . . . . . . . . . . . . . 6.6 USB Support . . . . . . . . . . . . . . . . . . . . . . . . 6.6.1 USB IRQ Support . . . . . . . . . . . . . . . . . . . . . . . . . . 6.7 External oscillator support for CLKI and CLKI2 . . . . . . . . . . 6.8 External oscillator support for USBCLK . . . . . . . . . . . . . 7 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 7.1 Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 7.2 Document Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 8 Parts List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 9 Schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 16 16 16 16 17 17 17 18 18 18 18 18 10 Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 11 Sales and Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 11.1 Epson Companion Chips (S1D13A05) . . . . . . . . . . . . . . . . . . . . . 30 11.2 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 4 Epson Research and Development Vancouver Design Center S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 5 1 Introduction This manual describes the setup and operation of the S5U13A05P00C100 Evaluation Board. The board is designed as an evaluation platform for the S1D13A05 LCD/USB Companion Chip. This user manual is updated as appropriate. Please check the Epson Research and Development Website at www.erd.epson.com for the latest revision of this document before beginning any development. We appreciate your comments on our documentation. Please contact us via email at [email protected]. S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 6 Epson Research and Development Vancouver Design Center 2 Features Following are some features of the S5U13A05P00C100 Evaluation Board: • 121-pin PFBGA S1D13A05 Embedded Memory LCD Controller with 256K bytes of embedded SRAM. • PCI bus operation through onboard PCI bridge. • CPU/Bus interface header strips for non-PCI bus operation. • Configuration options. • Software adjustable backlight intensity support using PWMOUT. • 4/8-bit 3.3V or 5V single monochrome passive LCD panel support. • 4/8/16-bit 3.3V or 5V single color passive LCD panel support. • 9/12/18-bit 3.3V or 5V active matrix TFT LCD panel support. • Direct interface for 18-bit Sharp HR-TFT LCD panel support. • Direct interface for 18-bit Casio TFT LCD panel support. • Direct interface for 18-bit TFT Type 2 LCD panel support • Direct interface for 18-bit TFT Type 3 LCD panel support • Direct interface for 18-bit TFT Type 4 (Epson ND-TFD) LCD panel support. • Connector for USB client support. • Oscillators for CLKI and CLKI2. S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 7 3 Installation and Configuration The S5U13A05P00C100 is designed to support as many platforms as possible. The S5U13A05P00C100 incorporates a DIP switch and three jumpers which allow both the evaluation board and the S1D13A05 LCD controller to be configured for a specified evaluation platform. 3.1 Configuration DIP Switches The S1D13A05 has seven configuration inputs (CNF[6:0]) which are read on the rising edge of RESET#. In order to configure the S1D13A05 for multiple Host Bus Interfaces an eight-position DIP switch (SW1) is required. The following figure shows the location of DIP switch SW1 on the S5U13A05P00C100. DIP Switch - SW1 Figure 3-1: Configuration DIP Switch (SW1) Location S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 8 Epson Research and Development Vancouver Design Center All S1D13A05 configuration inputs are fully configurable using the eight position DIP switch as described below. Table 3-1: Configuration DIP Switch Settings Switch (SW1) S1D13A05 Signal SW1-5, CNF4, SW1-[3:1] CNF[2:0] SW1-4 SW1-6 SW1-7 SW1-8 CNF3 CNF5 CNF6 - Value on this pin at rising edge of RESET# is used to configure: Closed (On/1) Open (Off/0) Select host bus interface as follows: CNF4 CNF2 CNF1 CNF0 Host Bus Interface 1 0 0 0 SH-4/SH-3 interface, Big Endian 0 0 0 0 SH-4/SH-3 interface, Little Endian 1 0 0 1 MC68K #1, Big Endian 0 0 0 1 Reserved 1 0 1 0 MC68K #2, Big Endian 0 0 1 0 Reserved 1 0 1 1 Generic #1, Big Endian 0 0 1 1 Generic #1, Little Endian 1 1 0 0 Reserved 0 1 0 0 Generic #2, Little Endian 1 1 0 1 RedCap 2, Big Endian 0 1 0 1 Reserved 1 1 1 0 DragonBall, Big Endian 0 1 1 0 Reserved X 1 1 1 Reserved Reserved. Must be set to 1. WAIT# is active high CLKI to BCLK Divide ratio 2:1 Disable PCI bridge for non-PCI host WAIT# is active low CLKI to BCLK divide ratio 1:1 Enable PCI bridge for PCI host = Required settings when using the PCI Bridge FPGA S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 9 3.2 Configuration Jumpers The S5U13A05P00C100 has three jumper blocks which configure various settings on the board. The jumper positions for each function are shown below. Table 3-2: Jumper Summary Jumper JP3 JP4 JP5 Function LCD Panel Voltage PCI_IRQ Disable GP00 Polarity on H3 Position 1-2 +3.3V LCDVCC Enable USB IRQ on PCI Normal (Active High) Position 2-3 +5V LCDVCC — Inverted (Active Low) No Jumper — Disable USB IRQ on PCI GPO0 not sent to H3 = recommended settings JP3 - LCD Panel Voltage JP3 selects the voltage level to the LCD panel. When the jumper is at position 1-2, the voltage level is +3.3V (default setting). When the jumper is at position 2-3, the voltage level is +5.0V. Note When configured for Sharp HR-TFT, JP3 and JP5 must be set to position 1-2. JP3 +3.3 LCDVCC +5 LCDVCC Figure 3-2: Configuration Jumper (JP3) Location S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 10 Epson Research and Development Vancouver Design Center JP4 - PCI_IRQ Enable JP4 selects whether the USB IRQ on PCI is enabled or disabled. When the jumper is at position 1-2, the USB IRQ on PCI is enabled (default setting). When no jumper is installed, the USB IRQ on PCI is disabled. JP4 USB IRQ on PCI enabled USB IRQ on PCI disabled Figure 3-3: Configuration Jumper (JP4) Location JP5 - GPO0 Polarity on H3 JP5 selects the polarity of the GPO0 signal available on the TFT Type 3 Extended LCD Connector H3. When the jumper is at position 1-2, the GPO0 signal is sent directly (active high) to H3 (default setting). When the jumper is at position 2-3, the GPO0 signal is inverted and then sent (active low) to H3. When no jumper is installed, GPO0 is not sent to H3. JP5 Normal (Active High) Inverted (Active Low) GPIO0 not sent to H1 Figure 3-4: Configuration Jumper (JP5) Location S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 11 4 CPU Interface 4.1 CPU Interface Pin Mapping Table 4-1: Host Bus Interface Pin Mapping Generic #2 Hitachi SH-3/SH-4 Motorola MC68K #1 Motorola MC68K #2 Motorola REDCAP2 Motorola MC68EZ328/ MC68VZ328 DragonBall A[17:1] A[17:1] A[17:1] A[17:1] A[17:1] A[17:1] S1D13A05 Pin Name Generic #1 AB[17:1] A[17:1] AB0 A01 A0 A0 DB[15:0] D[15:0] D[15:0] D[15:0] CS# External Decode 1 CSn# M/R# CLKI BS# LDS# A0 A0 A01 D[15:0] D[15:0]2 D[15:0] D[15:0] CSn CSX CLKO External Decode 1 External Decode BUSCLK BUSCLK Connected to IOVDD3 CKIO CLK CLK CLK BS# AS# AS# Connected to IOVDD3 RD/WR# RD1# Connected to IOVDD3 RD/WR# R/W# R/W# R/W Connected to IOVDD3 RD# RD0# RD# RD# Connected to IOVDD3 SIZ1 OE OE WE0# WE0# WE# WE0# Connected to IOVDD3 SIZ0 EB1 LWE WE1# WE1# BHE# WE1# UDS# DS# EB0 UWE DTACK# DSACK1# N/A DTACK RESET# RESET# RESET_OUT RESET WAIT# WAIT# WAIT# WAIT#/ RDY# RESET# RESET# RESET# RESET# Note 1 A0 for these bus interfaces is not used internally by the S1D13A05 and should be connected to VSS. 2 If the target MC68K bus is 32-bit, then these signals should be connected to D[31:16]. 3 These pins are not used in their corresponding host interface mode. Systems are responsible for externally connecting them to IO VDD. S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 12 Epson Research and Development Vancouver Design Center 4.2 CPU Bus Connector Pin Mapping Table 4-2: CPU Bus Connector (H4) Pinout Connector Pin No. Comments 1 Connected to DB0 of the S1D13A05 2 Connected to DB1 of the S1D13A05 3 Connected to DB2 of the S1D13A05 4 Connected to DB3 of the S1D13A05 5 Ground 6 Ground 7 Connected to DB4 of the S1D13A05 8 Connected to DB5 of the S1D13A05 9 Connected to DB6 of the S1D13A05 10 Connected to DB7 of the S1D13A05 11 Ground 12 Ground 13 Connected to DB8 of the S1D13A05 14 Connected to DB9 of the S1D13A05 15 Connected to DB10 of the S1D13A05 16 Connected to DB11 of the S1D13A05 17 Ground 18 Ground 19 Connected to DB12 of the S1D13A05 20 Connected to DB13 of the S1D13A05 21 Connected to DB14 of the S1D13A05 22 Connected to DB15 of the S1D13A05 23 Connected to RESET# of the S1D13A05 24 Ground 25 Ground 26 Ground 27 +12 volt supply 28 +12 volt supply 29 Connected to WE0# of the S1D13A05 30 Connected to WAIT# of the S1D13A05 31 Connected to CS# of the S1D13A05 32 Connected to MR# of the S1D13A05 33 Connected to WE1# of the S1D13A05 34 Connected to +3.3V S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 13 Table 4-3: CPU Bus Connector (H5) Pinout Connector Pin No. Comments 1 Connected to AB0 of the S1D13A05 2 Connected to AB1 of the S1D13A05 3 Connected to AB2 of the S1D13A05 4 Connected to AB3 of the S1D13A05 5 Connected to AB4 of the S1D13A05 6 Connected to AB5 of the S1D13A05 7 Connected to AB6 of the S1D13A05 8 Connected to AB7 of the S1D13A05 9 Ground 10 Ground 11 Connected to AB8 of the S1D13A05 12 Connected to AB9 of the S1D13A05 13 Connected to AB10 of the S1D13A05 14 Connected to AB11 of the S1D13A05 15 Connected to AB12 of the S1D13A05 16 Connected to AB13 of the S1D13A05 17 Ground 18 Ground 19 Connected to AB14 of the S1D13A05 20 Connected to AB15 of the S1D13A05 21 Connected to AB16 of the S1D13A05 22 Connected to AB17 of the S1D13A05 23 Not connected 24 Not connected 25 Ground 26 Ground 27 +5 volt supply 28 +5 volt supply 29 Connected to RD/WR# of the S1D13A05 30 Connected to BS# of the S1D13A05 31 Connected to BUSCLK of the S1D13A05 32 Connected to RD# of the S1D13A05 33 Not connected 34 Not connected S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 14 Epson Research and Development Vancouver Design Center 5 LCD Interface Pin Mapping Table 5-1: LCD Connector (H1) Monochrome Passive Panel Color Passive Panel Color TFT Panel Pin Name H1 Pin No. 4-bit 8-bit 4-bit 8-bit 8-bit 16-Bit 9-bit 12-bit FPDAT0 1 driven 0 D0 driven 0 D0 (B5)1 D0 (G3)1 D0 (R6)1 R2 R3 FPDAT1 3 driven 0 D1 driven 0 D1 (R5)1 D1 (R3)1 D1 (G5)1 R1 FPDAT2 5 driven 0 D2 driven 0 D2 (G4)1 D2 (B2)1 D2 (B4)1 FPDAT3 7 driven 0 D3 driven 0 D3 (B3)1 D3 (G2)1 FPDAT4 9 D0 D4 D0 (R2)1 D4 (R3)1 1 1 Single Single Format 1 D5 (G2) Sharp HR-TFT Casio TFT TFT Type 2 TFT Type 3 TFT Type 4 18-bit 18-bit 18-bit 18-bit 18-bit 18-bit R5 R5 R5 R5 R5 R5 R2 R4 R4 R4 R4 R4 R4 R0 R1 R3 R3 R3 R3 R3 R3 D3 (R4)1 G2 G3 G5 G5 G5 G5 G5 G5 D4 (R2)1 D8 (B5)1 G1 G2 G4 G4 G4 G4 G4 G4 1 D9 (R5)1 G0 G1 G3 G3 G3 G3 G3 G3 Others Format 2 D5 (B1) FPDAT5 11 D1 D5 D1 (B1) FPDAT6 13 D2 D6 D2 (G1)1 D6 (B1)1 D6 (G1)1 D10 (G4)1 B2 B3 B5 B5 B5 B5 B5 B5 FPDAT7 15 D3 D7 D3 (R1)1 D7 (R1)1 D7 (R1)1 D11 (B3)1 B1 B2 B4 B4 B4 B4 B4 B4 FPDAT8 17 driven 0 driven 0 driven 0 driven 0 driven 0 D4 (G3)1 B0 B1 B3 B3 B3 B3 B3 B3 FPDAT9 19 driven 0 driven 0 driven 0 driven 0 driven 0 D5 (B2)1 driven 0 R0 R2 R2 R2 R2 R2 R2 FPDAT10 21 driven 0 driven 0 driven 0 driven 0 driven 0 D6 (R2)1 driven 0 driven 0 R1 R1 R1 R1 R1 R1 FPDAT11 23 driven 0 driven 0 driven 0 driven 0 driven 0 D7 (G1)1 driven 0 driven 0 R0 R0 R0 R0 R0 R0 FPDAT12 25 driven 0 driven 0 driven 0 driven 0 driven 0 D12 (R3)1 driven 0 G0 G2 G2 G2 G2 G2 G2 FPDAT13 27 driven 0 driven 0 driven 0 driven 0 driven 0 D13 (G2)1 driven 0 driven 0 G1 G1 G1 G1 G1 G1 FPDAT14 29 driven 0 driven 0 driven 0 driven 0 driven 0 D14 (B1)1 driven 0 driven 0 G0 G0 G0 G0 G0 G0 FPDAT15 31 driven 0 driven 0 driven 0 driven 0 driven 0 D15 (R1)1 driven 0 B0 B2 B2 B2 B2 B2 B2 FPDAT16 4 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 B1 B1 B1 B1 B1 B1 FPDAT17 6 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 B0 B0 B0 B0 B0 B0 FPSHIFT 33 DCLK CLK CLK CPH FPSHIFT DRDY 35 & 38 driven 0 no connect INV INV DRDY FPSHIFT MOD FPSHIFT2 MOD DRDY FPLINE 37 FPLINE LP GPCK STB LP FPLINE FPFRAME 39 FPFRAME SPS GSRT STV STV FPFRAME GND 2, 8, 14, 20, 26 PWMOUT 28 PWMOUT N/C 30 Not connected LCDVCC 32 LCDVCC (3.3V or 5V) +12V 34 +12V N/C 36 Not Connected GPO02 40 GPO0 (for controlling on-board LCD bias power supply on/off) GND Note 1 These pin mappings use signal names commonly used for each panel type, however signal names may differ between panel manufacturers. The values shown in brackets represent the color components as mapped to the corresponding FPDATxx signals at the first valid edge of FPSHIFT. For further FPDATxx to LCD interface mapping, see S1D13A05 Hardware Functional Specification, document number X40A-A-001-xx. 2 GPO0 can be inverted on H1 by setting JP5 to 2-3. S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 15 Table 5-2: Extended LCD Connector (H2) Color TFT Panel Mono Passive Panels Color Passive Panels Sharp HR-TFT1 Casio TFT1 TFT Type 21 TFT Type 31 18-bit 18-bit 18-bit 18-bit 18-bit PS POL VCLK CPV GPIO0 GPIO0 GPIO1 CLS GRES AP OE GPIO1 GPIO1 GPIO2 Pin Name H2 Pin No. GPIO0 1 GPIO0 GPIO1 3 Others 9-bit 12-bit 18-bit TFT Type 4 USB2 GPIO2 5 GPIO2 REV FRP POL POL GPIO2 GPIO3 7 GPIO3 SPL STH STH EIO GPIO3 GPIO4 9 GPIO4 USBPUP GPIO5 11 GPIO5 USBDETECT GPIO6 13 GPIO6 USBDM GPIO7 15 GPIO7 USBDP GND 2, 4, 6, 8, 10, 12, 14, 16 GPIO3 GND Note 1 If a panel type requiring extra control signals is selected (REG[0Ch] or REG[48h]), GPIO[3:0] are used for the required signals. This leaves GPIO[7:4] available for USB support or as GPIOs. 2 If USB support is enabled (REG[4000h] bit 7 = 1b), GPIO[7:4] are used by the USB interface. GPIO[3:0] remain available for extended panel interface support (HR-TFT, Casio or Type 2/3/4 TFT) or as GPIOs. Table 5-3: TFT Type 3 Extended LCD Connector (H3) Pin Name H3 Pin number TFT Type 3 All Other LCD Display Modes GPO0 1 GPO0 GPO0 GPO1 3 VCOM GPO1 GPO2 5 XOEV GPO2 GPO3 7 CMD GPO3 GPO4 9 PCLK1 GPO4 GPO5 11 PCLK2 GPO5 GPO6 13 XRESH GPO6 GPO7 15 XRESV GPO7 GPO8 17 XOHV GPO8 GPO9 19 XSTBY GPO9 GPO10 21 PMDE GPO10 NC 23 - NC 25 - GND 2-26 Even Numbers GND S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 16 Epson Research and Development Vancouver Design Center 6 Technical Description 6.1 PCI Bus Support The S1D13A05 does not have on-chip PCI bus interface support. The S1D13A05P00C100 uses the on-board PCI Bridge FPGA to support the PCI bus. 6.2 Direct Host Bus Interface Support The S5U13A05P00C100 is specifically designed to work using the PCI Bridge FPGA in a standard PCI bus environment. However, the S1D13A05 directly supports many other host bus interfaces. Connectors H4 and H5 provide the necessary IO pins to interface to these host buses. For further information on the host bus interfaces supported, see “CPU Interface” on page 11. Note If a direct host bus interface is used, the PCI Bridge FPGA must be disabled using SW1-8. 6.3 S1D13A05 Embedded Memory The S1D13A05 has 256K bytes of embedded SRAM. The 256K byte display buffer address space is directly and contiguously available through the 18-bit address bus. 6.4 Software Adjustable LCD Backlight Intensity Support Using PWM The S1D13A05 provides Pulse Width Modulation output on PWMOUT. PWMOUT can be used to control LCD panels which support PWM control of the backlight inverter. The PWMOUT signal is provided on LCD Connector H1. S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 17 6.5 LCD Panel Support The S1D13A05 directly supports: • Single-panel, single drive passive displays. • 4/8-bit monochrome interface. • 4/8/16-bit color interface. • Active Matrix TFT interface. • 9/12/18-bit interface. • Direct support for 18-bit Sharp HR-TFT LCD panel. • Direct support for 18-bit Casio TFT LCD panel. • Direct support for 18-bit TFT Type 2 LCD panel. • Direct support for 18-bit TFT Type 3 LCD panel. • Direct support for 18-bit TFT Type 4 (Epson ND-TFD) LCD panel. All the necessary signals are provided on the 40-pin LCD Connector H1, 16-pin Extended LCD Connector H2, and the 26-pin TFT Type 3 Extended LCD Connector H3. For detailed connection information, see Section 5, “LCD Interface Pin Mapping” on page 14. S5U13A05P00C100 does not provide a power supply for the LCD bias voltage needed by Passive LCD panels. An external power supply is required to provide the bias LCD voltage to the LCD panel. 6.5.1 LCD Connector The LCD Connector H1 provides all LCD panel signals required for Active Matrix TFT. For Passive LCD panels, all the signals are provided except the LCD bias voltage (an external power supply for the LCD bias voltage is required for Passive LCD panels). These signals are buffered to either a 3.3V level or a 5.0V level depending on the setting of JP3. See Table 3-2: “Jumper Summary” on page 9. 6.5.2 Extended LCD Connector The S1D13A05 directly supports several extended panel types such as the Sharp 18-bit HRTFT, Casio TFT and compatible panels. The Extended LCD Connector H2 provides the extra signals required to support these panels. The signals on this connector are provided directly from the S1D13A05 without any buffering and are 3.3V signals. S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 18 Epson Research and Development Vancouver Design Center 6.5.3 TFT Type 3 Extended LCD Connector The S1D13A05 directly supports 18-bit TFT Type 3 compatible panels. The TFT Type 3 Extended LCD Connector H3 provides the extra signals required to support panels compatible with the specified timings. The signals on this connector are provided directly from the S1D13A05 without any buffering and are 3.3V signals. 6.6 USB Support The S1D13A05 USB controller provides a Revision 1.1 compliant USB client. The S1D13A05 acts as a USB device and connects to an upstream hub or USB host through connector J1 on the S5U13A05P00C100 evaluation board. Clamping diodes have been added to protect the USB bus from ESD and shorting. 6.6.1 USB IRQ Support The S1D13A05 supports interrupts using the output pin, IRQ. In order to support interrupts from the USB client of the S1D13A05, the S5U13A05P00C100 evaluation board connects IRQ to PCI interrupt INTA# from the PCI slot. The IRQ pin output to the PCI bus can be disabled by removing jumper JP4. 6.7 External oscillator support for CLKI and CLKI2 The S1D13A05 uses CLKI and CLKI2 signals provided by two +3.3V oscillator. The oscillator are mounted in 14-pin DIP sockets on the board. 6.8 External oscillator support for USBCLK The S1D13A05 can use a 48MHz oscillator for the USBCLK source, instead of the USB crystal oscillating circuit. A +3.3V supplied 14-pin DIP package sized oscillator slot is present on the board. Note The board supports either an external crystal or an external oscillator for USB functionality. Only one can be enabled at a time. If an external crystal is used for the clock source for the USB module, the USBCLK input needs to be disabled by using a pulldown resistor and removing the oscillator or clock source. If an oscillator or another type of clock external source is used, USBOCSI needs to be disabled by using a pulldown resistor and disabling or removing the crystal oscillator circuitry. S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 19 7 References 7.1 Documents • Epson Research and Development, Inc., S1D13A05 Hardware Functional Specification, document number X40A-A-001-xx. • Epson Research and Development, Inc., S1D13A05 Programming Notes and Examples, document number X40A-G-003-xx. 7.2 Document Sources • Epson Research and Development: http://www.erd.epson.com. S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 20 Epson Research and Development Vancouver Design Center 8 Parts List Table 8-1: Parts List Item Part Description Manufacturer / Part No. / Assembly Instructions Qty Reference 1 19 C1,C2,C3,C4,C5,C6,C7,C 8,C9,C10,C11, C12,C13,C15,C18,C19,C 22,C24,C28,C31, C33,C35,C36,C37,C38 0.1uF CAP 0.10UF 16V CERAMIC X7R 0805 2 2 C20,C21 6.8pF 6.8PF 50V CERM CHIP CAP Panasonic ECU-V1H6R8DCM SMD 1206 or equivalent capacitor 3 5 C23,C29,C32,C34,C49,C 50,C51 4 9 C39,C40,C41,C42,C43,C 44,C45,C46,C47 5 2 C48, C52 6 2 D1, D2 7 1 H1 8 1 9 KEMET C0805C104K4RACTU or equivalent capacitor. Do not populate C11, C12, C13, C15, C24, C28 68uF 10V Tantalum D-Size, 68uF,10V, +/-10% Kemet T491D686K010AS (altern -Panasonic ECST1AD686R (Digikey). Do not populate C23, C29. 0.22uF Ceramic Chip 0.22uF, 50V, X7R +/-5%, 1206 pckg Kemet C1206C224J5RAC or equivalent capacitor 33uF 20V Tantalum D-Size, 33uF,20V, +/-10% Kemet T491D336K020AS (altern -Panasonic ECST1AD686R (Digikey) Ultra high-speed switching diode Rohm BAV99 HEADER 20X2 20x2, shrouded header, keyed, straight Samtec TST-120-01-G-D H2 HEADER 8X2 8x2, shrouded header, keyed, Samtec TST-108-01-G-D straight 1 H3 HEADER 13X2 13x2, shrouded header, keyed, straight Samtec TST-113-01-G-D 10 2 H5, H4 HEADER 17X2 17x2, 0.1” pitch, .025” sq. unshrouded header Thomas&Betts P/N:609-3407 (altern. Samtec TSW-117-05G-D) or equiv. 11 2 JP3,JP5 HEADER 3 3x1, 0.1” pitch unshrouded header 12 1 JP4 HEADER 2 2x1, 0.1” pitch unshrouded header 13 1 J1 USB B Connector 14 1 L2 Ferrite 15 13 R1,R2,R3,R4,R5,R6,R7,R 9,R29, R32,R33,R34,R35 15K 5% 0805 Resistor, 15K, 5% 16 0 R12 15K 5% 0805 Resistor, 15K, 5% 17 1 R10 1M 0805 0805 Resistor, 1M, 1% 18 1 R11 470R 0805 19 3 R30,R31,R36 20 1 R28 100K 5% 1206 Resistor, 100K, 5% 21 1 R22 1.5K 1% 1206 Resistor, 1.5K, 1% BAV99 1K 5% Right Angle, Type B USB Connector AMP 787780-1 Ferrite Bead Steward 28F0181-ISR-10 (Digikey P/N: 240-2511-1-ND) Do not populate. 0805 Resistor, 470R, 1% 1206 Resistor, 1K, 5% S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 21 Table 8-1: Parts List Reference Part Description Manufacturer / Part No. / Assembly Instructions Item Qty 22 1 R23 150K 1% 1206 Resistor, 150K, 1% 23 2 R27,R24 301K 1% 1206 Resistor, 301K, 1% 24 2 R26,R25 20 1% 25 1 SW1 SW DIP-8 Dip Switch 8-Position 26 0 SW2 SW DIP-4 Dip Switch 4-Position Do not populate. 27 0 TP1 HEADER 1 1x1, 0.1” pitch unshrouded header Do not populate. 28 1 U1 S1D13A05B00B 121 pin PFBGA 13A05 LCD Controller 29 3 U5,U6,U7 1206 Resistor 20 Ohm, 1% Test Socket 30 1 U11 ADP3338AKCZ2.5RL7 31 1 U12 LT1117CM-3.3 32 3 U13,U15,U16 33 1 U14 34 1 U17 35 1 (U18) 36 1 37 74HCT244 14 pin narrow DIP, screw machine socket 2.5V fixed voltage regulator, SOT-223 Analog Devices ADP3338AKCZ-2.5RL7 (Digikey P/N: ADP3338AKCZ2.5RL7CT-ND) 3.3V fixed voltage regulator, 3 Linear Technology Lead Plastic DD LT1117CM-3.3 Buffer, SO-20 package 74AHC1G125/SOT- Single Bus Buffer Gate With 23 3-State Output TI74HCT244 or equivalent Texas Instruments SN74AHC1G125DBVR TQFP 144 pin FLEX 6000 FPGA Altera EPF6016TC144-2 EPC1PI8N 8-pin DIP package, OTP EPROM (Socketed) Altera EPC1PI8N, Socketed U18 Socket 8-pin narrow DIP, screw machine socket Socket for U18 1 Y2 48MHz 48MHz SMD XTAL EPSON FA-238 Series 48MHz Fundamental Crystal 38 3 (JP3-JP5) Shunts Jumper Shunts 39 1 Z1 PCI bracket PCI bracket with slot for USB Type B conn 40 2 Z2 Pan Head Screw Screw, pan head, #4-40 x 1/4” 41 2 Resistor SMD 0805 0ohm 42 1 (U6) 50MHz Oscillator DIP14, 50MHz Epson SG8002DB, 50MHz, socketed 43 1 (U7) 6.5MHz Oscillator DIP14, 6.5MHz Epson SG8002DB, 6.5MHz, socketed EPF6016TC144-2 0 0805 Resistor, 0 ohm S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 S1D13A05 X40A-G-014-01 Rev 1.01 A B C D CS# M/R# BS# RD# WE0# WE1# RD/WR# RESET# WAIT# USBOSCI USBOSCO CLKI CLKI2 USBCLK DB[15:0] AB[17:0] DB[15:0] AB[17:0] 5 5 DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 DB8 DB9 DB10 DB11 DB12 DB13 DB14 DB15 AB0 AB1 AB2 AB3 AB4 AB5 AB6 AB7 AB8 AB9 AB10 AB11 AB12 AB13 AB14 AB15 AB16 AB17 K2 F2 B2 G5 F9 K10 B10 E7 NC L1 NC A1 NC A8 NC L11 NC A11 E4 E3 E2 E1 E5 F4 F3 F1 G1 B1 C1 F5 B9 J8 L5 K5 J5 L4 K4 J4 J3 L3 K3 J2 H3 H2 H1 H4 G3 G2 D1 D2 D3 C3 A3 B3 C4 A4 D4 C5 B5 A5 D5 E6 B6 A6 C6 D6 VSS VSS VSS VSS VSS VSS VSS TESTEN NC NC NC NC NC CS# M/R# BS# RD# WE0# WE1# RD/WR# RESET# WAIT# USBOSCI USBOSCO CLKI CLKI2 USBCLK DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 DB8 DB9 DB10 DB11 DB12 DB13 DB14 DB15 AB0 AB1 AB2 AB3 AB4 AB5 AB6 AB7 AB8 AB9 AB10 AB11 AB12 AB13 AB14 AB15 AB16 AB17 U1 C2 A2 L10 J10 H6 L9 A10 F11 G4 L2 K1 J1 H5 J6 F6 H8 K11 J11 C11 B11 B4 H7 G6 K6 L6 K8 A9 4 GPO0 GPO1 GPO2 GPO3 GPO4 GPO5 GPO6 GPO7 GPO8 GPO9 GPO10 FPDAT0 FPDAT1 FPDAT2 FPDAT3 FPDAT4 FPDAT5 FPDAT6 FPDAT7 FPDAT8 FPDAT9 FPDAT10 FPDAT11 FPDAT12 FPDAT13 FPDAT14 FPDAT15 FPDAT16 FPDAT17 H11 G8 G9 G10 G11 G7 F8 F10 F7 E8 E11 E10 E9 D8 D11 D10 D9 C10 J9 H9 H10 K9 L8 J7 K7 L7 CNF0 CNF1 CNF2 CNF3 CNF4 CNF5 CNF6 A7 B7 C7 D7 B8 C8 C9 S1D13A05B00B COREVDD COREVDD COREVDD COREVDD IOVDD IOVDD IOVDD IOVDD IOVDD IOVDD GPO0 GPO1 GPO2 GPO3 GPO4 GPO5 GPO6 GPO7 GPO8 GPO9 GPO10 GPIO4 GPIO5 GPIO6 GPIO7 IRQ PWMOUT FPRAME FPLINE FPSHIFT DRDY GPIO0 GPIO1 GPIO2 GPIO3 FPDAT0 FPDAT1 FPDAT2 FPDAT3 FPDAT4 FPDAT5 FPDAT6 FPDAT7 FPDAT8 FPDAT9 FPDAT10 FPDAT11 FPDAT12 FPDAT13 FPDAT14 FPDAT15 FPDAT16 FPDAT17 CNF0 CNF1 CNF2 CNF3 CNF4 CNF5 CNF6 4 +2.5V +3.3V +3.3V FPDAT[17:0] CNF[6:0] GPIO4 GPIO5 GPIO6 GPIO7 IRQ GPO[10:0] PWMOUT FPFRAME FPLINE FPSHIFT DRDY GPIO0 GPIO1 GPIO2 GPIO3 FPDAT[17:0] CNF[6:0] 3 3 CNF[6:0] C1 0.1uF C2 0.1uF C3 0.1uF CNF0 CNF1 CNF2 CNF3 CNF4 CNF5 CNF6 C4 0.1uF 15K 5% R1 2 +3.3V 15K 5% R4 C6 0.1uF 15K 5% R3 C5 0.1uF 15K 5% R2 2 Date: Size B Title 15K 5% R5 C7 0.1uF 15K 5% R7 C8 0.1uF SW DIP-8 16 15 14 13 12 11 10 9 C9 0.1uF Wednesday, February 27, 2002 Document Number <Doc> 1 Sheet S5U13A05P00C100 - S1D13A05B00B / DIP SW 15K 5% R6 1 2 3 4 5 6 7 8 SW1 1 1 +2.5V of C10 0.1uF nCONFIG +3.3V 6 Rev 1.0 A B C D Page 22 Epson Research and Development Vancouver Design Center 9 Schematics Figure 9-1: S1D13A05P00C100 Schematics (1 of 6) S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 5 Test Socket GND VCC U7 OUT NC Test Socket GND 8 1 OUT NC BUSCLK 8 1 4 CLKI2 CLKI 3 C18 0.1uF Not Populated USBOSCI +3.3V NC OUT C20 7pF Not Populated Test Socket GND VCC U5 R12 15K 5% 7 14 1 4 Y2 8 1 USB Oscillator Socket 2 48MHz 1M 0805 R10 2 3 R9 15K 5% Date: Size B Title C21 7pF USBOSCO S5U13A05P00C100 - Clocks R11 470R 0806 USBCLK Sheet 1 2 of 6 Rev 1.0 C D Monday, October 02, 2006 Document Number <Doc> 1 A 7 14 7 VCC U6 2 A C22 0.1uF C19 0.1uF 14 3 B +3.3V +3.3V 4 B C D 5 Epson Research and Development Vancouver Design Center Page 23 Figure 9-2: S1D13A05P00C100 Schematics (2 of 6) S1D13A05 X40A-G-014-01 S1D13A05 X40A-G-014-01 Rev 1.01 A B C 5 +5V C31 0.1uF 3 VIN U11 RC1117S25T ADJ 1 VOUT 2 4 4 + C32 68uF 10V +2.5V +5V C33 0.1uF 3 3 VIN U12 LT1117CM-3.3 3 ADJ 1 VOUT 2 + +3.3V C34 68uF 10V HEADER 3 JP3 2 LCDVCC +5V 2 1- 2 3.3V LCD Panels 2- 3 5.0V LCD Panels 1 2 3 D 5 Date: Size B Title Monday, October 02, 2006 Document Number <Doc> S5U13A05P00C100 - Power Supplies 1 Sheet 1 3 of 6 Rev 1.0 A B C D Page 24 Epson Research and Development Vancouver Design Center Figure 9-3: S1D13A05P00C100 Schematics (3 of 6) S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 A B C GPO0 5 13 +3.3V FPDAT[17:0] 14 7 Rev 1.01 1 2 3 12 HEADER 3 74AHC04 U3F JP5 FPFRAME FPLINE DRDY FPSHIFT PWMOUT FPDAT[17:0] 1 19 2 4 6 8 11 13 15 17 1 19 2 4 6 8 11 13 15 17 74HCT244 1G 2G 1A1 1A2 1A3 1A4 2A1 2A2 2A3 2A4 U16 74HCT244 1G 2G 1A1 1A2 1A3 1A4 2A1 2A2 2A3 2A4 U15 74HCT244 1G 2G 4 GPO0 to LCD Connector 1-2 Non-Inverted 2-3 Inverted FPDAT16 FPDAT17 FPDAT8 FPDAT9 FPDAT10 FPDAT11 FPDAT12 FPDAT13 FPDAT14 FPDAT15 1 19 U13 1A1 1A2 1A3 1A4 2A1 2A2 2A3 2A4 VCC GND 1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4 VCC GND 1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4 VCC GND 1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4 20 10 18 16 14 12 9 7 5 3 20 10 18 16 14 12 9 7 5 3 20 10 18 16 14 12 9 7 5 3 BFPDAT16 BFPDAT17 BFPDAT8 BFPDAT9 BFPDAT10 BFPDAT11 BFPDAT12 BFPDAT13 BFPDAT14 BFPDAT15 BFPDAT0 BFPDAT1 BFPDAT2 BFPDAT3 BFPDAT4 BFPDAT5 BFPDAT6 BFPDAT7 GPO[10:0] C38 0.1uF LCDVCC C37 0.1uF LCDVCC C35 0.1uF LCDVCC H1 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 H2 2 4 6 8 10 12 14 16 GPO0 GPO1 GPO2 GPO3 GPO4 GPO5 GPO6 GPO7 GPO8 GPO9 GPO10 1 3 5 7 9 11 13 15 17 19 21 23 25 H3 2 4 6 8 10 12 14 16 18 20 22 24 26 HEADER 8X2 Extended LCD Connector 1 3 5 7 9 11 13 15 HEADER 20X2 Primary LCD Connector 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 BFPDAT[17:0] 3 HEADER 13X2 TFT Type 3 Extended LCD Connector GPIO0 GPIO1 GPIO2 GPIO3 GPIO4 GPIO5 GPIO6 GPIO7 BFPDAT0 BFPDAT1 BFPDAT2 BFPDAT3 BFPDAT4 BFPDAT5 BFPDAT6 BFPDAT7 BFPDAT8 BFPDAT9 BFPDAT10 BFPDAT11 BFPDAT12 BFPDAT13 BFPDAT14 BFPDAT15 BFPDAT16 BFPDAT17 LCDVCC +12V 2 IRQ IRQ +3.3V USBDP GPIO6 GPIO7 USBDM +3.3V Date: Size B 1 R26 20 1% 4 U14 R23 R22 1.5K 1% 150K 1% Tuesday, October 03, 2006 Document Number <Doc> 1 Sheet GPIO5 4 L2 Ferrite of 6 USB B Connector VBus DM DP GND J1 R24 301K 1% 1 2 3 4 C36 0.1uF For U15 +3.3V PCI_IRQ USBDETECT HEADER 2 JP4 1 74AHC1G125/SOT-23 R27 301K 1% 2 1 S5U13A05P00C100 - LCD/USB Connectors BAV99 D2 1 GPIO4 USBPUP HEADER 1 TP1 +3.3V R25 20 1% 1 10 D1 BAV99 74AHC04 U3E Title 2 2 11 +3.3V 14 7 2 4 6 8 11 13 15 17 2 1 2 3 5 3 FPDAT0 FPDAT1 FPDAT2 FPDAT3 FPDAT4 FPDAT5 FPDAT6 FPDAT7 4 3 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 3 D 5 Rev 1.0 A B C D Epson Research and Development Vancouver Design Center Page 25 Figure 9-4: S1D13A05P00C100 Schematics (4 of 6) S1D13A05 X40A-G-014-01 1 2 3 C/BE3# IDSEL C/BE2# FRAME# IRDY# TRDY# DEVSEL# STOP# PERR# SERR# PAR C/BE1# C/BE0# AD[31:0] RST# CLK A AD28 AD27 AD26 AD31 AD30 AD29 AB17 AD[31:0] IO1 IO2 IO3 nCE GND Vccint Vccio IO8 IO9 IO10 IO11 IO12 IO13 IO14 IO15 IO16 I17 GND Vccio I20 IO21 IO22 IO23 IO24 IO25 IO26 IO27 IO28 IO29 GND Vccint Vccio MSEL IO34 IO35 IO36 AD25 AD24 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 AB13 AB12 AB11 AB10 AB9 AB8 AB7 AB6 AB5 AB4 AB3 AB2 AB1 AB0 AD23 AD22 AD21 AD20 AD19 AD18 AD17 AD16 AB14 AB15 AB16 B nSTATUS U17 DATA nSTATUS +5V DCLK +3.3V DATA B DB11 DB10 DB13 DB12 DB15 DB14 DCLK 144 143 142 141 140 139 138 137 136 135 134 133 132 131 130 129 128 127 126 125 124 123 122 121 120 119 118 117 116 115 114 113 112 111 110 109 DB[15:0] AB[17:0] C 108 107 106 105 104 103 102 101 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 74 73 C AD5 AD6 AD7 AD0 AD1 AD2 AD3 AD4 DB0 DB2 DB1 DB6 DB5 DB4 DB3 DB9 DB8 DB7 CONF_DONE EPF6016TC144-2 IO108 IO107 IO106 CONF_DONE Vccio Vccint GND IO101 IO100 IO99 IO98 IO97 IO96 IO95 IO94 IO93 I92 Vccio GND I89 IO88 IO87 IO86 IO85 IO84 IO83 IO82 IO81 IO80 IO79 Vccio Vccint GND IO75 IO74 IO73 IO144 IO143 IO142 IO141 IO140 IO139 IO138 IO137 IO136 IO135 IO134 IO133 IO132 IO131 IO130 IO129 DCLK Vccio GND DATA IO124 IO123 IO122 IO121 IO120 IO119 IO118 IO117 IO116 IO115 IO114 IO113 IO112 IO111 IO110 IO109 IO37 IO38 IO39 IO40 IO41 IO42 IO43 IO44 IO45 IO46 IO47 IO48 IO49 IO50 IO51 IO52 nCONFIG GND Vccio nSTATUS IO57 IO58 IO59 IO60 IO61 IO62 IO63 IO64 IO65 IO66 IO67 IO68 IO69 IO70 IO71 IO72 AD15 AD14 AD13 AD12 AD11 AD10 AD9 Rev 1.01 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 S1D13A05 X40A-G-014-01 AD8 4 A +5V R36 1K 5% R32 15K 5% CONF_DONE R28 100K 5% R33 15K 5% nCONFIG D SW DIP-4 SW2 +5V 8 7 6 5 R30 1K 5% 1 2 3 4 U18 EPC1441PC8 DATA VCC VCC DCLK nCASC OE nCS GND 0.22uF 0.22uF Date: Size B +3.3V +5V 0.22uF C46 0.22uF C42 +3.3V E E Sheet 0.22uF C47 0.22uF C43 +5V +5V +5V Wednesday, February 27, 2002 Document Number <Doc> S5U13A05P00C100 - FPGA C45 0.22uF 0.22uF C44 C41 +3.3V +5V C40 Title 8 7 6 5 FPGA configuration EPROM R31 1K 5% +5V +5V +5V +5V +5V +3.3V +5V Do Not Populate 1 2 3 4 DATA DCLK nSTATUS CONF_DONE DB[15:0] R35 R34 15K 5% 15K 5% DATA DCLK nSTATUS CONF_DONE R29 15K 5% +3.3V AB[17:0] BUSCLK RD# BS# RD/WR# WE1# M/R# CS# WAIT# WE0# RESET# D 0.22uF C39 5 of 6 Rev 1.0 Place one on each +3.3V Power Pin of U19 Place one on each +5V Power Pin of U19 +5V 1 2 3 4 Page 26 Epson Research and Development Vancouver Design Center Figure 9-5: S1D13A05P00C100 Schematics (5 of 6) S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 A B C D C/BE0# PAR STOP# TRDY# FRAME# IDSEL RST# PCI_IRQ AD[31:0] 5 5 AD2 AD0 AD6 AD4 AD9 AD13 AD11 AD15 AD18 AD16 AD22 AD20 AD24 AD28 AD26 AD30 52 53 54 55 56 57 58 59 60 61 62 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 1 2 3 4 5 6 7 8 9 10 11 PCI-A C/BE0# +3.3V AD6 AD4 GND AD2 AD0 +VI/O REQ64# +5V +5V Place close to PCIB pin 5 & 6 PCI-B 68uF 10V + C51 +5V 4 52 53 54 55 56 57 58 59 60 61 62 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 1 2 3 4 5 6 7 8 9 10 11 33uF 20V + C52 +12V +5V Place close to PCIA pin 2 AD8 AD7 +3.3V AD5 AD3 GND AD1 +VI/O ACK64# +5V +5V RESERVED GND CLK GND REQ# +VI/O AD31 AD29 GND AD27 AD25 +3.3V C/BE3# AD23 GND AD21 AD19 +3.3V AD17 C/BE2# GND IRDY# +3.3V DEVSEL# GND LOCK# PERR# +3.3V SERR# 3.3V C/BE1# AD14 GND AD12 AD10 GND -12V TCK GND TDO +5V +5V INTB# INTD# PRSNT#1 RESERVED PRSNT#2 PCIB1 Place close to PCIB pin 61 & 62 RESERVED RST# +VI/O GNT# GND RESERVED AD30 +3.3V AD28 AD26 GND AD24 IDSEL +3.3V AD22 AD20 GND AD18 AD16 +3.3V FRAME# GND TRDY# GND STOP# +3.3V SDONE SBO# GND PAR AD15 +3.3V AD13 AD11 GND AD9 TRST# +12V TMS TDI +5V INTA# INTC# +5V RESERVED +VI/O RESERVED PCIA1 68uF 10V + C50 +5V +5V +12V AD[31:0] 4 AD1 AD5 AD3 AD8 AD7 AD12 AD10 AD14 AD17 AD21 AD19 AD23 AD27 AD25 AD31 AD29 3 3 C/BE1# SERR# PERR# DEVSEL# IRDY# C/BE2# C/BE3# CLK AB[17:0] DB[15:0] 2 RD/WR# BUSCLK WE0# CS# WE1# RESET# DB[15:0] 2 +5V +12V Date: Size B Title AB14 AB16 AB8 AB10 AB12 AB0 AB2 AB4 AB6 DB12 DB14 DB8 DB10 DB4 DB6 DB0 DB2 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 HEADER 17X2 H5 HEADER 17X2 H4 +5V +12V AB15 AB17 AB9 AB11 AB13 AB1 AB3 AB5 AB7 DB13 DB15 DB9 DB11 DB5 DB7 DB1 DB3 Wednesday, February 27, 2002 Document Number <Doc> 1 BS# RD# 6 + +5V + +12V WAIT# M/R# +3.3V Sheet S5U13A05P00C100 - Host Bus Connectors 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 1 of 6 C49 68uF 10V C48 33uF 20V Rev 1.0 A B C D Epson Research and Development Vancouver Design Center Page 27 Figure 9-6: S1D13A05P00C100 Schematics (6 of 6) S1D13A05 X40A-G-014-01 Page 28 Epson Research and Development Vancouver Design Center 10 Board Layout Figure 10-1: S5U13A05P00C100 Board Layout (Top View) S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 29 Figure 10-2: S5U13A05P00C100 Board Layout (Bottom View) S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01 Page 30 Epson Research and Development Vancouver Design Center 11 Sales and Technical Support 11.1 Epson Companion Chips (S1D13A05) Japan Seiko Epson Corporation IC International Sales Group 421-8, Hino, Hino-shi Tokyo 191-8501, Japan Tel: 042-587-5812 Fax: 042-587-5564 http://www.epson.co.jp/ North America Epson Electronics America, Inc. 2580 Orchard Parkway San Jose, CA 95131, USA Tel: (408) 922-0200 Fax: (408) 922-0238 http://www.eea.epson.com/ Taiwan Epson Taiwan Technology & Trading Ltd. 14F, No. 7 Song Ren Road Taipei 110, Taiwan, ROC Tel: 02-8786-6688 Fax: 02-8786-6677 http://www.epson.com.tw/ Hong Kong Epson Hong Kong Ltd. 20/F., Harbour Centre 25 Harbour Road Wanchai, Hong Kong Tel: 2585-4600 Fax: 2827-4346 http://www.epson.com.hk/ Europe Epson Europe Electronics GmbH Riesstrasse 15 80992 Munich, Germany Tel: 089-14005-0 Fax: 089-14005-110 http://www.epson-electronics.de/ Singapore Epson Singapore Pte Ltd 1 HarbourFront Place #03-02 HarbourFront Tower One Singapore, 098633 Tel: (65) 6586-5500 Fax: (65) 6271-3182 http://www.epson.com.sg/ 11.2 Ordering Information To order the S5U13A05P00C100 Evaluation Board, contact the Epson sales representative in your area and order part number S5U13A05P00C100. S1D13A05 X40A-G-014-01 S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 Rev 1.01 Epson Research and Development Vancouver Design Center Page 31 Change Record X40A-G-014-01 Revision 1.01 - Issued: November 1, 2006 • all changes from the last revision of the document are highlighted in Red • section 8, changed part used for items 30 and 35 X40A-G-014-01 Revision 1.0 - Issued: October 5, 2006 • released as Rev 1.0 X40A-G-014-00 Revision 0.01 - Issued: October 4, 2006 • created from S5U13A05B00C User Manual, X40A-G-004-xx • added updated parts list • added updated schematics • minor edits S5U13A05P00C100 Evaluation Board User Manual Issue Date: 2006/11/01 S1D13A05 X40A-G-014-01 Rev 1.01