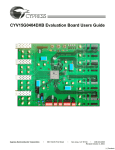

Download Cypress Semiconductor Quad HOTLink II CYV15G0404RB User`s guide

Transcript