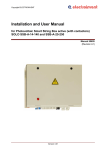

Download Manual Electronic Identification Systems BIS Processor BIS C

Transcript