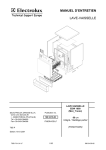

Download Rapports Techniques - Le Service d`Expérimentation et de

Transcript