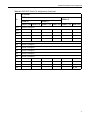

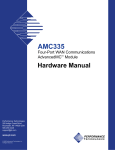

Download PCE335 Cable Pinouts

Transcript