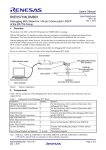

Download S7G2 MCU (High-performance MCU)

Transcript