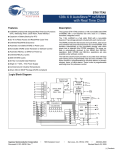

Download CP3210 Single PowerPC 750FX User`s Guide

Transcript