Download Integrated Device Technology

Transcript

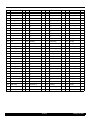

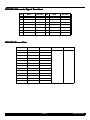

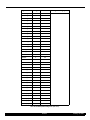

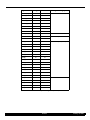

IDT RC32434 DDRCKP DDRCKN Tdo_7m DDRCSN Tdo_7m RowA DDRADDR[13:0] DDRCMD1 NOP Tdo_7m ACTV Col A0 NOP Col A2 RD RD BNKx BNKx RowB NOP NOP PRECHG NOP ACTV NOP DDRCKE Tdo_7m DDRBA[1:0] BNKx BNKx BNKx DDRDM[1:0] DDRDQSx (ideal) D0 DDRDATA[15:0]2 (ideal) D1 D2 D3 Tskew_7g D0 D1 D2 D3 Tskew_7g D0 D1 D2 D3 Tac (min) DDRDQSx (min) DDRDATA[15:0]2 Tac (max) DDRDQSx (max) DDRDATA[15:0]2 1 DDRCMD contains DDRRASN, DDRCASN and DDRWEN. 2 DDRDATA is either 32-bits or 16-bits wide depending on the DBW control bit in DDRC Register (see Chapter 7, DDR Controller, in the RC32434 User Reference Manual). Figure 6 DDR SDRAM AC Timing Waveform - SDRAM Read Access 20 of 53 January 19, 2006