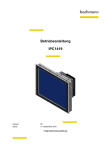

Download USER`S MANUAL

Transcript