Download Capítulo 4 Diagramas esquemáticos, planos de

Transcript

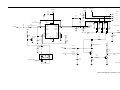

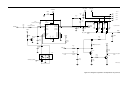

4-1 Capítulo 4 Diagramas esquemáticos, planos de ubicación de componentes y listas de partes 4.1 Introducción Esta sección contiene los diagramas esquemáticos, planos de ubicación de componentes y listas de partes de las tarjetas de circuito y conexiones de interfaz del radio. 4.1.1 Notas para todos los esquemas eléctricos y tarjetas de circuito * Componente sensible a la frecuencia. Remítase a la lista de partes eléctricas para determinar su valor y modo de empleo. 1. A menos que se indique de otra manera, los valores de las resistencias se expresan en ohmios (k = 1000), y los valores de los condensadores, en picofaradios (pF) o microfaradios (µF). 2. Los voltajes CC se miden entre el punto indicado y la tierra de chasis, mediante un multímetro de CC Motorola o un instrumento equivalente. Las mediciones del transmisor deben realizarse usando una bobina de choque de 1,2 µH en serie con la sonda medidora de voltaje para evitar que se cargue el circuito. 3. Los designadores de referencia están asignados de la siguiente forma: Series 400/500 = Controlador Serie 600 = Tarjeta de teclado Serie 3200 = Circuitos de IF Serie 3300 = Receptor Serie 3500 = Transmisor Series 3700 y 3800 = Generación de frecuencias 4. Leyenda de puntos de interconexión: UNSWB+ = Voltaje no conmutado de batería (7,5 V) SWB+ = Voltaje conmutado de batería (7,5 V) R5 = Cinco voltios del receptor CLK = Reloj Vdda = 3,3 voltios regulados (para circuitos analógicos) Vddd = 3,3 voltios regulados (para circuitos digitales) CSX = Línea de selección de circuito integrado (no para LVZIF) SYN = Sintetizador DACRx = Voltaje de convertidor digital-analógico (para el filtro de la etapa de entrada del receptor) VSF = Voltaje superfiltrado (5 voltios) VR = Regulador de voltaje 5. Si se muestran dos niveles de revisión de un esquema eléctrico o lista de partes, ambas versiones tendrán el mismo número de figura o de tabla, pero la versión más antigua estará 4-2 Aspecto del flexible designada con la letra “a” y la versión más reciente estará designada con la letra “b”. 4.1.2 Tarjeta de circuito impreso de seis capas LADO 1 CAPA 1 (L1) CAPA 2 (L2) CAPA 3 (L3) CAPA 4 (L4) CAPA 5 (L5) CAPA 6 (L6) CAPAS INTERNAS LADO 2 Figura 4-1. Tarjeta de circuito impreso de seis capas: escalonamiento del cobre en la secuencia de capas Aspecto del flexible <- TO KP Vista de la parte metálica frontal desde el lado superior 8480475Z02 REV A C 98 TO CTRL -> 40 40 4.2 J601 J400 ZMY0130344-O Figura 4-2. Flexible de interconexión entre el controlador y el teclado Esquema eléctrico del flexible de interconexión entre el controlador y el teclado 4.3 4-3 Esquema eléctrico del flexible de interconexión entre el controlador y el teclado TECLADO J601 CONTROLADOR J400 GND 1 1 GND FLAT_RX_SND GND 2 2 3 FLAT_RX_SND GND 4 5 RX_AUD_RTN GND 6 TX_AUD_SND 7 8 TX_AUD_RTN GND RX_AUD_RTN GND TX_AUD_SND TX_AUD_RTN GND FLAT_TX_RTN 3 4 5 6 7 8 9 OPT_ENA 10 RDY 11 GND 12 URX_SND 13 PTT 14 MISO 15 GND 16 KEYPAD_ROW 17 KEYPAD_COL GND GND SWB+ 18 19 20 21 SWB+ 22 GND 23 KEY_INT 24 GND 25 LEDBL 26 Vddd 27 Vddd 28 GND 29 DATA 30 GND 31 LCD_SEL 32 GND 33 CLK 34 GND 35 RESERVED 36 GND 37 RESERVED 38 RESERVED 39 RESERVED 40 9 FLAT_TX_RTN 10 OPT_ENA 11 RDY 12 GND 13 URX_SND 14 PTT 15 MISO 16 GND 17 18 19 20 21 KEYPAD_ROW KEYPAD_COL GND GND SWB+ 22 23 24 25 26 SWB+ GND KEY_INT GND LEDBL 27 Vddd 28 Vddd 29 GND 30 DATA 31 GND 32 LCD_SEL 33 GND 34 CLK 35 GND 36 RESERVED 37 GND 38 RESERVED 39 RESERVED 40 RESERVED Figura 4-3. Diagrama esquemático del flexible de interconexión entre el controlador y el teclado 4.4 Esquema eléctrico del micrófono/parlante J402 CONECTOR M401 DE 4 PINES 1 1 2 C800 100pF GND 2 INT_MIC 3 INT_SPN 4 M400 SPP SPKR_20 SPKR_20 ZMY0130346-O Figura 4-4. Esquema eléctrico del micrófono/parlante 4-4 Módulo de pantalla - 5104949J08 4.4.1 Conjunto del micrófono/parlante Tabla 4-1 Lista de partes del conjunto del micrófono/parlante Nº de parte Motorola C800 M400 M401 2113740A55 5085738Z02 5013920A04 8485687Z01 09800727Z01 Descripción Condensador 100pF Parlante Micrófono de minielectrete Flexible del micrófono Conector de cable 9 8 7 6 5 4 3 2 1 Módulo de pantalla - 5104949J08 LEDBL GND CLK GND DATA GND LCD_SEL Vddd SWB+ 4.5 Designación de referencia Figura 4-5. Módulo de pantalla ZMY0130358-O Capítulo 4 4-5 Esta página fue dejada intencionalmente en blanco. 4-6 4.6 Diagrama esquemático, tarjeta y lista de partes del teclado J601 44-Pin Connector J601-44 J601-43 J601-42 J601-41 J601-40 J601-39 J601-38 J601-37 J601-36 J601-35 J601-34 J601-33 J601-32 J601-31 J601-30 J601-29 J601-28 J601-27 J601-26 J601-25 J601-24 J601-23 J601-22 J601-21 J601-20 J601-19 J601-18 J601-17 J601-16 J601-15 J601-14 J601-13 J601-12 J601-11 J601-10 J601-9 J601-8 J601-7 J601-6 J601-5 J601-4 J601-3 J601-2 J601-1 FLAT_RX_SND RX_AUD_RTN TX_AUD_SND TX_AUD_RTN FLAT_TX_RTN OPT_ENA RDY URX_SND PTT MISO KEYPAD_ROW KEYPAD_COL J600 11-Pin Connector 1 2 3 4 5 6 7 8 9 SWB+ Vddd LCD_SEL DATA CLK LEDBL J600-1 J600-2 J600-3 J600-4 J600-5 J600-6 J600-7 J600-8 J600-9 SWB+ KEY_INT LEDBL Vddd DATA GND LCD_SEL 10 J600-10 11 J600-11 CLK OUT1 1 4 IN OUT2 2 GND ROW5 M605 SWITCH M604 SWITCH OUT1 1 4 IN OUT2 2 GND 3 EXIT 3 C616 100pF C614 C615 100pF 100pF C613 100pF ROW4 ROW3 UP 1 TP7 OUT1 1 IN 1 TP8 4 OUT2 2 GND 3 M606 SWITCH ENTER ROW4 OUT1 1 IN 4 OUT2 2 GND 3 COL5 C606 0.1uF OUT1 1 4 IN OUT2 2 GND C607 100pF KEYPAD_ROW M608 SWITCH Vddd OUT1 1 IN 4 OUT2 2 GND 1 TP9 M610 SWITCH 1 TP14 OUT1 1 IN 4 OUT2 2 GND 1 M611 SWITCH M612 SWITCH OUT1 1 4 IN OUT2 2 GND 3 2 3 ROW2 3 3 COL2 1 TP15 ROW3 Vddd R618 51K R619 51K R623 43K R622 22K R621 13K KEYPAD_ROW R624 130K R627 13K ROW2 C609 100pF COL2 Vddd C612 10uF COL3 R629 43K ROW5 R630 130K COL4 M613 SWITCH OUT1 1 IN 4 OUT2 2 GND 3 4 M614 SWITCH 2 4 5 1 OUT1 1 4 IN OUT2 2 GND 3 OUT1 1 4 IN OUT2 2 GND 3 7 1 TP16 OUT1 1 4 IN OUT2 2 GND 3 5 M617 SWITCH OUT1 1 IN 4 OUT2 2 GND 8 6 M618 SWITCH ROW4 9 3 M619 SWITCH OUT1 1 4 IN KEY_INT OUT2 2 GND 3 OUT1 1 IN 4 OUT2 2 GND 3 * M620 SWITCH OUT1 1 4 IN 0 OUT2 2 GND 3 C611 100pF R636 1MEG M615 SWITCH COL5 U602 LMC7211 3 R635 560K ROW3 ROW4 R628 22K KEYPAD_COL R634 51K OUT1 1 IN 4 OUT2 2 GND 3 M616 SWITCH C603 100pF Vddd MEM COL5 DOWN 3 OUT1 1 4 IN OUT2 2 GND 3 M622 SWITCH KEYPAD_COL C610 100pF Figura 4-6. Diagrama esquemático de la tarjeta del teclado (tarjeta de circuito impreso nº 8485642Z02) COL2 COL3 M621 SWITCH # ROW5 ZMY0130304-A M623 SWITCH P1 KEYPAD_ROW 4-7 TP7 M605 M604 M623 M622 M606 M608 TP8 J600 1 C610 TP16 C611 C607 R618 TP15 R634 R635 9 M613 C603 R621 R630 R622 R636 C609 U602 M612 M611 R627 R619 M610 R629 R628 TP9 C612 M615 M614 TP14 C606 M616 M617 M618 R623 R624 C613 M619 M620 M621 2 40 J601 39 C616 C615 ZMY0130327-A Vista superior C614 ZMY0130326-A Vista inferior Figura 4-7. Vistas superior e inferior de la tarjeta del teclado (tarjeta de circuito impreso nº 8485642Z02) 4-8 Tabla 4-2a. Lista de partes del teclado (tarjeta de circuito impreso nº 8485642Z01) Designación de referencia C603 C606 C607 C609 C610 C611 C612 C613 C614 C615 C616 J600 J601 R618 R619 R621 R622 R623 R624 R627 R628 R629 R630 R634 R635 R636 U602 Nº de parte Motorola 2113740F51 2113743E20 2113740F51 2113740F51 2113740F51 2113740F51 2113928D08 2113740F51 2113740F51 2113740F51 2113740F51 0985627Z01 0980521Z01 0660076E90 0660076E90 0662057P15 0660079J37 0660079J72 0662057G19 0662057P15 0660079J37 0660079J72 0662057G19 0660076E90 0662057B16 0662057B22 5102463J49 8485642Z01 Descripción 100pF 0,1uF 100pF 100pF 100pF 100pF 10uF 100pF 100pF 100pF 100pF Conector de 11 pines Conector de 44 pines 51K 51K 13K 22K 43K 130K 13K 22K 43K 130K 51K 560K 1M Comparador LMC7211 PCB Tabla 4-2b. Lista de partes del teclado (tarjeta de circuito impreso nº 8485642Z02) Designación de referencia C603 C606 C607 C609 C610 C611 C612 C613 C614 C615 C616 J600 J601 R618 R619 R621 R622 R623 R624 R627 R628 R629 R630 R634 R635 R636 U602 Nº de parte Motorola 2113740F51 2113743E20 2113740F51 2113740F51 2113740F51 2113740F51 2311049A69 2113740F51 2113740F51 2113740F51 2113740F51 0985627Z01 0980521Z01 0660076E90 0660076E90 0662057P15 0660079J37 0660079J72 0662057G19 0662057P15 0660079J37 0660079J72 0662057G19 0660076E90 0662057B16 0662057B22 5102463J49 8485642Z02 Descripción 100pF 0,1uF 100pF 100pF 100pF 100pF 10uF 100pF 100pF 100pF 100pF Conector de 11 pines Conector de 44 pines 51K 51K 13K 22K 43K 130K 13K 22K 43K 130K 51K 560K 1M Comparador LMC7211 PCB 4-9 4.7 Esquema eléctrico del controlador Sección I .............................................. 4-10 403-470 MHz, tarjeta de circuito impreso nº 8480672Z01 136-174 MHz, tarjeta de circuito impreso nº. 8480675Z01 450-527 MHz, tarjeta de circuito impreso nº. 8485755Z01 Sección II ............................................. 4-17 403-470 MHz, tarjeta de circuito impreso nº 8480672Z04 403-470 MHz, tarjeta de circuito impreso nº. 8480672Z06 136-174 MHz, tarjeta de circuito impreso nº. 8480675Z03 403-470 MHz, tarjeta de circuito impreso nº. 8480675Z04 450-527 MHz, tarjeta de circuito impreso nº. 8485755Z03 403-470 MHz, tarjeta de circuito impreso nº. 8485755Z04 4-10 ASFIC DACRX 1 TP402 FLAT_RX_SND 5V GREEN_LED Vdda BATT_CODE UNSWB+ 5V VOX F1200 SYN DATA CLK CSX HSIO RSSI CHACT BATT_DATA_IN FLAT_RX_SND BATT_PULL_UP RSSI BATT_CODE AUDIO_PA_ENA FLAT_SW BATT_PULL_UP GREEN_LED LEDBL MECH_SWB+ MECH_SWB+ URX_SND LEDBL MODIN FLAT_TX_RTN URX_SND RX_AUD_RTN FLAT_TX_RTN MODIN TX_AUD_SND RX_AUD_RTN 16.8MHz TX_AUD_SND RED_LED 16.8MHz TX_AUD_RTN RED_LED MIC_LINE RESET DACRX FLAT_SW AUDIO EXT_SPKR_SEL SWB+ DEMOD LSIO Vdda Vddd UNSWB+ R403 NU CSX MISO AUDIO MIC_LINE CLK C432 NU AUDIO_PA_ENA DATA 5V RESET Vddd SWB+ Vddd Vdda Vdda 4V_3.3V Vddd TX_AUD_RTN IF_4V_3.3V_CTRL Vddd DEMOD MISO 5V Vdda RESET 4V_3.3V SQ_DET IF_5V_CTRL IF_Vdda_CTRL IF_RESET_CTRL 4V_3.3V SWB+ 4V_3.3V RED_LED GREEN_LED SB1 SB2 BATT_CODE INT_SPN SPP SPN MIC SCI INT_MIC RTA0 RTA1 RTA2 RTA3 MECH_SWB+ VOL PTT LVZIF_SEL SWB+ DACRx CSX MODIN DATA CLK LOCK UNSWB+ DEMOD RSSI 16.8MHz UNSWB+ 5V Vdda RESET IF_RED_LED_CTRL IF_GREEN_LED_CTRL IF_SB1_CTRL IF_SB2_CTRL IF_BATT_CODE_CTRL IF_INT_SPN_CTRL IF_SPP_CTRL IF_SPN_CTRL IF_MIC_CTRL IF_SCI_CTRL IF_INT_MIC_CTRL IF_RTA0_CTRL IF_RTA1_CTRL IF_RTA2_CTRL IF_RTA3_CTRL IF_MECHSWB+_CTRL IF_VOL_CTRL IF_PTT_CTRL IF_LVZIF_SEL_CTRL IF_SWB+_CTRL IF_DACRX_CTRL IF_CSX_CTRL IF_MODIN_CTRL IF_DATA_CTRL IF_CLK_CTRL IF_LOCK_CTRL IF_UNSWB+_CTRL IF_DEMOD_CTRL IF_RSSI_CTRL IF_16.8MHz_CTRL EE_CS RED_LED GREEN_LED SB1 SB2 BATT_CODE INT_SPN SPP SPN MIC SCI INT_MIC RTA0 RTA1 RTA2 RTA3 MECH_SWB+ VOL PTT LVZIF_SEL SWB+ DACRx CSX MODIN DATA CLK LOCK UNSWB+ DEMOD RSSI 16.8MHz OFF_BATT_DATA_OUT OFF_BATT_DATA_OUT Esquema eléctrico del controlador, sección I (403-470 MHz para la 8480672Z01, 136-174 MHz para la 8480675Z01, 450-527 MHz para la 8485755Z01) INT_MIC MIC INT_SPN SPN PTT_MIC UNSWB+ SWB+ VOX RESET RDY SPN LCD_SEL CHACT F1200 SYN DATA CLK CSX HSIO LSIO SQ_DET MISO EE_CS BATT_PULL_UP SPP LCD_SEL LVZIF_SEL SPP BATT_PULL_UP BATT_DATA_IN Vddd LVZIF_SEL R_W RAM_CS FLASH_OE FLASH_EN XA18 Audio_PA RDY PTT_MIC PG0 PI1 PG0 PI1 PJ6 PE2 PJ6 PE2 CLK CLK Interface RTA0 Vddd RTA1 RTA1 RTA2 RTA2 RTA3 RTA3 D0 D1 D2 D3 D4 D5 D6 D7 Memory A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 Micro_P SB1 SB1 SB2 SB2 OFF_BATT_DATA_OUT A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 FLAT_SW OPT_ENA MECH_SWB+ VOL FLAT_SW OPT_ENA MECH_SWB+ VOL KEYPAD_COL KEYPAD_ROW KEYPAD_ROW LOCK PTT 1 KEY_INT ZMY0130297-A PG0 PI1 PJ6 PE2 SH400 SHIELD Figura 4-8. Diagrama esquemático completo del controlador MIC OFF_BATT_DATA_OUT KEYPAD_COL PG0 PI1 PJ6 PE2 INT_MIC RSSI LOCK LCD_SEL RSSI RTA0 PTT MISO DATA RAM_CS KEY_INT MISO DATA Vddd LEDBL R_W LEDBL RAM_CS KEYPAD_ROW KEYPAD_COL PTT KEY_INT SCI R_W D0 D1 D2 D3 D4 D5 D6 D7 FLASH_OE KEYPAD_ROW KEYPAD_COL PTT KEY_INT SCI FLASH_OE XA18 FLAT_RX_SND RX_AUD_RTN TX_AUD_SND TX_AUD_RTN FLAT_TX_RTN OPT_ENA RDY URX_SND FLASH_EN FLAT_RX_SND RX_AUD_RTN TX_AUD_SND TX_AUD_RTN FLAT_TX_RTN OPT_ENA RDY URX_SND ON LCD_SEL FLASH_EN SWB+ Vddd INT_SPN XA18 SWB+ Vddd Memory Shield SH401 SHIELD 1 On/Off Shield SH402 SHIELD 1 Microprocessor Shield SH403 SHIELD 1 ASFIC/Audio PA Shield 4-11 4V_3.3V RSSI BATT_CODE R498 MIC_LINE R462 100K 1 5 Q431-1 6 100K R493 NU R499 10K R494 0 R405 0 FLAT_SW C443 0.1uF 3 R401 0 6 1 C407 0.1uF 2 4 Q405 5 1 RESET C410 0.1uF LEDBL R445 24K FLAT_TX_RTN AUDIO MODIN C412 0.1uF R447 1.5MEG C480 10uF 3 R416 39K CR440 2 3 1 MECH_SWB+ 2 OFF_BATT_DATA_OUT R476 24K R448 270K 3 Q403 1 2 R446 220K 7.45V C430 0.1uF FLAT_RX_SND C414 0.1uF C415 .01uF C452 4.7uF C451 .022uF U404 09Z41 TXRTN GCB3 CLK168 VDDD VDDCP GNDD GNDD0 F1200 SYN VDDSYN NC PLCAP2 GCB2 GCB1 GCB0 CHACT SQDET LSIO HSIO CSX CLK DATA GNDSYN LCAP VOX VDDA DISC GNDA DACU DACR DACG VOX PLCAP SQIN UIO VDDDAC AGCCAP 36 35 34 33 32 31 30 29 28 27 26 25 TX_AUD_RTN 3.29V RED_LED C419 16.8MHz NU (UHF); 0.01uF (VHF) F1200 SYN C487 NU C416 0.1uF 13 14 15 16 17 18 19 20 21 22 23 24 1 2 3 4 5 6 7 8 9 10 11 12 DEMOD DACRx Vdda C420 .01uF C421 0.1uF R400 47K C422 0.1uF R413 0 Vddd 5V C428 0.1uF C427 100pF R429 10K EE_CS 6 1 3 7 5 GREEN_LED AUDIO_PA_ENA EXT_SPKR_SEL CHACT SQ_DET LSIO HSIO CSX CLK DATA R449 24K MICEXT GNDRC MICINT VDDRC TXSND AUXRX AUXTX AUDIO MOD URXOUT GCB5 GCB4 48 47 46 45 44 43 42 41 40 39 38 37 Vdda C411 0.1uF BATT_DATA_IN 3.28V TX_AUD_SND C479 0.1uF 3 4 1 URX_SND RX_AUD_RTN CR412 Vdda R475 0 R425 30K C403 10uF 8 INPUT OUTPUT 1 7 FEEDBACK ERROR 5 3 SHUTDOWN SENSE 2 6 VTAP C409 0.1uF R427 10K R406 75K 4 GND Q419-1 BATT_PULL_UP UNSWB+ 1 C402 0.1uF U400 LP2951ACMM-3.3 7.45V C408 100pF 2 C400 .01uF R461 100K TP410 Q400 1 C401 0.1uF 5 R402 NU Vddd 1 3.28V SWB+ TP406 0V 2 4 Q419-2 3 8 VCC U407 X25320_2.7V CLK CS 2 SO MISO WP HOLD SI 4K x 8 BIT 4 VSS EEPROM ZMY0130299-C Figura 4-9. Diagrama esquemático del ASFIC/ON_OFF del controlador 4-12 Vddd F1200 Vddd R457 10K Q418 SCI C493 NU Vddd R437 NU C431 100pF C449 100pF C453 100pF UNSWB+ Vddd Vddd C423 100pF L411 390nH L410 390nH C456 100pF 12 88 39 59 71 72 73 74 75 76 77 78 PE0_AN0 PE1_AN1 PE2_AN2 PE3_AN3 PE4_AN4 PE5_AN5 PE6_AN6 PE7_AN7 67 66 65 64 63 62 61 60 C435 0.1uF KEY_INT VST CSGP3 CSGP4 RTA0 RTA1 RTA2 RTA3 SB1 SB2 PJ6 OFF_BATT_DATA_OUT LOW BATT VOL R415 C433 PE2 91K .01uF RSSI VOX KEYPAD_COL KEYPAD_ROW 3 1 5 R419 4.7K 4 CR414 R414 180K Mech_SWB+ R463 300 TP415 TEST_POINT 1 5 BOOT_CTRL 3 1 47K C433 .01uF R432 51K RT400 33.0K CR413 1 4 Q417 Vddd 2 6 4.7K TP405 TEST_POINT 2 10K UNSWB+ Figura 4-10. Diagrama esquemático del microprocesador del controlador 2 3.30V 47K LOCK PI1 3 SWB+ 4 PTT PTT_MIC OPT_ENA ZMY0130300-B 3.29V C434 0.1uF RESET R_W C494 100pF A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 R460 4.7K 1 95 LVOUT 92 93 VDDSYN XFC 68 69 VRL VRH 90 91 EXTAL XTAL VDD VDDR VDDL AVDD PJ0_CSGP3 PJ1_CSGP4 PJ2 PJ3 PJ4 PJ5 PJ6 PJ7 AVSS PC0_DATA0 PC1_DATA1 PC2_DATA2 PC3_DATA3 PC4_DATA4 PC5_DATA5 PC6_DATA6 PC7_DATA7 22 23 24 25 26 27 28 29 D0 D1 D2 D3 D4 D5 D6 D7 30 31 32 33 34 35 36 37 U409 MC68HC11FL0 89 96 48 94 4 58 57 13 87 VSS 40 VSSR 70 VSSL RAM_CS FLASH_EN ECLK IRQ XIRQ RESET PG7_R_W MODA_LIR MODB_VSTBY PI7 PI6 PI5 PI4 PI3 PI2 PI1 PI0 LCD_SEL PH0_PW1 PH1_PW2 PH2_PW3 PH3_PW4 PH4_CSIO PH5_CSGP1 PH6_CSGP2 PH7_CSPROG 49 50 51 52 53 54 55 56 BATT_PULL_UP 47 46 45 44 43 42 41 38 PB7_ADDR15 PB6_ADDR14 PB5_ADDR13 PB4_ADDR12 PB3_ADDR11 PB2_ADDR10 PB1_ADDR9 PBO_ADDR8 LVZIF_SEL PG0_XA13 PG1_XA14 PG2_XA15 PG3_XA16 PG4_XA17 PG5_XA18 PG6_AS 7 8 15 21 9 11 10 14 XA18 BATT_DATA_IN 6 16 20 19 17 18 5 PF7_ADDR7 PF6_ADDR6 PF5_ADDR5 PF4_ADDR4 PF3_ADDR3 PF2_ADDR2 PF1_ADDR1 PFO_ADDR0 PG0 PA7_PA1_OC1 PA6_OC2_OC1 PA5_OC3_OC1 PA4_OC4_OC1 PA3_IC4_OC5_OC1 PA2_IC1 PA1_IC2 PA0_IC3 PD6_LVIN PD5_SS PD4_SCK PD3_MOSI PD2_MISO PD1_TXD PD0_RXD 3.30V 86 85 84 83 82 81 80 79 R411 10K 3 2 1 100 99 98 97 CLK CSX EE_CS U410 ILC7062CM-33 3.3V 2 VIN VOUT 3 1 VSS DATA 4.7K FLAT_SW R418 0 1.90V SYN 3.28V RDY 18K FLASH_OE LSIO CHACT SQ_DET HSIO TP401 TEST_POINT 1 47K MISO 47K 4-13 R_W R492 0 RAM_CS XA18 R408 NU A0 A1 A2 A3 30 32 7 20 19 18 17 16 15 14 13 3 2 31 1 12 4 5 11 10 6 10 9 8 7 6 5 4 3 25 24 21 23 2 26 1 20 22 27 C425 0.1uF A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 CS OE WE C429 0.1uF EN_CE EN_OE EN_WE A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 28 Vddd 14 8 NC D7 D6 D5 D4 D3 D2 D1 D0 RAM VDD VSS A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 FLASH_OE R410 100K FLASH_EN A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 24 VCC FLASH ROM GND 19 18 17 16 15 13 12 11 C426 100pF U405 SRM2B256 D1 D2 D3 D4 D5 D6 D7 D8 C424 10uF U406 AT49BV020 21 22 23 25 26 27 28 29 9 XA18 D0 D1 D2 D3 D4 D5 D6 D7 R428 2.2 D0 D1 D2 D3 D4 D5 D6 D7 R478 10K Vddd ZMY0130301-O Figura 4-11. Diagrama esquemático de la memoria del controlador 4-14 INT_SPN INT_MIC UNSWB+ C475 10uF J402 1 J402-1 GND 2 J402-2 INT_MIC 3 J402-3 INT_SPN 4 J402-4 SPP C489 1000pF R473 10 U420 TDA8547 AUDIO 15 14 Vddd 6 4 5 R467 10K VCC2 IN1POS OUT1POS IN1NEG OUT1NEG IN2POS OUT2POS IN2NEG OUT2NEG NC1 SELECT NC2 MODE NC3 SVR NC4 1 Q433 GND2 17 NC5 3 C472 100pF Speaker/Mic Connector SPP SPN 18 C486 1000pF 8 C488 1000pF C485 100pF 13 2 C483 100pF C484 100pF L400 390nH MIC_LINE 7 MIC 9 12 C473 SWB+ 19 470pF R435 2K 10 16 VCC1 R472 3.6K C471 100pF C470 100pF 11 20 GND1 R423 47K C447 0.1uF C442 0.1uF C476 10uF R471 5.6K Vddd R436 180K R438 0 C450 0.1uF Vdda R495 100K Q420 6 R434 NU Q410 4 5V PTT_MIC R496 100K AUDIO_PA_ENA 1 2 3 C440 4.7uF Q421 R439 100K ZMY0130302-A Figura 4-12a. Diagrama esquemático del amplificador de potencia de audio del controlador 4-15 INT_SPN INT_MIC UNSWB+ C475 10uF J402 1 J402-1 GND 2 J402-2 INT_MIC 3 J402-3 INT_SPN 4 J402-4 SPP C489 NU R473 10 17 AUDIO 15 14 Vddd 6 4 5 R467 10K VCC2 IN1POS OUT1POS IN1NEG OUT1NEG IN2POS OUT2POS IN2NEG OUT2NEG NC1 SELECT NC2 MODE NC3 SVR NC4 1 Q433 GND2 16 VCC1 R472 36K(UHF),3.6K(VHF) C470 100pF(UHF),NU(VHF) 11 20 GND1 C447 0.1uF U420 TDA8547 NC5 3 C471 100pF C472 100pF Speaker/Mic Connector SPP SPN 18 C486 NU 8 C488 NU C485 100pF 13 2 C483 100pF C484 100pF L400 390nH MIC_LINE 7 MIC 9 12 C473 SWB+ 19 470pF R435 2K 10 R423 470K(UHF),47K(VHF) C442 0.1uF C476 10uF R471 5.6K Vddd R436 47K(UHF),180K(VHF) R438 0 C450 NU Vdda R495 100K Q420 6 R434 NU Q410 4 5V PTT_MIC R496 100K AUDIO_PA_ENA 1 2 3 C440 4.7uF Q421 R439 100K ZMY0130302-B Figura 4-12b. Diagrama esquemático de la interfaz del controlador 4-16 C466 100pF C458 100pF C459 100pF R481 24K J400 40-Pin Connector FLAT_RX_SND RX_AUD_RTN TX_AUD_SND TX_AUD_RTN FLAT_TX_RTN OPT_ENA RDY C467 0.1uF C482 0.1uF C481 0.1uF URX_SND PTT MISO KEYPAD_ROW KEYPAD_COL C463 100pF SWB+ KEY_INT LEDBL Vddd DATA LCD_SEL CLK PG0 PI1 PJ6 PE2 E400 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 ZMY0130303-O Figura 4-13. Diagrama esquemático de la interfaz del controlador J400-1 J400-2 J400-3 J400-4 J400-5 J400-6 J400-7 J400-8 J400-9 J400-10 J400-11 J400-12 J400-13 J400-14 J400-15 J400-16 J400-17 J400-18 J400-19 J400-20 J400-21 J400-22 J400-23 J400-24 J400-25 J400-26 J400-27 J400-28 J400-29 J400-30 J400-31 J400-32 J400-33 J400-34 J400-35 J400-36 J400-37 J400-38 J400-39 J400-40 4-17 ASFIC DACRX 1 TP402 FLAT_RX_SND 5V GREEN_LED Vdda BATT_CODE UNSWB+ 5V VOX F1200 SYN DATA CLK CSX HSIO RSSI CHACT BATT_DATA_IN FLAT_RX_SND BATT_PULL_UP RSSI BATT_CODE AUDIO_PA_ENA FLAT_SW BATT_PULL_UP GREEN_LED LEDBL MECH_SWB+ MECH_SWB+ URX_SND LEDBL MODIN FLAT_TX_RTN URX_SND RX_AUD_RTN FLAT_TX_RTN MODIN TX_AUD_SND RX_AUD_RTN 16.8MHz TX_AUD_SND RED_LED 16.8MHz TX_AUD_RTN RED_LED MIC_LINE RESET DACRX FLAT_SW AUDIO EXT_SPKR_SEL SWB+ DEMOD LSIO Vdda Vddd UNSWB+ R403 NU CSX MISO AUDIO MIC_LINE CLK C432 NU AUDIO_PA_ENA DATA 5V RESET Vddd SWB+ Vddd Vdda Vdda 4V_3.3V Vddd TX_AUD_RTN IF_4V_3.3V_CTRL Vddd DEMOD MISO 5V Vdda RESET 4V_3.3V SQ_DET IF_5V_CTRL IF_Vdda_CTRL IF_RESET_CTRL 4V_3.3V SWB+ 4V_3.3V RED_LED GREEN_LED SB1 SB2 BATT_CODE INT_SPN SPP SPN MIC SCI INT_MIC RTA0 RTA1 RTA2 RTA3 MECH_SWB+ VOL PTT LVZIF_SEL SWB+ DACRx CSX MODIN DATA CLK LOCK UNSWB+ DEMOD RSSI 16.8MHz UNSWB+ 5V Vdda RESET IF_RED_LED_CTRL IF_GREEN_LED_CTRL IF_SB1_CTRL IF_SB2_CTRL IF_BATT_CODE_CTRL IF_INT_SPN_CTRL IF_SPP_CTRL IF_SPN_CTRL IF_MIC_CTRL IF_SCI_CTRL IF_INT_MIC_CTRL IF_RTA0_CTRL IF_RTA1_CTRL IF_RTA2_CTRL IF_RTA3_CTRL IF_MECHSWB+_CTRL IF_VOL_CTRL IF_PTT_CTRL IF_LVZIF_SEL_CTRL IF_SWB+_CTRL IF_DACRX_CTRL IF_CSX_CTRL IF_MODIN_CTRL IF_DATA_CTRL IF_CLK_CTRL IF_LOCK_CTRL IF_UNSWB+_CTRL IF_DEMOD_CTRL IF_RSSI_CTRL IF_16.8MHz_CTRL EE_CS RED_LED GREEN_LED SB1 SB2 BATT_CODE INT_SPN SPP SPN MIC SCI INT_MIC RTA0 RTA1 RTA2 RTA3 MECH_SWB+ VOL PTT LVZIF_SEL SWB+ DACRx CSX MODIN DATA CLK LOCK UNSWB+ DEMOD RSSI 16.8MHz OFF_BATT_DATA_OUT OFF_BATT_DATA_OUT Esquema eléctrico del controlador, Sección II (403-470 MHz para la 8480672Z04/Z06, 136-174 MHz para la 8480675Z03/Z04, 450-527 MHz para la 8485755Z03/Z04) INT_MIC MIC INT_SPN SPN PTT_MIC UNSWB+ SWB+ VOX RESET RDY SPN LCD_SEL CHACT F1200 SYN DATA CLK CSX HSIO LSIO SQ_DET MISO EE_CS BATT_PULL_UP SPP LCD_SEL LVZIF_SEL SPP BATT_PULL_UP BATT_DATA_IN Vddd LVZIF_SEL R_W RAM_CS FLASH_OE FLASH_EN XA18 Audio_PA RDY PTT_MIC PJ6 PE2 CLK Interface CLK RTA2 RTA3 RTA3 D0 D1 D2 D3 D4 D5 D6 D7 Memory A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 Micro_P SB1 SB1 SB2 SB2 OFF_BATT_DATA_OUT A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 FLAT_SW OPT_ENA MECH_SWB+ VOL MIC OFF_BATT_DATA_OUT FLAT_SW OPT_ENA MECH_SWB+ VOL KEYPAD_COL KEYPAD_COL KEYPAD_ROW KEYPAD_ROW PG0 PI1 PJ6 PE2 INT_MIC RTA1 RTA2 LOCK PJ6 PE2 RTA1 ZMY0130297-A PG0 PI1 PJ6 PE2 SH400 SHIELD 1 LOCK PG0 PI1 RTA0 Vddd PTT PG0 PI1 RSSI PTT LCD_SEL RSSI RTA0 KEY_INT MISO DATA RAM_CS KEY_INT MISO DATA Vddd LEDBL R_W LEDBL RAM_CS KEYPAD_ROW KEYPAD_COL PTT KEY_INT SCI R_W D0 D1 D2 D3 D4 D5 D6 D7 FLASH_OE KEYPAD_ROW KEYPAD_COL PTT KEY_INT SCI FLASH_OE XA18 FLAT_RX_SND RX_AUD_RTN TX_AUD_SND TX_AUD_RTN FLAT_TX_RTN OPT_ENA RDY URX_SND FLASH_EN FLAT_RX_SND RX_AUD_RTN TX_AUD_SND TX_AUD_RTN FLAT_TX_RTN OPT_ENA RDY URX_SND ON LCD_SEL FLASH_EN SWB+ Vddd INT_SPN XA18 SWB+ Vddd Memory Shield SH402 SHIELD SH401 SHIELD 1 1 On/Off Shield Microprocessor Shield SH403 SHIELD 1 ASFIC/Audio PA Shield Figura 4-14. Diagrama esquemático completo del controlador 4-18 4V_3.3V RSSI BATT_CODE R498 MIC_LINE R462 100K 1 5 Q431-1 6 100K R493 NU R499 10K R494 0 R405 0 C400 .01uF R401 0 7.45V TP410 Q419-1 C408 100pF 1 INPUT OUTPUT FEEDBACK ERROR SHUTDOWN SENSE VTAP C409 0.1uF 1 R452 100K R446 220K NU R455 NU CR440 2 R454 NU 1 3 DEMOD DACRx VOX C430 0.1uF FLAT_RX_SND C414 0.1uF C415 .01uF C452 4.7uF C451 .022uF VDDA DISC GNDA DACU DACR DACG VOX PLCAP SQIN UIO VDDDAC AGCCAP U404 09Z41 TXRTN GCB3 CLK168 VDDD VDDCP GNDD GNDD0 F1200 SYN VDDSYN NC PLCAP2 GCB2 GCB1 GCB0 CHACT SQDET LSIO HSIO CSX CLK DATA GNDSYN LCAP 1 2 3 4 5 6 7 8 9 10 11 12 36 35 34 33 32 31 30 29 28 27 26 25 TX_AUD_RTN RED_LED 16.8MHz C419 NU 3.29V F1200 SYN C487 NU C416 0.1uF ZMY0130299-D Vddd 13 14 15 16 17 18 19 20 21 22 23 24 R449 24K MICEXT GNDRC MICINT VDDRC TXSND AUXRX AUXTX AUDIO MOD URXOUT GCB5 GCB4 48 47 46 45 44 43 42 41 40 39 38 37 R445 24K C480 10uF R456 0 3 R416 10K Q403 2 3 2 OFF_BATT_DATA_OUT R451 15K 1 MECH_SWB+ LEDBL C412 0.1uF FLAT_TX_RTN AUDIO MODIN TX_AUD_SND C411 0.1uF A1 4 A2 5 A3 CR412 R476 R448 24K 10K R447 100K RX_AUD_RTN 3 K1 2 K2 K3 4 Q405 RESET C410 0.1uF URX_SND C479 0.1uF C403 10uF 1 5 2 6 3.28V R475 0 R425 30K R427 10K R406 75K Vdda C407 0.1uF BATT_PULL_UP UNSWB+ 4 GND 8 7 3 2 1 C402 0.1uF U400 LP2951ACMM-3.3 R461 100K 6 Vdda 3 C401 0.1uF C443 0.1uF Q400 1 FLAT_SW 5 R402 NU Vddd 1 3.28V SWB+ TP406 0V 2 4 Q419-2 3 Vdda C420 .01uF C421 0.1uF R400 47K C422 0.1uF C428 0.1uF C427 100pF R413 0 R429 10K EE_CS GREEN_LED AUDIO_PA_ENA EXT_SPKR_SEL CHACT SQ_DET LSIO HSIO CSX CLK DATA 5V Figura 4-15. Diagrama esquemático del ASFIC/ON_OFF del controlador 6 1 3 7 5 8 VCC U407 X25320_2.7V CLK CS 2 SO MISO WP HOLD SI 4K x 8 BIT 4 VSS EEPROM BATT_DATA_IN 4-19 Vddd F1200 Vddd R457 10K Q418 SCI C493 NU Vddd R437 NU C431 100pF C449 100pF C453 100pF UNSWB+ Vddd Vddd C423 100pF L411 390nH L410 390nH C456 100pF 12 88 39 59 71 72 73 74 75 76 77 78 PE0_AN0 PE1_AN1 PE2_AN2 PE3_AN3 PE4_AN4 PE5_AN5 PE6_AN6 PE7_AN7 67 66 65 64 63 62 61 60 C435 0.1uF C434 0.1uF KEY_INT RESET R_W VST CSGP3 CSGP4 RTA0 RTA1 RTA2 RTA3 SB1 SB2 PJ6 OFF_BATT_DATA_OUT LOW BATT VOL R415 C433 PE2 91K .01uF RSSI VOX KEYPAD_COL KEYPAD_ROW 3 1 5 R419 4.7K 4 CR414 R414 180K Mech_SWB+ R463 300 TP415 TEST_POINT 1 5 BOOT_CTRL 3 1 47K C433 .01uF 2 6 4.7K TP405 TEST_POINT 2 10K UNSWB+ RT400 33.0K CR413 1 4 Q417 Vddd R432 51K LOCK PI1 2 3.30V 47K C494 100pF A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 R460 4.7K 1 95 LVOUT 92 93 VDDSYN XFC 68 69 VRL VRH 90 91 EXTAL XTAL VDD VDDR VDDL AVDD PJ0_CSGP3 PJ1_CSGP4 PJ2 PJ3 PJ4 PJ5 PJ6 PJ7 AVSS PC0_DATA0 PC1_DATA1 PC2_DATA2 PC3_DATA3 PC4_DATA4 PC5_DATA5 PC6_DATA6 PC7_DATA7 22 23 24 25 26 27 28 29 D0 D1 D2 D3 D4 D5 D6 D7 30 31 32 33 34 35 36 37 U409 MC68HC11FL0 89 96 48 94 4 58 57 13 87 VSS 40 VSSR 70 VSSL RAM_CS FLASH_EN ECLK IRQ XIRQ RESET PG7_R_W MODA_LIR MODB_VSTBY PI7 PI6 PI5 PI4 PI3 PI2 PI1 PI0 LCD_SEL PH0_PW1 PH1_PW2 PH2_PW3 PH3_PW4 PH4_CSIO PH5_CSGP1 PH6_CSGP2 PH7_CSPROG 49 50 51 52 53 54 55 56 BATT_PULL_UP 47 46 45 44 43 42 41 38 PB7_ADDR15 PB6_ADDR14 PB5_ADDR13 PB4_ADDR12 PB3_ADDR11 PB2_ADDR10 PB1_ADDR9 PBO_ADDR8 LVZIF_SEL PG0_XA13 PG1_XA14 PG2_XA15 PG3_XA16 PG4_XA17 PG5_XA18 PG6_AS 7 8 15 21 9 11 10 14 XA18 BATT_DATA_IN 6 16 20 19 17 18 5 PF7_ADDR7 PF6_ADDR6 PF5_ADDR5 PF4_ADDR4 PF3_ADDR3 PF2_ADDR2 PF1_ADDR1 PFO_ADDR0 PG0 PA7_PA1_OC1 PA6_OC2_OC1 PA5_OC3_OC1 PA4_OC4_OC1 PA3_IC4_OC5_OC1 PA2_IC1 PA1_IC2 PA0_IC3 PD6_LVIN PD5_SS PD4_SCK PD3_MOSI PD2_MISO PD1_TXD PD0_RXD 3.30V 86 85 84 83 82 81 80 79 R411 10K 3 2 1 100 99 98 97 CLK CSX EE_CS U410 ILC7062CM-33 3.3V 2 VIN VOUT 3 1 VSS DATA 4.7K FLAT_SW R418 0 1.90V SYN 3.28V RDY 18K FLASH_OE LSIO CHACT SQ_DET HSIO TP401 TEST_POINT 1 47K MISO 47K 3 SWB+ 4 PTT PTT_MIC OPT_ENA ZMY0130300-B 3.29V Figura 4-16. Diagrama esquemático del microprocesador del controlador 4-20 R_W R492 0 RAM_CS XA18 R408 NU A0 A1 A2 A3 30 32 7 20 19 18 17 16 15 14 13 3 2 31 1 12 4 5 11 10 6 10 9 8 7 6 5 4 3 25 24 21 23 2 26 1 20 22 27 C425 0.1uF A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 CS OE WE C429 0.1uF EN_CE EN_OE EN_WE A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 28 Vddd 14 8 NC D7 D6 D5 D4 D3 D2 D1 D0 RAM VDD VSS A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 FLASH_OE R410 100K FLASH_EN A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 24 19 18 17 16 15 13 12 11 C426 100pF U405 SRM2B256 D1 D2 D3 D4 D5 D6 D7 D8 C424 10uF U406 AT49BV020 21 22 23 25 26 27 28 29 9 XA18 D0 D1 D2 D3 D4 D5 D6 D7 R428 2.2 D0 D1 D2 D3 D4 D5 D6 D7 ZMY0130301-O Vddd R478 10K Figura 4-17. Diagrama esquemático de la memoria del controlador VCC FLASH ROM GND 4-21 INT_SPN INT_MIC UNSWB+ C475 10uF J402 1 J402-1 GND 2 J402-2 INT_MIC 3 J402-3 INT_SPN 4 J402-4 SPP C489 NU R473 10 17 AUDIO 15 14 Vddd 6 4 5 R467 10K VCC2 IN1POS OUT1POS IN1NEG OUT1NEG IN2POS OUT2POS IN2NEG OUT2NEG NC1 SELECT NC2 MODE NC3 SVR NC4 1 Q433 GND2 16 VCC1 R472 36K(UHF),3.6K(VHF) C470 100pF(UHF),NU(VHF) 11 20 GND1 C447 0.1uF U420 TDA8547 NC5 3 C471 100pF C472 100pF Speaker/Mic Connector SPP SPN 18 C486 NU 8 C488 NU C485 100pF 13 2 C483 100pF C484 100pF L400 390nH MIC_LINE 7 MIC 9 12 C473 SWB+ 19 470pF R435 2K 10 R423 470K(UHF),47K(VHF) C442 0.1uF C476 10uF R471 5.6K Vddd R436 47K(UHF),180K(VHF) R438 0 C450 NU Vdda R495 100K Q420 6 R434 NU Q410 4 5V PTT_MIC R496 100K AUDIO_PA_ENA 1 2 3 C440 4.7uF Q421 R439 100K ZMY0130302-B Figura 4-18. Diagrama esquemático del amplificador de potencia de audio del controlador 4-22 C466 100pF C458 100pF C459 100pF R481 24K J400 40-Pin Connector FLAT_RX_SND RX_AUD_RTN TX_AUD_SND TX_AUD_RTN FLAT_TX_RTN OPT_ENA RDY C467 0.1uF C482 0.1uF C481 0.1uF URX_SND PTT MISO KEYPAD_ROW KEYPAD_COL C463 100pF SWB+ KEY_INT LEDBL Vddd DATA LCD_SEL CLK PG0 PI1 PJ6 PE2 E400 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 ZMY0130303-O Figura 4-19. Diagrama esquemático de la interfaz del controlador J400-1 J400-2 J400-3 J400-4 J400-5 J400-6 J400-7 J400-8 J400-9 J400-10 J400-11 J400-12 J400-13 J400-14 J400-15 J400-16 J400-17 J400-18 J400-19 J400-20 J400-21 J400-22 J400-23 J400-24 J400-25 J400-26 J400-27 J400-28 J400-29 J400-30 J400-31 J400-32 J400-33 J400-34 J400-35 J400-36 J400-37 J400-38 J400-39 J400-40