Download ダウンロード - 余熱@れすぽん

Transcript

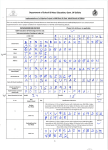

$=35(Y%RDUG ඞହછ http://respon.org/ AZPR EvBoard ྲྀᢅㄝ᫂᭩ ┠ḟ 1. ᴫせ ...................................................................................................................................................3 1.1. ᭦᪂ᒚṔ.....................................................................................................................................3 1.2. ෆᐜ≀ ........................................................................................................................................3 1.3. ὀព㡯.....................................................................................................................................3 1.4. ᭩⡠ࠕCPU ⮬సධ㛛࡚ࠖ〇సࡍࡿᇶᯈࡢ┦㐪Ⅼ ...............................................................3 1.5. ࢧ࣏࣮ࢺ࣮࣌ࢪࡘ࠸࡚............................................................................................................3 2. AZPR EvBoard ࡢᐇ㒊ရ ..............................................................................................................4 3. ᅇ㊰ᅗ ...............................................................................................................................................5 4. ไ⣙ࣇࣝ...................................................................................................................................11 5. 6. 7. FPGA ࡢࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ᪉ἲ ...........................................................................................12 5.1. UrJTAG ࢆ⏝ࡋࡓࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ .........................................................................12 5.2. cblsrv-0.1_ft2232 ࢆ⏝ࡋࡓࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ...........................................................20 5.3. እ㒊ࢲ࣮࢘ࣥࣟࢻࢣ࣮ࣈࣝࡽࡢࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ ....................................................24 ࢲࢢࣉࣟࢢ࣒ࣛ ........................................................................................................................25 6.1. ๓‽ഛ...................................................................................................................................25 6.2. ࢲࢢࣉࣟࢢ࣒ࣛࡢᐇ⾜ ......................................................................................................25 Appendix-A 㟁Ꮚࢧࢥࣟࡢᐇ...................................................................................................27 2 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 1. ᴫせ 1.1. ᭦᪂ᒚṔ 2012/08/11 ึ∧సᡂ 2012/10/20 2 ∧࣭ᮏᩥ୰ࡢㄗࡾࢆゞṇ 1.2. ෆᐜ≀ ᮏ〇ရࡢࣃࢵࢣ࣮ࢪࡣୗグࡢෆᐜ≀ࡀྵࡲࢀࡲࡍࠋ ࣭ AZPR EvBoard ᮏయ ࣭ ࣡ࣥࢱࢵࢳᇶᯈࢫࢱࣥࢻ MPS-08 ࣭ ྲྀᢅㄝ᫂᭩(ᮏ᭩) ࡞࠾ࠊୗグࡢ〇ရࡣᮏ〇ရࡢࣃࢵࢣ࣮ࢪࡣྵࡲࢀ࡚࠾ࡽࡎࠊ࠾ᐈᵝ⮬㌟࡛⏝ពࡋ࡚࠸ࡓࡔࡃᚲせ ࡀ࠶ࡾࡲࡍࠋ ࣭ PC(OS ࡣ windows7 ࢆ᥎ዡ) ࣭ AC ࢲࣉࢱ(ฟຊ㟁ᅽ: 5[V], ฟຊ㟁ὶ:2[A]⛬ᗘ, ෆᚄ 2.1[mm]) ࣭ USB ࢣ࣮ࣈࣝ(A-miniB) ࡲࡓࠊࢲࢢࣉࣟࢢ࣒ࣛࢆືసࡉࡏࡿሙྜࡣୗグࡢ〇ရࡀᚲせ࡞ࡾࡲࡍࠋ ࣭ 10 ࣆࣥࣇࣛࢵࢺࢣ࣮ࣈࣝ(5 ࣆࣥ2 ิ) 1.3. ὀព㡯 ࣭ ᮏ〇ရࢆ࠾࠸࡞ࡿࡣ㟁Ꮚᕤసࡸ㟁Ꮚᅇ㊰ࡘ࠸࡚ࡢ୍⯡ⓗ࡞▱㆑ࠊࢨࣜࣥࢡࢫ♫〇 FPGA ࡘ࠸࡚ࡢ▱㆑ࡸ㛤Ⓨ⎔ቃ࡞ࡀᚲせ࡛ࡍࠋ ࣭ ᮏ〇ရࢆ࠾࠸࡞ࡿ๓ࡣࠊᚲࡎ IC ࡢࢻ࣓࢟ࣗࣥࢺ㢮ࢆཧ↷ࡋ࡚ࡃࡔࡉ࠸ࠋࢨࣜࣥࢡࢫ♫ࡢ ࣮࣒࣮࣍࣌ࢪࡽࠊFPGA ࡢࢻ࣓࢟ࣗࣥࢺࡸ㛤Ⓨࢶ࣮ࣝ࡞ࢆࢲ࣮࢘ࣥࣟࢻ࡛ࡁࡲࡍࠋ ࣭ ᮏ〇ရࡣᏛ⩦⏝ࡢᇶᯈ࡛ࡍࠋᕤᴗ〇ရࡢ⤌ࡳ㎸ࡳ࡞ࠊ⏝㏵እࡢ⏝ࡣࡈ㐲៖ࡃࡔࡉ࠸ࠋࡲࡓࠊ ᮏ〇ရࡼࡗ࡚⏕ࡌࡓᦆᐖ࡞ࡘ࠸࡚ࡣ㈐௵ࢆ㈇࠸ࡡࡲࡍࠋ ࣭ ᮏ〇ရࡢᵝࡣண࿌࡞ࡃኚ᭦࡞ࡿሙྜࡀ࠶ࡾࡲࡍࠋࡈὀពࡃࡔࡉ࠸ࠋ ࣭ ᮏ࣐ࢽࣗࣝࡣࠊෆᐜࡘ࠸࡚⤯ᑐࡢಖドࢆࡍࡿࡶࡢ࡛ࡣ࠶ࡾࡲࡏࢇࠋ 1.4. ᭩⡠ࠕCPU ⮬సධ㛛࡚ࠖ〇సࡍࡿᇶᯈࡢ┦㐪Ⅼ ࣭ ᇶᯈࡢࣂ࣮ࢪࣙࣥࢆ v.1.0 ࡽ v.2.0 ኚ᭦ࡋ࡚࠸ࡲࡍࠋ ࣭ FPGA ࡢᆺ␒ࢆ XC3S250E ࡽ XC3S500E ኚ᭦ࡋ࡚࠸ࡲࡍࠋ ࣭ ࢥࣥࣇࢢ ROM ࡢᆺ␒ࢆ XCF02S ࡽ XCF04S ኚ᭦ࡋ࡚࠸ࡲࡍࠋ ࣭ 㟁※ᅇ㊰ࢆෆⶶࡋ࡚࠸ࡲࡍࠋ ࣭ USB-ࢩࣜࣝኚ IC ⏝ࡢ EEPROM ࢆᐇࡋࠊෆ㒊タᐃࢆ᭩ࡁ㎸ࢇ࡛࠸ࡲࡍࠋ ࡇࡢࡓࡵࠊࢹࣂࢫ࣐ࢿ࣮ࢪࣕࡽࢩ࣏࣮ࣜࣝࢺࡣ 1ch ࡢࡳㄆ㆑ࡉࢀࡲࡍࠋ 1.5. ࢧ࣏࣮ࢺ࣮࣌ࢪࡘ࠸࡚ ୗグࡢ࣮࣌ࢪ࡚ࠊᅇ㊰ᅗࠊไ⣙ࣇࣝࠊࢲࢢࣉࣟࢢ࣒ࣛ࡞ࡢ㓄ᕸ࡞ࢆ⾜ࡗ࡚࠸ࡲࡍࠋ KWWSUHVSRQRUJ 3 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 2. AZPR EvBoard ࡢᐇ㒊ရ ᅗ 1: AZPR EvBoard ࡢᴫほ ࣭ FPGA ࢥࣥࣇࢢ ROM FPGA: Spartan3E(Device: XC3S500E, Package: VQG100, SpeedGrade: -4, ) ࢥࣥࣇࢢ ROM: XCF04S AZPR EvBoard ࡛ࡣ USB ࡼࡿࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥእ㒊ࢲ࣮࢘ࣥࣟࢻࢣ࣮ࣈࣝࡼࡿ ࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࢆࢧ࣏࣮ࢺࡋ࡚࠸ࡲࡍࠋ ヲ⣽ࡣࠕ5 FPGA ࡢࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ᪉ἲࠖࢆཧ↷ࡋ࡚ࡃࡔࡉ࠸ࠋ ࣭ ࢫࢵࢳ 4 ಶᐇࡉࢀ࡚࠸ࡲࡍࠋṇㄽ⌮ධຊࠊࢳࣕࢱࣜࣥࢢ㝖ཤ῭ࡳ࡛ࡍࠋ ࣭ LED 2 ಶᐇࡉࢀ࡚࠸ࡲࡍࠋ㈇ㄽ⌮ฟຊ࡛ࡍࠋ 4 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ࣭ 7 ࢭࢢ࣓ࣥࢺ LED 2 ಶᐇࡉࢀ࡚࠸ࡲࡍࠋࢹࢥ࣮ࢲᅇ㊰ࡣ࡞ࡃࠊFPGA ࡽ┤⤖ࡉࢀ࡚࠸ࡲࡍࠋ㈇ㄽ⌮ฟຊ࡛ࡍࠋ D.P, g, f, e, d, c, b, a ୪ࡓሙྜࡢࢹࢥ࣮ࢻ⾲ࢆ⾲ 1 ࠊ➃Ꮚ㓄⨨ෆ㒊ᅇ㊰ᵓᡂᅗࢆᅗ 2 ♧ࡋࡲࡍࠋ ⾲ 1: 7 ࢭࢢ࣓ࣥࢺ LED ࡢࢹࢥ࣮ࢻ⾲ ⾲♧㻌 㻞 㐍ᩘ㻌 㻝㻢 㐍ᩘ㻌 㻜㻌 㻝㻝㻜㻜㻜㻜㻜㻜㻌 㻜㼤㻯㻜㻌 㻝㻌 㻝㻝㻝㻝㻝㻜㻜㻝㻌 㻜㼤㻲㻥㻌 㻞㻌 㻝㻜㻝㻜㻜㻝㻜㻜㻌 㻜㼤㻭㻠㻌 㻟㻌 㻝㻜㻝㻝㻜㻜㻜㻜㻌 㻜㼤㻮㻜㻌 㻠㻌 㻝㻜㻜㻝㻝㻜㻜㻝㻌 㻜㼤㻥㻥㻌 㻡㻌 㻝㻜㻜㻝㻜㻜㻝㻜㻌 㻜㼤㻥㻞㻌 㻢㻌 㻝㻜㻜㻜㻜㻜㻝㻜㻌 㻜㼤㻤㻞㻌 㻣㻌 㻝㻝㻝㻝㻝㻜㻜㻜㻌 㻜㼤㻲㻤㻌 㻤㻌 㻝㻜㻜㻜㻜㻜㻜㻜㻌 㻜㼤㻤㻜㻌 㻥㻌 㻝㻜㻜㻝㻜㻜㻜㻜㻌 㻜㼤㻥㻜㻌 ᅗ 2: 7 ࢭࢢ࣓ࣥࢺ LED ࡢ➃Ꮚ㓄⨨ෆ㒊ᅇ㊰ᵓᡂᅗ ࣭ ࢡࣟࢵࢡ 10MHz ࡢ࿘Ἴᩘࡀධຊࡉࢀ࡚࠸ࡲࡍࠋFPGA ෆ㒊ࡢ DCM ࡛࿘Ἴᩘࢆኚ᭦ࡍࡿࡇࡀ࡛ࡁࡲࡍࠋ ࣭ ࣜࢭࢵࢺ ㈇ㄽ⌮ධຊ࡛ࡍࠋࣜࢭࢵࢺ➃Ꮚࡣࠊ㟁ᅽ㝆ୗᛂࡌ࡚⮬ືⓗࣜࢭࢵࢺࡀࡾࡲࡍࠋ ࣭ UART USB-ࢩࣜࣝኚ IC ࡼࡿ௬ COM ࣏࣮ࢺ࡛ࡍࠋ ࣭ እ㒊 I/O VPort ࡢ࣎ࢵࢡࢫ࣊ࢵࢲࡀ 2 ಶᐇࡉࢀ࡚࠸ࡲࡍࠋࣆࣥࢆ⾲ 2 ࠊࣆࣥࢧࣥࢆ⾲ 3 ♧ࡋࡲࡍࠋ ⾲ 2: VPort ࡢࣆࣥ 䝢䞁␒ྕ㻌 㻝䡚㻤㻌 ⏝㏵㻌 ỗ⏝ 㻵㻛㻻㻌 㻥㻌 㻳㻺㻰㻌 㻝㻜㻌 㼂㼏㼏㻌 ᅗ 3: VPort ࣎ࢵࢡࢫ࣊ࢵࢲࡢࣆࣥࢧࣥ 3. ᅇ㊰ᅗ ḟ࣮࣌ࢪ௨㝆♧ࡋࡲࡍࠋ 5 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 6 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 7 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 8 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 9 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 10 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 4. ไ⣙ࣇࣝ ไ⣙ࣇࣝࡢసᡂᚲせ࡞ FPGA ࡢ᥋⥆ሗࢆ⾲ 3 ♧ࡋࡲࡍࠋไ⣙㛵ࡍࡿヲ⣽ࡣࠊࢨࣜ ࣥࢡࢫ♫ࡢࠕไ⣙࢞ࢻࠖKWWSMDSDQ[LOLQ[FRPVXSSRUWGRFXPHQWDWLRQGWBLVHKWPࢆཧ↷ࡋ࡚ ࡃࡔࡉ࠸ࠋ ⾲ 3: FPGA ࡢ᥋⥆ሗ 㒊ရྡ㻌 㼏㼘㼛㼏㼗㻌 㼞㼑㼟㼑㼠㻌 㼘㼑㼐㼋㻝㻌 㼘㼑㼐㼋㻞㻌 㼜㼡㼟㼔㼋㼟㼣㼋㻝㻌 㼜㼡㼟㼔㼋㼟㼣㼋㻞㻌 㼜㼡㼟㼔㼋㼟㼣㼋㻟㻌 㼜㼡㼟㼔㼋㼟㼣㼋㻠㻌 㼟㼑㼓㼋㻝㼋㼍㻌 㼟㼑㼓㼋㻝㼋㼎㻌 㼟㼑㼓㼋㻝㼋㼏㻌 㼟㼑㼓㼋㻝㼋㼐㻌 㼟㼑㼓㼋㻝㼋㼑㻌 㼟㼑㼓㼋㻝㼋㼒㻌 㼟㼑㼓㼋㻝㼋㼓㻌 㼟㼑㼓㼋㻝㼋㼐㼜㻌 㼟㼑㼓㼋㻞㼋㼍㻌 㼟㼑㼓㼋㻞㼋㼎㻌 㼟㼑㼓㼋㻞㼋㼏㻌 㼟㼑㼓㼋㻞㼋㼐㻌 㼟㼑㼓㼋㻞㼋㼑㻌 㼟㼑㼓㼋㻞㼋㼒㻌 㼟㼑㼓㼋㻞㼋㼓㻌 㼟㼑㼓㼋㻞㼋㼐㼜㻌 㼢㼜㼛㼞㼠㼋㻝㼋㻝㻌 㼢㼜㼛㼞㼠㼋㻝㼋㻞㻌 㼢㼜㼛㼞㼠㼋㻝㼋㻟㻌 㼢㼜㼛㼞㼠㼋㻝㼋㻠㻌 㼢㼜㼛㼞㼠㼋㻝㼋㻡㻌 㼢㼜㼛㼞㼠㼋㻝㼋㻢㻌 㼢㼜㼛㼞㼠㼋㻝㼋㻣㻌 㼢㼜㼛㼞㼠㼋㻝㼋㻤㻌 㼢㼜㼛㼞㼠㼋㻞㼋㻝㻌 㼢㼜㼛㼞㼠㼋㻞㼋㻞㻌 㼢㼜㼛㼞㼠㼋㻞㼋㻟㻌 㼢㼜㼛㼞㼠㼋㻞㼋㻠㻌 㼢㼜㼛㼞㼠㼋㻞㼋㻡㻌 㼢㼜㼛㼞㼠㼋㻞㼋㻢㻌 㼢㼜㼛㼞㼠㼋㻞㼋㻣㻌 㼢㼜㼛㼞㼠㼋㻞㼋㻤㻌 䝢䞁㻌 㻼㻤㻟㻌 㻼㻤㻡㻌 㻼㻡㻠㻌 㻼㻡㻟㻌 㻼㻞㻞㻌 㻼㻞㻟㻌 㻼㻞㻠㻌 㻼㻞㻢㻌 㻼㻥㻝㻌 㻼㻥㻞㻌 㻼㻝㻞㻌 㻼㻝㻡㻌 㻼㻝㻢㻌 㻼㻥㻜㻌 㻼㻤㻢㻌 㻼㻝㻝㻌 㻼㻟㻌 㻼㻞㻌 㻼㻡㻌 㻼㻥㻌 㻼㻝㻜㻌 㻼㻥㻡㻌 㻼㻥㻠㻌 㻼㻠㻌 㻼㻢㻜㻌 㻼㻢㻝㻌 㻼㻢㻞㻌 㻼㻢㻟㻌 㻼㻢㻡㻌 㻼㻢㻢㻌 㻼㻢㻣㻌 㻼㻢㻤㻌 㻼㻟㻟㻌 㻼㻟㻠㻌 㻼㻟㻡㻌 㻼㻟㻢㻌 㻼㻠㻜㻌 㻼㻠㻝㻌 㻼㻡㻣㻌 㻼㻡㻤㻌 㼄㻯㻟㻿㻡㻜㻜㻱㼋㻼㻵㻺㻌 㻵㻻㼋㻸㻜㻞㻼㼋㻜㻛㻳㻯㻸㻷㻠㻌 㻵㻻㼋㻸㻜㻟㻼㼋㻜㻛㻳㻯㻸㻷㻢㻌 㻵㻻㼋㻸㻜㻝㻺㼋㻝㻌 㻵㻻㼋㻸㻜㻝㻼㼋㻝㻌 㻵㻻㼋㻸㻜㻣㻼㼋㻟㻌 㻵㻻㼋㻸㻜㻣㻺㼋㻟㻌 㻵㻻㼋㻸㻜㻝㻼㼋㻞㻛㻯㻿㻻㼋㻮㻌 㻵㻻㼋㻸㻜㻞㻼㼋㻞㻛㻰㻻㼁㼀㻛㻮㼁㻿㼅㻌 㻵㻻㼋㻸㻜㻡㻺㼋㻜㻛㻳㻯㻸㻷㻝㻝㻌 㻵㻻㻌 㻵㻻㼋㻸㻜㻠㻺㼋㻟㻛㻸㻴㻯㻸㻷㻟㻛㻵㻾㻰㼅㻞㻌 㻵㻻㼋㻸㻜㻡㻼㼋㻟㻛㻸㻴㻯㻸㻷㻠㻛㼀㻾㻰㼅㻞㻌 㻵㻻㼋㻸㻜㻡㻺㼋㻟㻛㻸㻴㻯㻸㻷㻡㻌 㻵㻻㼋㻸㻜㻡㻼㼋㻜㻛㻳㻯㻸㻷㻝㻜㻌 㻵㻻㼋㻸㻜㻟㻺㼋㻜㻛㻳㻯㻸㻷㻣㻌 㻵㻻㼋㻸㻜㻠㻼㼋㻟㻛㻸㻴㻯㻸㻷㻞㻌 㻵㻻㼋㻸㻜㻝㻺㼋㻟㻌 㻵㻻㼋㻸㻜㻝㻼㼋㻟㻌 㻵㻻㼋㻸㻜㻞㻺㼋㻟㻛㼂㻾㻱㻲㼋㻟㻌 㻵㻻㼋㻸㻜㻟㻼㼋㻟㻛㻸㻴㻯㻸㻷㻜㻌 㻵㻻㼋㻸㻜㻟㻺㼋㻟㻛㻸㻴㻯㻸㻷㻝㻌 㻵㻻㼋㻸㻜㻢㻺㼋㻜㻛㼂㻾㻱㻲㼋㻜㻌 㻵㻻㼋㻸㻜㻢㻼㼋㻜㻌 㻵㻻㼋㻸㻜㻞㻺㼋㻟㻛㼂㻾㻱㻲㼋㻟㻌 㻵㻻㼋㻸㻜㻟㻼㼋㻝㻛㻾㻴㻯㻸㻷㻜㻌 㻵㻻㼋㻸㻜㻟㻺㼋㻝㻛㻾㻴㻯㻸㻷㻝㻌 㻵㻻㼋㻸㻜㻠㻼㼋㻝㻛㻾㻴㻯㻸㻷㻞㻌 㻵㻻㼋㻸㻜㻠㻺㼋㻝㻛㻾㻴㻯㻸㻷㻟㻛㼀㻾㻰㼅㻝㻌 㻵㻻㼋㻸㻜㻡㻼㼋㻝㻛㻾㻴㻯㻸㻷㻠㻛㻵㻾㻰㼅㻝㻌 㻵㻻㼋㻸㻜㻡㻺㼋㻝㻛㻾㻴㻯㻸㻷㻡㻌 㻵㻻㼋㻸㻜㻢㻼㼋㻝㻛㻾㻴㻯㻸㻷㻢㻌 㻵㻻㼋㻸㻜㻢㻺㼋㻝㻛㻾㻴㻯㻸㻷㻣㻌 㻵㻻㼋㻸㻜㻟㻺㼋㻞㻛㻰㻢㻛㻳㻯㻸㻷㻝㻟㻌 㻵㻻㻛㻰㻡㻌 㻵㻻㼋㻸㻜㻠㻼㼋㻞㻛㻰㻠㻛㻳㻯㻸㻷㻝㻠㻌 㻵㻻㼋㻸㻜㻠㻺㼋㻞㻛㻰㻟㻛㻳㻯㻸㻷㻝㻡㻌 㻵㻻㼋㻸㻜㻢㻼㼋㻞㻛㻰㻞㻛㻳㻯㻸㻷㻞㻌 㻵㻻㼋㻸㻜㻢㻺㼋㻞㻛㻰㻝㻛㻳㻯㻸㻷㻟㻌 㻵㻻㼋㻸㻜㻞㻼㼋㻝㻌 㻵㻻㼋㻸㻜㻞㻺㼋㻝㻌 㼀㼅㻼㻱㻌 㻳㻯㻸㻷㻌 㻳㻯㻸㻷㻌 㻵㻛㻻㻌 㻵㻛㻻㻌 㻵㻛㻻㻌 㻵㻛㻻㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻌 㻳㻯㻸㻷㻌 㻵㻛㻻㻌 㻳㻯㻸㻷㻌 㻳㻯㻸㻷㻌 㻳㻯㻸㻷㻌 㻳㻯㻸㻷㻌 㻳㻯㻸㻷㻌 㻳㻯㻸㻷㻌 㻵㻛㻻㻌 㻵㻛㻻㻌 㼂㻾㻱㻲㻌 㻳㻯㻸㻷㻌 㻳㻯㻸㻷㻌 㼂㻾㻱㻲㻌 㻵㻛㻻㻌 㼂㻾㻱㻲㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻛㻳㻯㻸㻷㻌 㻰㼁㻭㻸㻌 㻰㼁㻭㻸㻛㻳㻯㻸㻷㻌 㻰㼁㻭㻸㻛㻳㻯㻸㻷㻌 㻰㼁㻭㻸㻛㻳㻯㻸㻷㻌 㻰㼁㻭㻸㻛㻳㻯㻸㻷㻌 㻵㻛㻻㻌 㻵㻛㻻㻌 11 XFI ࣇࣝ 1(7FORFN/2& 3 1(7UHVHW/2& 3 1(7OHGB/2& 3 1(7OHGB/2& 3 1(7SXVKBVZB/2& 3 1(7SXVKBVZB/2& 3 1(7SXVKBVZB/2& 3 1(7SXVKBVZB/2& 3 1(7VHJBBD/2& 3 1(7VHJBBE/2& 3 1(7VHJBBF/2& 3 1(7VHJBBG/2& 3 1(7VHJBBH/2& 3 1(7VHJBBI/2& 3 1(7VHJBBJ/2& 3 1(7VHJBBGS/2& 3 1(7VHJBBD/2& 3 1(7VHJBBE/2& 3 1(7VHJBBF/2& 3 1(7VHJBBG/2& 3 1(7VHJBBH/2& 3 1(7VHJBBI/2& 3 1(7VHJBBJ/2& 3 1(7VHJBBGS/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 1(7YSRUWBB/2& 3 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 5. FPGA ࡢࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ᪉ἲ AZPR EvBoard ࡛ࡣࠊ3 ✀㢮ࡢࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ᪉ἲࢆࢧ࣏࣮ࢺࡋ࡚࠸ࡲࡍࠋ࡞࠾ࠊᮏྲྀᢅㄝ ᫂᭩ࡣࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥሗࢆ᱁⣡ࡋࡓࣇࣝ(BIT ࣇࣝࡸ MCS ࣇࣝ)ࡀ‽ഛࡋ࡚࠶ ࡿ࠸࠺๓ᥦ࡛᭩ࢀ࡚࠸ࡲࡍࠋࢨࣜࣥࢡࢫ♫ࡢࢶ࣮ࣝࡢᇶᮏⓗ࡞࠸᪉ࡣࠊࢨࣜࣥࢡࢫ♫ࡢ࣮࣍ ࣒࣮࣌ࢪ࡞ࢆཧ↷ࡋ࡚ࡃࡔࡉ࠸ࠋ 5.1. UrJTAG ࢆ⏝ࡋࡓࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ UrJTAG ࢆ⏝ࡋࡓࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࡢὶࢀࢆᅗ 4 ♧ࡋࡲࡍࠋ ᅗ 4: UrJTAG ࢆ⏝ࡋࡓࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࡢὶࢀ 5.1.1. SVF ࣇࣝࡢ⏕ᡂ SVF ࡣ Serial Vector Format ࡢ␎࡛ࠊJTAG ᧯సࢆグ㏙ࡋࡓࣇ࡛ࣝࡍࠋࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ ࢹ࣮ࢱࢆ SVF ᙧᘧ࡛ࣇࣝฟຊࡋࠊUrJtag ࠸࠺ࢶ࣮࡛ࣝ⏝ࡋࡲࡍࠋUrJtag ࡛ SVF ࣇࣝ ࢆ⏕ࡍࡿࡇ࡛ࠊࢹࣂࢫᑐࡋ࡚ JTAG ᧯సࢆ⾜࠸ࡲࡍࠋࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥሗࢆ᱁⣡ࡋࡓ ࣇࣝ(BIT ࣇࣝࡸ MCS ࣇࣝ)ࡀ‽ഛࡋ࡚࠶ࡿ࠸࠺๓ᥦ࡛ࠊࡇࡇ࡛ࡣ SVF ࣇࣝసᡂࡢ ᡭ㡰ࢆㄝ᫂ࡋࡲࡍࠋ 12 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ࡲࡎࠊiMPACT ࢆ㉳ືࡋࡲࡍࠋᅗ 5 ࠕISE iMPACT Projectࠖ࢘ࣥࢻ࢘ࢆ♧ࡋࡲࡍࠋ ᅗ 5: iMPACT ㉳ືࡢ⏬㠃 ࠕISE iMPACTࠖ࢘ࣥࢻ࢘ࡢᕥୖࡢ㡿ᇦࡽࠕBoundary Scanࠖࢆࢲࣈࣝࢡࣜࢵࢡࡋࡲࡍࠋ ᅗ 6: Boundary Scan ࡀ⾲♧ࡉࢀ࡚࠸ࡿ㡿ᇦ 13 AZPR EvBoard ྲྀᢅㄝ᫂᭩ Boundary Scan ᐇ⾜ᚋࡢ⏬㠃ࢆᅗ 7 ♧ࡋࡲࡍࠋ ᅗ 7: Boundary Scan ᚋࡢ⏬㠃 ࠕRight click to Add Device or Initialize JTAG chainࠖ⾲♧ࡉࢀࡓ㡿ᇦࢆྑࢡࣜࢵࢡࡋࠊᅗ 8 ♧ ࡍࡼ࠺ [Output File Type]Ѝ[SVF File]Ѝ[Create SVF File]ࢆ㑅ᢥࡋࠊSVF ࣇࣝసᡂࢆ㛤ጞࡋࡲ ࡍࠋ ᅗ 8: Create SVF File ࡢ㑅ᢥ ࠕAdd Deviceࠖࢲࣟࢢ࡛᭩ࡁࡇࡴࣇࣝࢆ㑅ᢥࡋࡲࡍࠋࡇࡇ࡛ BIT ࣇࣝࢆ㑅ᢥࡍࡿሙྜ MCS ࣇࣝࢆ㑅ᢥࡍࡿሙྜ࡛ᡭ㡰ࡀูࢀࡲࡍࠋBIT ࣇࣝࢆ㑅ᢥࡍࡿࠊᅗ 9 ࡢࡼ࠺ ࠕxc3s500eࠖࡀ㏣ຍࡉࢀࡲࡍࠋ 14 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ᅗ 9: BIT ࣇࣝ㏣ຍᚋࡢ⏬㠃 ᅗ 10 ࡢࡼ࠺ࠕSelect Device Part Nameࠖࢲࣟࢢࡀ⾲♧ࡉࢀࡲ MCS ࣇࣝࢆ㑅ᢥࡍࡿࠊᅗ ࡍࠋࡇࡇ࡛ࠊPROM ࢹࣂࢫࡋ࡚ࠊࠕxcf04sࠖࢆ㑅ᢥࡋࡲࡍࠋ[OK]࣎ࢱࣥࢆࢡࣜࢵࢡࡍࡿࠊᅗ 11 ࡢࡼ࠺ࠕxcf04sࠖࡀ㏣ຍࡉࢀࡲࡍࠋ ᅗ 10: Select Device Part Name ᅗ 11: MCS ࣇࣝ㏣ຍᚋࡢ⏬㠃 15 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ᭩ࡁ㎸ࡴࣇࣝࢆ㑅ᢥࡋࡓᚋࠊ㏣ຍࡉࢀࡓࢹࣂࢫୖ࡛ྑࢡࣜࢵࢡࡋࠊ ࠕProgramࠖࢆ㑅ᢥࡋࡲࡍࠋ ᅗ 12 ࡛♧ࡍࠕDevice Programming Propertiesࠖࢲࣟࢢࡀ㛤ࡃࡢ࡛ࠊࡑࡢࡲࡲ[OK]࣎ࢱࣥࢆᢲࡋ ࡲࡍࠋ ᅗ 12: Device Programming Properties ᭱ᚋࠊᅗ 13 ࡢࡼ࠺ࠕProgram Succeededࠖ⾲♧ࡉࢀࡓࡢࢆ☜ㄆᚋࠊ࣓ࢽ࣮ࣗࣂ࣮ࡽ[Output] Ѝ[SVF File]Ѝ[Stop Writing to File]ࢆ㑅ᢥࡋࠊSVF ࣇࣝࡢసᡂࢆ⤊ࡋࡲࡍࠋ ᅗ 13: SVF ࣇࣝసᡂ ௨ୖࡢᡭ㡰࡛ SVF ࣇࣝࡀ⏕ᡂࡉࢀࡲࡍࠋ 16 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 5.1.2. UrJTAG ࡢᐇ⾜ ࣭ ‽ഛ UrJTAG FT2232 ࢻࣛࣂ libusb-win32 ࡀᚲせ࡞ࡾࡲࡍࠋࡇࡇ࡛ࡣࠊࡑࢀࡒࢀࡢࣥࢫࢺ࣮ ࣝࡘ࠸࡚ㄝ᫂ࡋࡲࡍࠋ ¾ UrJTAG UrJTAG ࡣ௨ୗࡢ࣮࣌ࢪࡽࣥࢫࢺ࣮ࣛࢆࢲ࣮ࣥࣟࢻࡋ࡚ࡃࡔࡉ࠸ࠋࣥࢫࢺ࣮ࣛࢆᐇ⾜ࡍࡿ 㝿ࡣࠊࣥࢫࢺ࣮ࣛࢆྑࢡࣜࢵࢡࡋࠕ⟶⌮⪅ࡋ࡚ᐇ⾜ࠖࢆ㑅ᢥࡋ࡚ࠊࣥࢫࢺ࣮ࣝࡋ࡚ࡃࡔࡉ࠸ࠋ KWWSXUMWDJRUJ ¾ FT2232 ࢻࣛࣂ Windows 7 ࡛ࡣࠊFT2232 ࢆ᥋⥆ࡍࡿ FT2232 ࢻࣛࣂࡣ⮬ື࡛ࣥࢫࢺ࣮ࣝࡉࢀࡲࡍࠋUSB ࢣ࣮ࣈ࡛ࣝ PC AZPR EvBoard ࢆ᥋⥆ࡋࠊ㟁※ࢆ ON ࡍࡿ FT2232 ࢻࣛࣂࡢࣥࢫࢺ࣮ࣝࡀ ጞࡲࡾࡲࡍࠋ ¾ libusb-win32 libusb-win32 ࡣ௨ୗࡢ࣮࣌ࢪࡽࢲ࣮࢘ࣥࣟࢻࡋ࡚ࡃࡔࡉ࠸ࠋ KWWSVRXUFHIRUJHQHWDSSVWUDFOLEXVEZLQZLNL PC AZPR EvBoard ࢆ᥋⥆ࡋࡓࡲࡲࠊࢲ࣮࢘ࣥࣟࢻࡋࡓࣇࣝࢆゎࡋࠊ ࠕbinࠖࣇ࢛ࣝࢲෆ ࡢࠕinf-wizard.exeࠖࢆᐇ⾜ࡋࡲࡍࠋᅗ 14 ࡛♧ࡍࠕlibusb-win32 Inf-Wizardࠖࢲࣟࢢࡀ⾲♧ࡉࢀ ࡲࡍࠋ ᅗ 14: libusb-win32 Inf-Wizard (1/3) 17 AZPR EvBoard ྲྀᢅㄝ᫂᭩ [Next]࣎ࢱࣥࢆࢡࣜࢵࢡࡍࡿࠊᅗ 15 ࡛♧ࡍ⏬㠃ࡀ⾲♧ࡉࢀࡲࡍࠋ ᅗ 15: libusb-win32 Inf-Wizard (2/3) ࡇࡇ࡛ࠊࢀ୍ࡘࢹࣂࢫࢆ㑅ᢥࡋࠊ[Next]࣎ࢱࣥࢆᢲࡋࡲࡍࠋᅗ 15 ࡛ࡣࠊࠕDescriptionࠖ ࡀࠕDual RS232 (Interface 1)ࠖࡢࢹࣂࢫࢆ㑅ᢥࡋ࡚࠸ࡲࡍࠋࢲࣟࢢࢆ㐍ࡵࡿࠊᅗ 16 ࡛♧ࡍ⏬ 㠃ࡀ⾲♧ࡉࢀࡲࡍࠋ ᅗ 16: libusb-win32 Inf-Wizard (3/3) ࡇࡇ࡛[Install Now]࣎ࢱࣥࢆᢲࡋࠊࢻࣛࣂࢆࣥࢫࢺ࣮ࣝࡋࡲࡍࠋ ࣭ タᐃ UrJTAG ࡢࣥࢫࢺ࣮ࣝࢹࣞࢡࢺࣜ(C:¥Program Files (x86)¥UrJTAG¥data¥xilinx)௨ୗࡢࣇ ࣝࢆୖ᭩ࡁࡋ࡚㓄⨨ࡋࡲࡍࠋࣇࣝࡣࢧ࣏࣮ࢺ࣮࣌ࢪࡽࢲ࣮࢘ࣥࣟࢻࡋ࡚ࡃࡔࡉ࠸ࠋ &?3URJUDP)LOHV[?8U-7$*?GDWD?[LOLQ[ 3$576 [FVH [FIV 18 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ࣭ FPGA ࡢㄆ㆑ JTAG Shell ࢆ㉳ືࡋࠊ௨ୗࡢࢥ࣐ࣥࢻࢆධຊࡋࡲࡍࠋ MWDJ!FDEOHMWDJNH\ MWDJ!GHWHFW JTAG Shell ௨ୗࡢࡼ࠺⾲♧ࡉࢀࢀࡤࠊFPGA ࡀㄆ㆑ࡉࢀ࡚࠸ࡲࡍࠋ MWDJ!GHWHFW ,5OHQJWK &KDLQOHQJWK 'HYLFH,G[& 0DQXIDFWXUHU;LOLQ[ 3DUW[FVH 6WHSSLQJ )LOHQDPHF?SURJUDPILOHV[?XUMWDJ?GDWD[LOLQ[[FVH[FVH 'HYLFH,G[' 0DQXIDFWXUHU;LOLQ[ 3DUW[FIV 6WHSSLQJ )LOHQDPHF?SURJUDPILOHV[?XUMWDJ?GDWD[LOLQ[[FIV[FIV ࣭ ࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ FPGA ࡢㄆ㆑࡛⾲♧ࡉࢀࡓࡼ࠺ࠊxc3s500e ࡀ part 0ࠊxcf04s ࡀ part 1 ࡞ࡾࡲࡍࠋ BIT ࣇࣝࢆ㑅ᢥࡋ࡚ SVF ࣇࣝࢆసᡂࡋࡓࡁࡣࠊ௨ୗࡢࢥ࣐ࣥࢻࢆᐇ⾜ࡋ࡚ࠊxc3s500e ࢆ 㑅ᢥࡋࡲࡍࠋ MWDJ!SDUW MCS ࣇࣝࢆ㑅ᢥࡋ࡚ SVF ࣇࣝࢆసᡂࡋࡓࡁࡣࠊ௨ୗࡢࢥ࣐ࣥࢻࢆᐇ⾜ࡋ࡚ࠊxcf04s ࢆ㑅 ᢥࡋࡲࡍࠋ MWDJ!SDUW ௨ ୗ ࠊ xcf04s ࡢ ࢥ ࣥ ࣇ ࢠ ࣗ ࣞ ࣮ ࢩ ࣙ ࣥ ࢆ ⾜ ࠺ ࡁ ࡢ ࢥ ࣐ ࣥ ࢻ ࡢ ධ ຊ ࢆ ♧ ࡋ ࡲ ࡍ ࠋ ࠕD:¥sample.svfࠖࡣࠕ5.1.1 SVF ࣇࣝࡢ⏕ᡂ࡛ࠖ⏕ᡂࡋࡓ SVF ࣇࣝࡢࣇࣝࣃࢫ࡞ࡾࡲ ࡍࠋ MWDJ!SDUW MWDJ!VYI'?VDPSOHVYISURJUHVV 3DUVLQJ 6FDQQHGGHYLFHRXWSXWPDWFKHGH[SHFWHG7'2YDOXHV MWDJ! 19 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 5.2. cblsrv-0.1_ft2232 ࢆ⏝ࡋࡓࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ cblsrv-0.1_ft2232 ࡣ fenrir Ặࡼࡗ࡚సᡂࡉࢀࡓࢶ࣮࡛ࣝࡍࠋXilinx ♫ࡢࢲ࣮࢘ࣥࣟࢻࢶ࣮࡛ࣝ࠶ࡿ iMPACT ⤌ࡳྜࢃࡏ࡚ࠊAZPR EvBoard ᦚ㍕ࡉࢀ࡚࠸ࡿ FT2232 ࢆ⤒⏤࡛ࢥࣥࣇࢠ࣮ࣗࣞࢩࣙ ࣥࢆ⾜࠺ࡇࡀ࡛ࡁࡲࡍࠋࡇࡢ᪉ἲ࡛ࡣࠊBIT ࣇࣝࡸ MCS ࣇࣝࢆ࠺ࡓࡵࠊSVF ࣇࣝࢆ సࡿᚲせࡣ࠶ࡾࡲࡏࢇࠋ ὀព㸸cblsrv-0.1_ft2232 ࡢ⏝ࡼࡗ࡚࠸࡞ࡿᦆᐖࡀ⏕ࡌ࡚ࡶ fenrir Ặཬࡧࢀࡍࡱࢇࡣ୍ษࡢ㈐௵ ࡣ㈇࠸ࡲࡏࢇࡢ࡛ࡈᢎࡃࡔࡉ࠸ࠋࡲࡓࠊcblsrv-0.1_ft2232 ࡣ ISE11 ࡲ࡛ࡋືస☜ㄆ࡛ࡁ࡚࠸ࡲࡏ ࢇࠋ᭱᪂∧ࡢ ISE ࡛ࡣືసࡋ࡞࠸ྍ⬟ᛶࡀ࠶ࡾࡲࡍࠋWindows 7 ࡣ ISE 12 ࡽࡢᑐᛂࡢࡓࡵࠊࡇࡇ࡛ ࡣ Windows XP(32bit ∧)࡛ࡢᡭ㡰ࢆ♧ࡋࡲࡍࠋ ࣭ ‽ഛ cblsrv-0.1_ft2232 Microsoft Visual C++ 2008 㡺ᕸྍ⬟ࣃࢵࢣ࣮ࢪ(x86) FT2232 ࡢࢻࣛࣂࡀ ᚲせ࡞ࡾࡲࡍࠋ ¾ cblsrv-0.1_ft2232 cblsrv-0.1_ft2232 ࡣ fenrir Ặࡢ࣮࣒࣮࣍࣌ࢪࡽࢲ࣮ࣥࣟࢻ࡛ࡁࡲࡍࠋ KWWSIHQULUQDUXRNDRUJDUFKLYHVKWPO ࣂࢢࡢಟṇࡀ⾜ࢃࢀ࡚࠸ࡿࡢ࡛ࠊ࡞ࡿࡃ᭱᪂ࡢࣂ࣮ࢪࣙࣥࢆࡗ࡚ࡃࡔࡉ࠸ࠋ(ᇳ➹Ⅼ࡛ࡣ cblsrv-0.1_ft2232_r4804.zip ࡀ᭱᪂ࡢࣂ࣮ࢪ࡛ࣙࣥࡍࠋ)ࢲ࣮࢘ࣥࣟࢻࡋࡓࣇࣝࢆゎࡋࡲࡍࠋ௨㝆 ࡣࠊゎඛࡢࣇ࢛ࣝࢲࢆࠕC:¥AZPR¥cblsrv-0.1_ft2232_r4804ࠖࡋ࡚ㄝ᫂ࡋࡲࡍࠋ ¾ Microsoft Visual C++ 2008 㡺ᕸྍ⬟ࣃࢵࢣ࣮ࢪ(x86) ௨ୗࡢ࣮࣌ࢪࡽ Microsoft Visual C++ 2008 㡺ᕸྍ⬟ࣃࢵࢣ࣮ࢪ(x86)ࢆࢲ࣮࢘ࣥࣟࢻࡋ࡚ ࣥࢫࢺ࣮ࣝࡋ࡚ࡃࡔࡉ࠸ࠋ KWWSZZZPLFURVRIWFRPGRZQORDGVGHWDLOVDVS["IDPLO\LG %'$($'%)% &%)GLVSOD\ODQJ MD ¾ FT2232 ࢻࣛࣂ Windows 7 ᥋⥆ࡋࡓሙྜࠊ⮬ືⓗࢻࣛࣂࡀࣥࢫࢺ࣮ࣝࡉࢀࡲࡍࡀࠊWindows XP ࡛ࡣ௨ ୗࡢ࣮࣌ࢪࡽ FT2232 ࢻࣛࣂࢆࢲ࣮࢘ࣥࣟࢻࡋ࡚ࡃࡔࡉ࠸ࠋVirtual COM Port Driver ࠸࠺ྡ๓ ࡛බ㛤ࡉࢀ࡚࠸ࡲࡍࠋ KWWSZZZIWGLFKLSFRP ࢲ࣮࢘ࣥࣟࢻࡋࡓࣇࣝࢆゎࡋࠊUSB ࢣ࣮ࣈ࡛ࣝ PC AZPR EvBoard ࢆ᥋⥆ࡋ࡚ࡃࡔࡉ ࠸ࠋ㟁※ࢆ ON ࡍࡿ᪂ࡋ࠸ࣁ࣮ࢻ࢙࢘ࡢ᳨ฟ࢘ࢨ࣮ࢻࡀ⾲♧ࡉࢀࡿࡢ࡛ࠊඛゎࡋࡓࣇ࢛ ࣝࢲࡽࠕi386ࠖࣇ࢛ࣝࢲࢆᣦᐃࡋ࡚ࠊࢻࣛࣂࢆࣥࢫࢺ࣮ࣝࡋ࡚ࡃࡔࡉ࠸ࠋ 20 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ࣭ ࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ᪉ἲ ࡇࡇ࡛ࡣࠊMCS ࣇࣝࢆࡗ࡚ xcf04s ࢆࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࡍࡿ᪉ἲࢆ⤂ࡋࡲࡍࠋBIT ࣇ ࣝࢆࡗ࡚ xc3s500e ࢆࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࡶྠࡌ᪉ἲ࡛⾜࠼ࡿࡢ࡛ࠊ㐺ᐅㄞࡳ᭰࠼࡚ࡃࡔࡉ ࠸ࠋ ࡲࡎࠊAZPR EvBoard ࣃࢯࢥࣥࢆ USB ࢣ࣮ࣈ࡛ࣝ᥋⥆ࡋࠊ㟁※ࢫࢵࢳࢆ ON ࡋࡲࡍࠋḟࠊ ࢥ ࣐ ࣥ ࢻ ࣉ ࣟ ࣥ ࣉ ࢺ ࢆ ㉳ ື ࡋ ࠊ cblsrv-0.1_ft2232 ࡢ ᐇ ⾜ ࣇ ࣝ ࠕ cblsrv.exe ࠖ ࡀ ࠕC:¥AZPR¥cblsrv-0.1_ft2232_r4804¥build¥win32¥Releaseࠖ⛣ືࡋࠊ௨ୗࡢࡼ࠺ࢥ࣐ࣥࢻࢆධ ຊࡋࡲࡍࠋ(ͤࠕWindows ࢭ࢟ࣗࣜࢸࡢ㔜せ࡞㆙࿌ࠖࡀ⾲♧ࡉࢀࡓሙྜࡣࠊ ࠕࣈࣟࢵࢡࢆゎ㝖ࡍࡿࠖ࣎ ࢱࣥࢆᢲࡋ࡚ࡃࡔࡉ࠸ࠋ) &?$=35?FEOVUYBIWBU?EXLOG?ZLQ?5HOHDVH!FEOVUYH[H̽FDPRQWHF̽S iMPACT ࢆ㉳ືࡋࡲࡍࠋ(ᅗ 17) ᅗ 17: iMPACT ࡢ⏬㠃 ࢘ࣥࢻ࢘ᕥୖࡢ㡿ᇦࡽࠕBoundary Scanࠖࢆࢲࣈࣝࢡࣜࢵࢡࡋࠊྑࡢࣇ࣮࣒ࣞෆࠕRight click to Add Device or Initialize JTAG chainࠖ࠸࠺ᩥᏐࢆ⾲♧ࡉࡏࡲࡍࠋ 21 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ࡑࡢᚋࠊ࣓ࢽ࣮ࣗࡽ[Output]Ѝ[Cable Setup]ࢆ㑅ᢥࡋࠊCable Communication Setup ࢘ࣥࢻ࢘ ࢆ⾲♧ࡉࡏࡲࡍࠋᅗ 18 ࡢࡼ࠺ࠕCommunication Modeࠖࡢ㡯┠ࡢ Parallel Ϫࢆ㑅ᢥࠊࠕCable Locationࠖࡢ㡯┠ࡢࠕRemoteࠖࢆ㑅ᢥࠊ ࠕHost Nameࠖ[localhost:1234]ධຊࡋࠊOK ࣎ࢱࣥࢆᢲࡋ ࡲࡍࠋࡇࡇ࡛ᣦᐃࡍࡿᩘᏐࡣࠊࠕcblsrv.exeࠖࡢ-p ࢜ࣉࢩ࡛ࣙࣥᣦᐃࡋࡓ࣏࣮ࢺ␒ྕ୍⮴ࡉࡏࡲࡍࠋ ᅗ 18: Cable Communication Setup ࢘ࣥࢻ࢘ ࠕRight click to Add Device or Initialize JTAG chainࠖ⾲♧ࡉࢀ࡚࠸ࡿࣇ࣮࣒ࣞෆࢆྑࢡࣜࢵࢡࡋࠊ ࠕInitialize Chainࠖࢆ㑅ᢥࡋࡲࡍࠋᅗ 19 ࡢࡼ࠺ xcf04s xc3s500e ࢆㄆ㆑ࡋࡲࡍࠋ ᅗ 19: xcf04s xc3s500e ࢆㄆ㆑ࡋࡓ⏬㠃 22 AZPR EvBoard ྲྀᢅㄝ᫂᭩ xcf04s ࢆྑࢡࣜࢵࢡࡋࠊ ࠕAssign New Configuration Fileࠖࢆ㑅ᢥࡍࡿࢲࣟࢢࡀ⾲♧ࡉࢀࡲࡍࠋ ࡇࡇ࡛ MCS ࣇࣝࢆ㑅ᢥࡋࡲࡍࠋࡧ xcf04s ࢆྑࢡࣜࢵࢡࡋࠊProgram ࢆ㑅ᢥࡋࠊOK ࣎ࢱࣥࢆᢲ ࡋ࡚ࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࡀᡂຌࡍࡿࠊᅗ 20 ࡢࡼ࠺ࠕProgram Succeededࠖ⾲♧ࡉࢀࡲࡍࠋ ᅗ 20: ࠕProgram Succeededࠖ⾲♧ࡉࢀࡓ⏬㠃 ࡇࢀ࡛ࠊࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࡣ࡛ࡍࠋ iMPACT ᐇ⾜୰ၥ㢟ࡀⓎ⏕ࡋࡓࡁࡣࠊࢥ࣐ࣥࢻࣉࣟࣥࣉࢺ࡛ CTRL+C ࢆᢲࡋ࡚ࠕcblsrv.exeࠖࢆ ⤊ࡋࠊiMAPCT ࢆ㛢ࡌ࡚ࡃࡔࡉ࠸ࠋࡑࡢᚋࠊࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ᪉ἲࡢ᭱ึࡽࡸࡾ┤ࡋ࡚ࡃࡔ ࡉ࠸ࠋ 23 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 5.3. እ㒊ࢲ࣮࢘ࣥࣟࢻࢣ࣮ࣈࣝࡽࡢࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥ AZPR EvBoard ࡣࠊእ㒊ࢲ࣮࢘ࣥࣟࢻࢣ࣮ࣈࣝࡼࡿࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࡀྍ⬟࡛ࡍࠋእ㒊ࢲ࢘ ࣮ࣥࣟࢻࢣ࣮ࣈࣝࢆ⏝ࡍࡿࡇ࡛ࠊIMPACT ࡽ┤᥋ FPGA ࢆࢥࣥࣇࢠ࣮ࣗࣞࢩࣙࣥࡍࡿࡇࡀ ࡛ࡁࡲࡍࠋ እ㒊ࢲ࣮࢘ࣥࣟࢻࢣ࣮ࣈࣝࢆ⏝ࡍࡿ㝿ࡣࠊJP1 ࢪࣕࣥࣃ࣮ࢆ᥋⥆ࡋࠊᇶᯈୖࡢࢩࣝࢡࡋࡓࡀࡗ ࡚ JTAG ࣆࣥࢆ᥋⥆ࡋࡲࡍࠋࡇࡢࡁࠊࢧࣥࣁࣖࢺ♫〇ࡢࠕࢸࢫࢺ࣡ࣖ TTW-200ࠖࢆ⏝ࡍࡿࢫ ࣮࣮ࣝ࣍ࣝࡢࢡࢭࢫࡀྍ⬟࡞ࡾࡲࡍࠋ ᅗ 21: እ㒊ࢲ࣮࢘ࣥࣟࢻࢣ࣮ࣈࣝࡢ᥋⥆ 24 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 6. ࢲࢢࣉࣟࢢ࣒ࣛ AZPR EvBoard ࡢฟⲴࡢࢥࣥࣇࢢ ROM ࡣࠊFPGA-㒊ရ㛫ࡢ᥋⥆ࢳ࢙ࢵࢡࢆ⾜࠺ࡓࡵࡢࢲ ࢢࣉࣟࢢ࣒ࣛࡀ᱁⣡ࡉࢀ࡚࠸ࡲࡍࠋAZPR EvBoard ࡢ㟁※ࢆධࢀࡿࡇ࡛ࠊࢲࢢࣉࣟࢢ࣒ࣛࢆᐇ ⾜ࡋࡲࡍࠋࡲࡓࠊࢲࢢࣉࣟࢢ࣒ࣛࡣࢧ࣏࣮ࢺ࣮࣌ࢪࡽࢲ࣮࢘ࣥࣟࢻࡍࡿࡇࡀྍ⬟࡛ࡍࠋ 6.1. ๓‽ഛ ࢲࢢࣉࣟࢢ࣒ࣛࡢᐇ⾜ࡣࠊୗグࡢࡼ࠺ࢣ࣮ࣈࣝ㢮ࢆ᥋⥆ࡋࡲࡍࠋ ᅗ 22: ࢲࢢࣉࣟࢢ࣒ࣛᐇ⾜⏝ࡢ᥋⥆ PC ୖ࡛➃ᮎ࢚࣑࣮ࣗࣞࢱ࡛࠶ࡿ TeraTerm ࢆ㉳ືࡋࠊAZPR EvBoard ࡢ COM ࣏࣮ࢺ᥋⥆ࡋࡲࡍࠋ PC TeraTerm ࡀࣥࢫࢺ࣮ࣝࡉࢀ࡚࠸࡞࠸ሙྜࡣࠊ௨ୗࡢ࣮࣌ࢪࡽࢲ࣮࢘ࣥࣟࢻࡋ࡚ࠊࣥࢫࢺ ࣮ࣝࡋ࡚ࡃࡔࡉ࠸ࠋ KWWSVRXUFHIRUJHMSSURMHFWVWWVVKUHOHDVHV USB Serial Port ᥋⥆ࡋࠊTeraTerm ࢆୗグࡢࡼ࠺タᐃࡋࡲࡍࠋ ࣭ ཷಙᨵ⾜ࢥ࣮ࢻࡢタᐃ: LF ࣭ ࢩ࣏࣮ࣜࣝࢺࡢ࣮࣮࣎ࣞࢻࡢタᐃ: 38400 6.2. ࢲࢢࣉࣟࢢ࣒ࣛࡢᐇ⾜ ࣭ LED ࢸࢫࢺ ㉳ື┤ᚋࠊLED1 LED2 ࡀ 3 ᅇࡎࡘⅬ⁛ࡋࡲࡍࠋLED ࡢⅬⅉၥ㢟ࡀ࡞࠸ࡇࢆ☜ㄆࡋ࡚ ࡃࡔࡉ࠸ࠋ ࣭ 7 ࢭࢢࢸࢫࢺ 7 ࢭࢢ࣓ࣥࢺ LED ࡀࠕ11ࠖЍࠕ22ࠖЍࠕ33ࠖЍ㺃㺃㺃Ѝࠕ77ࠖЍࠕ00ࠖ⾲♧ࡋࡲࡍࠋࡍ࡚ࡢᩘᏐ ࡀၥ㢟࡞ࡃฟຊࡉࢀ࡚࠸ࡿࡇࢆ☜ㄆࡋ࡚ࡃࡔࡉ࠸ࠋ 25 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ࣭ UART ࢸࢫࢺ TeraTerm ୖ௨ୗࡢᩥᏐิࡀ⾲♧ࡉࢀࡿࡢ࡛ࠊ࣮࣮࢟࣎ࢻࡢ”n”࣮࢟ࢆᢲࡋ࡚ࡃࡔࡉ࠸ࠋ 3UHVVQNH\ 䛂UART test: Pass䛃䛾⾲♧䛜ฟຊ䛥䜜䛯䜙䚸UART 䝔䝇䝖䛿 Pass 䛸䛺䜚䜎䛩䚹㻌 3UHVVQNH\ Q 8$57WHVW3DVV ࣭ VPort ࢸࢫࢺ UART ࢸࢫࢺ⥆ࡅ࡚ࠊVPort ࢸࢫࢺࢆ⾜࠸ࡲࡍࠋ ࠕVPort test: Passࠖࡢ⾲♧ࡀฟຊࡉࢀࡓࡽࠊVPort ࡢࢸࢫࢺࡣ Pass ࡞ࡾࡲࡍࠋ 93RUWFRQQHFW 93RUWWHVW3DVV ࣭ SW ࢸࢫࢺ VPort ࢸࢫࢺ⥆ࡅ࡚ࠊ ࢫࢵࢳࡢࢸࢫࢺࢆ⾜࠸ࡲࡍࠋSW1 ࡽ SW4 ࡲ࡛ࢆ㡰␒ᢲࡋ࡚ࡃࡔࡉ࠸ࠋ TerTerm ୖ௨ୗࡢ⾲♧ࡀฟຊࡉࢀࡲࡍࠋ ࠕSW test: Passࠖࡢ⾲♧ࡀฟຊࡉࢀࡓࡽࠊSW ࢸࢫࢺࡣ Pass ࡞ࡾࡲࡍࠋ 6:WHVW 6:21 6:2)) 6:21 6:2)) 6:21 6:2)) 6:21 6:2)) 6:WHVW3DVV ࣭ ࢸࢫࢺ⤊ ୖグࡢࢸࢫࢺࡀࡍ࡚⤊ࢃࡿࠊ௨ୗࡢ⾲♧ࡀฟຊࡉࢀࡲࡍࠋ $OOWHVW3DVVHG 8$57WHVW3DVV 93RUWWHVW3DVV 6:WHVW3DVV ௨ୖ࡛ࢲࢢࣉࣟࢢ࣒ࣛࡢࡍ࡚ࡢࢸࢫࢺࡣ⤊࡛ࡍࠋ 26 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 7. Appendix-A 㟁Ꮚࢧࢥࣟࡢᐇ ࢧࣥࣉࣝࣉࣜࢣ࣮ࢩࣙࣥࡋ࡚ࠊ㟁Ꮚࢧࢥࣟࡢᐇࢆ⾜࠸ࡲࡍࠋ㟁Ꮚࢧࢥࣟࡣୗグࡢᵝ࡛タ ィࡋࡲࡍࠋ ࣭ ࣜࢭࢵࢺᚋࠊṆ≧ែ㑄⛣ࡍࡿ ࣭ ࢫࢵࢳ 1 ࢆᢲࡍᅇ㌿≧ែ㑄⛣ࡍࡿ ࣭ ࡧࢫࢵࢳ 1 ࢆᢲࡍṆ≧ែ㑄⛣ࡍࡿ ࣭ ෆ㒊࢝࢘ࣥࢱࢆᣢࡕࠊ࢝࢘ࣥࢱࡢ≧ែᛂࡌ࡚ࢧࢥࣟࡢ್ࢆ⾲♧ࡍࡿ ᅗ 23: 㟁Ꮚࢧࢥࣟࡢ≧ែ㑄⛣ᅗ ࣜࢫࢺ 1 㟁Ꮚࢧࢥࣟࡢࢯ࣮ࢫࢥ࣮ࢻࢆ♧ࡋࡲࡍࠋ 27 AZPR EvBoard ྲྀᢅㄝ᫂᭩ ࣜࢫࢺ 1 㟁Ꮚࢧࢥࣟࡢࢯ࣮ࢫࢥ࣮ࢻ 28 AZPR EvBoard ྲྀᢅㄝ᫂᭩ 29 AZPR EvBoard ྲྀᢅㄝ᫂᭩ [I] ࣔࢪ࣮ࣗࣝᐉゝ ࠕdiceࠖ࠸࠺ࣔࢪ࣮ࣗࣝࢆᐉゝࡋ࡚࠸ࡲࡍࠋධຊࡣࢡࣟࢵࢡ(clk)ࣜࢭࢵࢺ(reset_)ࣉࢵࢩࣗࢫ ࢵࢳ(sw_)ࠋฟຊࡣ 7 ࢭࢢ࣓ࣥࢺ LED(led_)࡛ࡍࠋ [II] ෆ㒊ಙྕࡢᐃ⩏ (1)࡛ỗ⏝ࣃ࣓࣮ࣛࢱࡢ LOW HIGH ࢆᐃ⩏ࡋ࡚࠸ࡲࡍࠋ (2)࡛ LED Ⅼⅉ⏝ࡢࣃ࣓࣮ࣛࢱࢆᐃ⩏ࡋ࡚࠸ࡲࡍࠋ (3)࡛ࢧࢥࣟࡢ≧ែ⏝ࣃ࣓࣮ࣛࢱಙྕࢆᐃ ⩏ࡋ࡚࠸ࡲࡍࠋ㟁ᏊࢧࢥࣟࡣࠕṆ≧ែࠖࠕᅇ㌿≧ែࠖࡢ 2 ࡘࡢ≧ែࢆྲྀࡾࡲࡍࠋ (4)࡛⾲♧⏝ࡢศ࿘࢝࢘ࣥࢱࡢࣃ࣓࣮ࣛࢱಙྕࢆᐃ⩏ࡋ࡚࠸ࡲࡍࠋ㟁Ꮚࢧࢥࣟࡀࠕᅇ㌿≧ែࠖࡢ ࡣࠊศ࿘࢝࢘ࣥࢱࡀ‶ࡍࡿᗘ⾲♧ࡉࢀࡿ್ࡀኚࢃࡾࡲࡍࠋᅇࡣ⾲♧ኚ᭦ࡢ࿘ᮇࢆ 50Hz ࡋࡲࡋࡓࠋࡑࡢࡓࡵࠊศ࿘ẚࡣ AZPR EvBoard ࡢ࢜ࢩ࣮ࣞࢱࡢ࿘Ἴᩘ 10MHz ࢆ 50Hz ࡛ࡗࡓ್ ࡞ࡾࡲࡍࠋᐇ㝿ࡣศ࿘࢝࢘ࣥࢱࡣ 0 ࡽ࢝࢘ࣥࢺࡍࡿࡓࡵࠊ࣐ࢼࢫ 1 ࡋࡓ್࡞ࡾࡲࡍࠋ 199,999 ࢆ࢝࢘ࣥࢺࡍࡿࡢᚲせ࡞ࣅࢵࢺᩘࡣ 18 ࣅࢵࢺ(2^18 = 262,144 < 199,999)࡞ࡿࡢ࡛ࠊ ศ࿘࢝࢘ࣥࢱ(div_cnt)ࡣ 18 ࣅࢵࢺ࡞ࡾࡲࡍࠋ (5)࡛ࢧࢥࣟ⏝ࡢ࢝࢘ࣥࢱࢆᐃ⩏ࡋ࡚࠸ࡲࡍࠋࢧࢥࣟࡣ 1㹼6 ࡢ್ࢆ࢝࢘ࣥࢺࡍࡿࡓࡵࠊ3 ࣅࢵ ࢺ(2^3 = 8 < 6)࡞ࡾࡲࡍࠋ (6)࡛ࢫࢵࢳ⏝ࡢࣛࢵࢳ(ࣞࢪࢫࢱ)ࢆᐃ⩏ࡋ࡚࠸ࡲࡍࠋࢫࢵࢳධຊࡢ࢚ࢵࢪ᳨ฟࢆ⾜࠺ࡓࡵࠊࣛ ࢵࢳࢆ 2 ಶ⏝ࡋࡲࡍࠋ [III] LED ࡢⅬⅉไᚚ ࢧࢥࣟ⏝࢝࢘ࣥࢱ(dice_cnt)ᛂࡌ࡚ LED(led_)Ⅼⅉࣃࢱ࣮ࣥࢆฟຊࡋ࡚࠸ࡲࡍࠋ [IV] ࢫࢵࢳ⏝ࣛࢵࢳไᚚ ࣉࢵࢩࣗࢫࢵࢳࡢධຊ(sw_)ࢆࠕsw_l࡛ࠖࣛࢵࢳࡋࠊࡉࡽࡑࢀࢆࠕsw_dl࡛ࠖࢲࣈࣝࣛࢵࢳࡋ࡚ ࠸ࡲࡍࠋ≧ែไᚚࡢ㒊ศ࡛ࠕsw_lࠖࠕsw_dlࠖࢆẚ㍑ࡋࠊ࡛࢚ࢵࢪࡢ᳨ฟࢆ⾜࠸ࡲࡍࠋ [V] ≧ែไᚚ (7)࡛ࣜࢭࢵࢺࢫࢵࢳࡀᢲࡉࢀ࡚ LOW ࡞ࡗࡓࡽᅇ㊰ࢆ㠀ྠᮇࣜࢭࢵࢺࡋࡲࡍࠋ (8)࡛Ṇ≧ែࡢไᚚࢆ⾜ࡗ࡚࠸ࡲࡍࠋṆ≧ែ࡛ࡣ⌧ᅾࡢ್ࢆಖᣢࡋ⥆ࡅࡲࡍࠋࣉࢵࢩࣗࢫࢵࢳ ࡢࢲ࢚࢘ࣥࢵࢪࢆ᳨ฟ(ࠕsw_lࠖࡀ HIGHࠊࠕsw_dlࠖࡀ LOW)ࡋࡓሙྜࠊᅇ㌿≧ែ㑄⛣ࡋࡲࡍࠋ (9)࡛ᅇ㌿≧ែࡢไᚚࢆ⾜ࡗ࡚࠸ࡲࡍࠋ (10)࡛ࣉࢵࢩࣗࢫࢵࢳࡢࢲ࢚࢘ࣥࢵࢪࢆ᳨ฟࡋࡓሙྜࠊṆ≧ែ㑄⛣ࡋࡲࡍࠋ (11)࡛⾲♧⏝ศ࿘࢝࢘ࣥࢱࡢไᚚࢆ⾜ࡗ࡚࠸ࡲࡍࠋ⾲♧⏝ᩥ㞟࢝࢘ࣥࢱ(div_cnt)ࡀ‶ࡋࡓሙྜࠊ (12)࡚ࢧࢥࣟ⏝ࡢ࢝࢘ࣥࢱࢆ᭦᪂ࡋ࡚࠸ࡲࡍࠋ 30