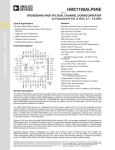

Download HMC832LP6GE

Transcript