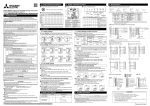

Download version 2.2

Transcript