Download Transcend 64MB SDRAM PC100 Unbuffer Non-ECC Memory

Transcript

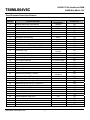

168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C Description Placement The TS8MLS64V8C is a 8M bit x 64 Synchronous Dynamic RAM high density for PC-100. The TS8MLS64V8C consists of 4pcs CMOS 8Mx16 bits Synchronous DRAMs in TSOP-II 400mil packages and a 2048 bits serial EEPROM on a 168-pin printed circuit board. The TS8MLS64V8C is a Dual In-Line Memory Module and is intended for mounting into 168-pin edge connector sockets. Synchronous design allows precise cycle control with the use of system clock. I/O transactions are possible on A every clock cycle. Range of operation frequencies, programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications. B Features D • Performance Range: PC-100. E • Conformed to JEDEC Standard Spec. C • Burst Mode Operation. • Auto and Self Refresh. • CKE Power Down Mode. E • DQM Byte Masking (Read/Write) H • Serial Presence Detect (SPD) with serial EEPROM G F • LVTTL compatible inputs and outputs. • Single 3.3V ± 0.3V power supply. • MRS cycle with address key programs. PCB: 09-7130 Latency (Access from column address) Burst Length (1,2,4,8 & Full Page) Data Sequence (Sequential & Interleave) • All inputs are sampled at the positive going edge of the system clock. Transcend information Inc 1 I 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C Dimensions Pin Identification Side Millimeters A 133.35±0.40 5.250±0.016 B 65.67 2.585 C 23.49 0.925 D 8.89 E Symbol Inches Function A0 ~ A11, BA0, BA1 Address input DQ0 ~ DQ63 Data Input/Output. 0.350 CLK0, CLK2 Clock Input.. 3.00 0.118 CKE0 Clock Enable Input. F 31.75±0.20 1.250±0.008 /CS0, /CS2 Chip Select Input. G 19.80 0.788 H 15.80 0.622 /RAS Row Address Strobe I 1.27±0.10 0.050±0.004 /CAS Column Address Strobe /WE Write Enable DQM0 ~ DQM7 Data (DQ) Mask SA0 ~ SA2 Address in EEPROM SCL Serial PD Clock SDA Serial PD Add/Data input/output Vcc +3.3 Voltage Power Supply Vss Ground NC No Connection (Refer Placement) Transcend information Inc 2 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C Pinouts: Pin Pin Pin Pin No Name No Name 01 Vss 43 Vss 02 DQ0 44 NC 03 DQ1 45 /CS2 04 DQ2 46 DQM2 05 DQ3 47 DQM3 06 Vcc 48 NC 07 DQ4 49 Vcc 08 DQ5 50 NC 09 DQ6 51 NC 10 DQ7 52 *CB2 11 DQ8 53 *CB3 12 Vss 54 Vss 13 DQ9 55 DQ16 14 DQ10 56 DQ17 15 DQ11 57 DQ18 16 DQ12 58 DQ19 17 DQ13 59 Vcc 18 Vcc 60 DQ20 19 DQ14 61 NC 20 DQ15 62 *Vref 21 *CB0 63 *CKE1 22 *CB1 64 Vss 23 Vss 65 DQ21 24 NC 66 DQ22 25 NC 67 DQ23 26 Vcc 68 Vss 27 /WE 69 DQ24 28 DQM0 70 DQ25 29 DQM1 71 DQ26 30 /CS0 72 DQ27 31 NC 73 Vcc 32 Vss 74 DQ28 33 A0 75 DQ29 34 A2 76 DQ30 35 A4 77 DQ31 36 A6 78 Vss 37 A8 79 *CLK2 38 A10/AP 80 NC 39 BA1 81 NC 40 Vcc 82 SDA 41 Vcc 83 SCL 42 CLK0 84 Vcc * Please refer Block Diagram Transcend information Inc Pin No 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 3 Pin Name Vss DQ32 DQ33 DQ34 DQ35 Vcc DQ36 DQ37 DQ38 DQ39 DQ40 Vss DQ41 DQ42 DQ43 DQ44 DQ45 Vcc DQ46 DQ47 *CB4 *CB5 Vss NC NC Vcc /CAS DQM4 DQM5 */CS1 /RAS Vss A1 A3 A5 A7 A9 BA0 A11 Vcc *CLK1 *A12 Pin No 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 Pin Name Vss CKE0 */CS3 DQM6 DQM7 *A13 Vcc NC NC *CB6 *CB7 Vss DQ48 DQ49 DQ50 DQ51 Vcc DQ52 NC *Vref *REGE Vss DQ53 DQ54 DQ55 Vss DQ56 DQ57 DQ58 DQ59 Vcc DQ60 DQ61 DQ62 DQ63 Vss *CLK3 NC SA0 SA1 SA2 Vcc 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C Block Diagram /CS CLK CKE0 CKE /CS CLK CKE DQM4 DQM0 /RAS /CAS /WE 8Mx16 SDRAM /CS DQM5 DQM1 CLK CKE /RAS /CAS /WE 8Mx16 SDRAM /CS DQM6 DQM2 CLK CKE UDQM /CS0 CLK0 /WE 8Mx16 SDRAM A0~A11, BA0,BA1 DQ0~DQ15 LDQM /WE /CAS UDQM /WE /RAS 8Mx16 SDRAM A0~A11, BA0,BA1 DQ0~DQ15 LDQM /CAS UDQM /RAS /CAS LDQM /RAS A0~A11, BA0,BA1 DQ0~DQ15 UDQM DQ0~DQ63 A0~A11, BA0,BA1 DQ0~DQ15 LDQM A0~A11,BA0,BA1 DQM7 DQM3 /CS2 CLK2 Serial EEPROM SCL SCL A0 SDA A1 SDA A2 SA0 SA1 SA2 This technical information is based on industry standard data and tests believed to be reliable. However, Transcend makes no warranties either expressed or implied, as to its accuracy and assumes no liability in connection with the use of this product. Transcend reserves the right to make changes in specifications at any time without prior notice. Transcend information Inc 4 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C ABSOLUTE MAXIMUM RATINGS Parameter Voltage on any pin relative to Vss Voltage on VDD supply to Vss Storage temperature Power dissipation Short circuit current Operating Temperature Symbol VIN, VOUT VDD, VDDQ TSTG PD IOS TA Value -1.0 ~ 4.6 -1.0 ~ 4.6 -55 ~ +150 4 50 0~70 Unit V V °C W mA °C Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to recommended operating condition. Exposure to higher than recommended voltage for extended periods of time could affect device reliability. DC OPERATING CONDITIONS AND CHARACTERISTICS Recommended operating conditions (Voltage referenced to Vss = 0V, TA = 0 to 70°C) Parameter Symbol Min Typ Max Unit Supply voltage VDD 3.0 3.3 3.6 V Input high voltage VIH 2.0 3.0 VDD+0.3 V Input low voltage VIL -0.3 0 0.8 V Output high voltage VOH 2.4 V Output low voltage VOL 0.4 V Input leakage current (Inputs) IIL -10 10 uA Input leakage current (I/O pins) IIL -1.5 1.5 uA Note 1 2 IOH=-2mA IOL=2mA 3 - Note: 1. VIH (max) = 5.6V AC .The overshoot voltage duration is ≤ 3ns. 2. VIL (min) = -2.0V AC .The undershoot voltage duration is ≤ 3ns. 3. Any input 0V ≤ VIN ≤ VDDQ. Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs. 4. Dout is disabled, 0V ≤ VOUT ≤ VDDQ. CAPACITANCE (VDD = 3.3V, TA = 20°C, f = 1MHz, VREF = 1.4V ± 200 mV) Parameter Input capacitance (A0~A11, BA0, BA1) Input capacitance (/RAS, /CAS, /WE) Input capacitance (CKE0) Input capacitance (CLK0, CLK2) Input capacitance (/CS0, /CS2) Input capacitance (DQM0 ~ DQM7) Data input/output capacitance (DQ0 ~ DQ63) Transcend information Inc Symbol Min Max Unit CIN1 CIN2 CIN3 CIN4 CIN5 CIN6 COUT1 15 15 15 10 10 8 9 25 25 25 13 15 10 12 pF pF pF pF pF pF pF 5 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C DC CHARACTERISTICS (Recommended operating condition unless otherwise noted, TA = 0 to 70°C) Parameter Symbol Test Condition CAS Latency Operating Current (One Bank Active) Precharge Standby Current ICC2P in power-down mode ICC2PS ICC2N Precharge Standby Current in non power-down mode Active Standby Current in power-down mode Active Standby Current in non power-down mode (One Bank Active) Burst Length =1 tRC≥tRC(min) IOL=0mA ICC1 ICC2NS Unit Note 400 mA 1 CKE≤VIL (max), tCC=10ns 8 CKE & CLK≤VIL (max), tCC=∞ 8 CKE≥VIH (min), /CS≥VIH (min), tCC=10ns Input signals are changed one time during 20ns CKE≥VIH (min), CLK≤VIL (max), tCC=∞ 80 mA ICC3P CKE≤VIL (max), tCC=10ns 20 ICC3PS CKE & CLK≤VIL (max), tCC=∞ 20 ICC3N CKE≥VIH (min), /CS≥VIH (min), tCC=10ns Input signals are changed one time during 20ns IOL= 0 mA Page Burst tccD = 2CLKs ICC4 Refresh Current ICC5 tRC≥tRC(min) Self Refresh Current ICC6 CKE≤0.2V Note: 1. Measured with outputs open. 2. Refresh period is 64ms. 6 mA 120 mA ICC3NS CKE≥VIH (min), CLK≤VIL(max), tCC=∞ Operating Current (Bust Mode) mA 40 Input signals are stable 100 Input signals are stable Transcend information Inc Value (Typ) 3 520 2 520 mA 1 760 mA 2 8 mA 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C AC OPERATING TEST CONDITIONS (VDD = 3.3V,0.3V, TA = 0 to 70°C) Parameter AC Input levels (VIH/VIL) Input timing measurement reference level Input rise and fall time Output timing measurement reference level Output load condition Value Unit 2.4/0.4 V 1.4 V tr/tf=1/1 ns 1.4 V See Fig. 2 Vtt=1.4V 3.3V 50 Ohm 1200 Ohm Output VOH (DC)=2.4V, IOH=-2mA VOL (DC)=0.4V, I OL=2mA Output Z0=50 Ohm 50pF 50pF 870 Ohm (Fig. 2) AC Output Load Circuit (Fig. 1) DC Output Load Circuit OPERATING AC PARAMETER (AC operating conditions unless otherwise noted) Parameter Symbol Value Unit Note Row active to row active delay tRRD(min) 20 ns 1 /RAS to /CAS delay tRCD(min) 20 ns 1 Row precharge time tRP(min) 20 ns 1 tRAS(min) 50 ns 1 tRAS(max) 100 us Row cycle time tRC(min) 70 ns 1 Last data in to new col. address delay tCDL(min) 1 CLK 2 Last data in to row precharge tRDL(min) 2 CLK 2 Last data in to burst stop tBDL(min) 1 CLK 2 Col. address to col. address delay tCCD(min) 1 CLK 3 ea 4 Row active time Number of valid output data Note: CAS latency=3 2 CAS latency=2 1 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time, and then rounding off to the next higher integer. 2. Minimum delay is required to complete write. 3. All parts allow every cycle column address change. 4. In case of row precharge interrupt, auto precharge and read burst stop. Transcend information Inc 7 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C AC CHARACTERISTICS (AC operating conditions unless otherwise noted) Refer to the individual component, not the whole module. Parameter Symbol CLK cycle time CAS latency=3 CAS latency=2 CLK to valid output delay CAS latency=3 Output data hold time CAS latency=3 Min 10 tCC Max Unit Note 1000 ns 1 ns 1, 2 ns 2 10 6 tSAC CAS latency=2 6 3 tOH CAS latency=2 3 CLK high pulse width tCH 3 ns 3 CLK low pulse width tCL 3 ns 3 Input setup time tSS 2 ns 3 Input hold time tSH 1 1 3 CLK to output in Low-Z tSLZ 1 1 2 CLK to output in Hi-Z CAS latency=3 6 tSHZ ns 6 CAS latency=2 Note: 1. Parameters depend on programmed CAS latency. 2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter. 3. Assumed input rise and fall time (tr & tf)= 1ns. If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter. Transcend information Inc 8 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C SIMPLIFIED TRUTH TABLE COMMAND CKEn-1 CKEn Register Mode Register Set Refresh Auto Refresh Self Refresh Entry Exit Bank Active & Row Addr. Read & Column Address Write & Column Address Burst Stop Precharge (V=Valid, X=Don’t Care, H=Logic High, L=Logic Low) Auto Precharge Disable Auto Precharge Enable /RAS /CAS /WE DQM BA0,1 A10/AP A11, A0~A9 H X L L L L X OP CODE H H L L L L H X X L H L H H X H X H X X X H X L L H H X V H X L H L H X V H X L H L L X V H X L H H L X H X L L H L X H L H X X X L V V V X X X X H X X X L H H H H X X X L V V V H X X X L H H H Auto Precharge Disable Auto Precharge Enable Clock Suspend or Active Power Down Bank Selection Both Banks Entry Exit Precharge Power Down Mode L H H L Entry L DQM No Operation Command V X 1,2 3 3 3 3 Row Address L H L H X L H Column Address (A0~A8) Column Address (A0~A8) 4 4, 5 4 4, 5 6 X X X X X H X H H X X V X X X 1. OP Code : Operand Code A0~A11, BA0~BA1 : Program keys. (@MRS) 2. MRS can be issued only at both banks precharge state. A new command can be issued after 2 CLK cycles of MRS. 3. Auto refresh functions are as same as CBR refresh of DRAM. The automatical precharge without row precharge command is meant by “Auto”. Auto/self refresh can be issued only at both banks precharge state. 4. BA0~BA1: Bank select address. If both BA0 and BA1 are “Low” at read, write, row active and precharge, bank A is selected. If both BA0 is “Low” and BA1 is “High” at read, write, row active and precharge, bank B is selected. If both BA0 is “High” and BA1 is “Low” at read, write, row active and precharge, bank C is selected. If both BA0 and BA1 are “High” at read, write, row active and precharge, bank D is selected. If A10/AP is “High” at row precharge, BA0 and BA1 is ignored and both banks are selected. 5. During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst. New row active of the associated bank can be issued at tRP after the end of burst. 6. Burst stop command is valid at every burst length. 7. DQM sampled at positive going edged of a CLK masks the data-in at the very CLK (Write DQM latency is 0), but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2) Transcend information Inc Note X Exit Note: /CS 9 7 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C Serial Presence Detect Specification Serial Presence Detect Byte No. Function Described 0 1 2 3 4 5 6 7 8 9 10 11 # of Bytes Written into Serial Memory Total # of Bytes of S.P.D Memory Fundamental Memory Type # of Row Addresses on this Assembly # of Column Addresses on this Assembly # of Module Banks on this Assembly Data Width of this Assembly Data Width Continuation Voltage Interface Standard of this Assembly SDRAM Cycle Time (highest CAS latency) SDRAM Access from Clock (highest CL) DIMM configuration type (non-parity, ECC) 12 Refresh Rate Type 13 14 15 16 17 18 19 20 21 Primary SDRAM Width Error Checking SDRAM Width Min Clock Delay Back to Back Random Address Burst Lengths Supported Number of banks on each SDRAM device CAS # Latency CS # Latency Write Latency SDRAM Module Attributes 22 SDRAM Device Attributes : General 23 24 25 26 27 28 29 30 31 32 33 34 35 36-61 SDRAM Cycle Time (2nd highest CL) SDRAM Access from Clock (2nd highest CL) SDRAM Cycle Time (3rd highest CL) SDRAM Access from Clock (3rd highest CL) Minimum Row Precharge Time Minimum Row Active to Row Activate Minimum RAS to CAS Delay Minimum RAS Pulse Width Density of Each Bank on Module Command/Address Setup Time Command/Address Hold Time Data Signal Setup Time Data Signal Hold Time Superset Information Transcend information Inc 10 Standard Specification 128bytes 256bytes SDRAM 12 9 1 bank 64bits LVTTL3.3V 10ns 6ns Non parity 15.625us/Self Refresh X16 None 1 clock 1,2,4,8 & Full page 4 bank 2&3 0 clock 0 clock Non Buffered Prec All, Auto Prec, R/W Burst 12ns 7ns 20ns 20ns 20ns 50ns 1 row of 64MB 2ns 1ns 2ns 1ns - Vendor Part 80 08 04 0C 09 01 40 00 01 A0 60 00 80 10 00 01 8F 04 06 01 01 00 0E C0 70 00 00 14 14 14 32 10 20 10 20 10 00 168PIN PC100 Unbuffered DIMM 64MB With 8Mx16 CL3 TS8MLS64V8C 62 63 64-71 72 SPD Data Revision Code Checksum for Bytes 0-62 Manufacturers JEDEC ID Code per JEP-108E Manufacturing Location JEDEC2 Transcend T 12 3D 7F, 4F 54 54 53 38 4D 4C 53 73-90 91-92 93-94 95-98 99-125 126 127 128~ Manufacturers Part Number Revision Code Manufacturing Date Assembly Serial Number Manufacturer Specific Data Intel Specification Frequency Intel Specification CAS# Latency/Clock Signal Support Unused Storage Locations Transcend information Inc 11 TS8MLS64V8C 36 34 56 38 43 20 By Manufactory By Manufactory 100MHz CL=2, 3 Clock 0~3 Open 20 20 20 20 20 20 0 Variable Variable 0 64 F4 FF