Download S3FN429

Transcript

S3FN429

32-bit CMOS Microcontrollers

Revision 1.20

May 2012

User's Manual

2012

Samsung Electronics Co., Ltd. All rights reserved.

Important Notice

Samsung Electronics Co. Ltd. ("Samsung") reserves the

right to make changes to the information in this publication

at any time without prior notice. All information provided is

for reference purpose only. Samsung assumes no

responsibility for possible errors or omissions, or for any

consequences resulting from the use of the information

contained herein.

This publication on its own does not convey any license,

either express or implied, relating to any Samsung and/or

third-party products, under the intellectual property rights of

Samsung and/or any third parties.

any information provided in this publication. Customer shall

indemnify and hold Samsung and its officers, employees,

subsidiaries, affiliates, and distributors harmless against all

claims, costs, damages, expenses, and reasonable attorney

fees arising out of, either directly or indirectly, any claim

(including but not limited to personal injury or death) that

may be associated with such unintended, unauthorized

and/or illegal use.

Customers are responsible for their own products and

applications. "Typical" parameters can and do vary in

different applications. All operating parameters, including

"Typicals" must be validated for each customer application

by the customer's technical experts.

WARNING No part of this publication may be reproduced,

stored in a retrieval system, or transmitted in any form or by

any means, electric or mechanical, by photocopying,

recording, or otherwise, without the prior written consent of

Samsung. This publication is intended for use by designated

recipients only. This publication contains confidential

information (including trade secrets) of Samsung protected

by Competition Law, Trade Secrets Protection Act and other

related laws, and therefore may not be, in part or in whole,

directly or indirectly publicized, distributed, photocopied or

used (including in a posting on the Internet where

unspecified access is possible) by any unauthorized third

party. Samsung reserves its right to take any and all

measures both in equity and law available to it and claim full

damages against any party that misappropriates Samsung's

trade secrets and/or confidential information.

Samsung products are not designed, intended, or authorized

for use in applications intended to support or sustain life, or

for any other application in which the failure of the Samsung

product could reasonably be expected to create a situation

where personal injury or death may occur. Customers

acknowledge and agree that they are solely responsible to

meet all other legal and regulatory requirements regarding

their applications using Samsung products notwithstanding

警 告 本文件仅向经韩国三星电子株式会社授权的人员提供,

其内容含有商业秘密保护相关法规规定并受其保护的三星电

子株式会社商业秘密,任何直接或间接非法向第三人披露、

传播、复制或允许第三人使用该文件全部或部分内容的行为

(包括在互联网等公开媒介刊登该商业秘密而可能导致不特

定第三人获取相关信息的行为)皆为法律严格禁止。此等违

法行为一经发现,三星电子株式会社有权根据相关法规对其

采取法律措施,包括但不限于提出损害赔偿请求。

Samsung makes no warranty, representation, or guarantee

regarding the suitability of its products for any particular

purpose, nor does Samsung assume any liability arising out

of the application or use of any product or circuit and

specifically disclaims any and all liability, including without

limitation any consequential or incidental damages.

Copyright 2012 Samsung Electronics Co., Ltd.

Samsung Electronics Co., Ltd.

San #24 Nongseo-Dong, Giheung-Gu

Yongin-City, Gyeonggi-Do, Korea 446-711

Contact Us: [email protected]

TEL:

(82)-(31)-209-4956

FAX:

(82)-(31)-8000-2005

Home Page: http://www.samsungsemi.com

Trademarks

All brand names, trademarks and registered trademarks belong to their respective owners.

Exynos, Exynos4210, FlexOneNAND, and OneNAND are trademarks of Samsung Electronics.

ARM, Jazelle, TrustZone, and Thumb are registered trademarks of ARM Limited. Cortex, ETM, ETB,

Coresight, ISA, and Neon are trademarks of ARM Limited.

Java is a trademark of Sun Microsystems, Inc.

SD is a registered trademark of Toshiba Corporation.

MMC and eMMC are trademarks of MultiMediaCard Association.

JTAG is a registered trademark of JTAG Technologies, Inc.

Synopsys is a registered trademark of Synopsys, Inc.

I2S is a trademark of Phillips Electronics.

I2C is a trademark of Phillips Semiconductor Corp.

MIPI and Slimbus are registered trademarks of the Mobile Industry Processor Interface (MIPI) Alliance.

All other trademarks used in this publication are the property of their respective owners.

Chip Handling Guide

Precaution against Electrostatic Discharge

When using semiconductor devices, ensure that the environment is protected against static electricity:

1. Wear antistatic clothes and use earth band.

2. All objects that are in direct contact with devices must be made up of materials that do not produce static

electricity.

3. Ensure that the equipment and work table are earthed.

4. Use ionizer to remove electron charge.

Contamination

Do not use semiconductor products in an environment exposed to dust or dirt adhesion.

Temperature/Humidity

Semiconductor devices are sensitive to:

Environment

Temperature

Humidity

High temperature or humidity deteriorates the characteristics of semiconductor devices. Therefore, do not store or

use semiconductor devices in such conditions.

Mechanical Shock

Do not to apply excessive mechanical shock or force on semiconductor devices.

Chemical

Do not expose semiconductor devices to chemicals because exposure to chemicals leads to reactions that

deteriorate the characteristics of the devices.

Light Protection

In non- Epoxy Molding Compound (EMC) package, do not expose semiconductor IC to bright light. Exposure to

bright light causes malfunctioning of the devices. However, a few special products that utilize light or with security

functions are exempted from this guide.

Radioactive, Cosmic and X-ray

Radioactive substances, cosmic ray, or X-ray may influence semiconductor devices. These substances or rays

may cause a soft error during a device operation. Therefore, ensure to shield the semiconductor devices under

environment that may be exposed to radioactive substances, cosmic ray, or X-ray.

EMS (Electromagnetic Susceptibility)

Strong electromagnetic wave or magnetic field may affect the characteristic of semiconductor devices during the

operation under insufficient PCB circuit design for Electromagnetic Susceptibility (EMS).

Revision History

Revision No.

1.00

Date

Jan. 17, 2012

Description

Promoted from preliminary to V1.0 and released

Author(s)

YH Jin

Added guide notes (caution) related to the pin (XIN and

XOUT) connection for unused external oscillator.

1.10

Feb. 22, 2012

Page 2-7, 5-8, 5-21, 5-41, 5-59, and 19-7

Corrected the errata.

MCU solution

part

The offset address of PPD_SCTVHR register in page

7-37 was fixed from 0x006C to 0x005C.

Added guide notes related to the pin (OPAMP output

1.20

May. 16, 2012

pin) configuration when OPAMP is enabled.

Page 12-5, 13-8

MCU solution

part

Table of Contents

1 PRODUCT OVERVIEW .................................................................................1-1

1.1 Introduction .............................................................................................................................................. 1-1

1.2 Features ................................................................................................................................................... 1-2

1.3 Block Diagram .......................................................................................................................................... 1-9

2 PIN CONFIGURATION ..................................................................................2-1

2.1 Overview .................................................................................................................................................. 2-1

2.2 Pin Map .................................................................................................................................................... 2-2

2.3 Pin Assignment ........................................................................................................................................ 2-3

2.4 Mirror Pins ................................................................................................................................................ 2-5

2.5 Pin Description ......................................................................................................................................... 2-6

2.5.1 Power Pins ........................................................................................................................................ 2-6

2.5.2 System Pins ...................................................................................................................................... 2-7

2.5.3 Function Pins .................................................................................................................................... 2-9

2.5.4 Debug Interface Pins ...................................................................................................................... 2-10

2.5.5 Flash Serial Program Pins .............................................................................................................. 2-10

2.6 Pin Circuit Type ...................................................................................................................................... 2-11

2.6.1 Block Diagram ................................................................................................................................ 2-11

3 SYSTEM MEMORY MANAGEMENT.............................................................3-1

3.1 Overview .................................................................................................................................................. 3-1

3.2 Default Memory Map ................................................................................................................................ 3-1

3.3 Special Function Register Map ................................................................................................................ 3-2

3.3.1 Core Special Function Register Map ................................................................................................ 3-2

3.3.2 Peripheral Special Function Register Map ....................................................................................... 3-3

4 ANALOG TO DIGITAL CONVERTER (ADC) ................................................4-1

4.1 Overview .................................................................................................................................................. 4-1

4.1.1 Features ............................................................................................................................................ 4-1

4.1.2 Pin Description.................................................................................................................................. 4-1

4.1.3 Block Diagram .................................................................................................................................. 4-2

4.1.4 Input and Output ............................................................................................................................... 4-3

4.1.5 Clock Frequency and Conversion Time ........................................................................................... 4-4

4.1.6 Conversion Mode.............................................................................................................................. 4-5

4.1.7 Conversion Start Trigger .................................................................................................................. 4-9

4.1.8 Conversion Data ............................................................................................................................. 4-10

4.1.9 Interrupt and Flag ........................................................................................................................... 4-10

4.1.10 Calibration ..................................................................................................................................... 4-11

4.1.11 Operation Sequence ..................................................................................................................... 4-14

4.2 Register Description ............................................................................................................................... 4-16

4.2.1 Register Map Summary .................................................................................................................. 4-16

5 CLOCK AND POWER MANAGER ................................................................5-1

5.1 Overview .................................................................................................................................................. 5-1

5.1.1 Features ............................................................................................................................................ 5-2

5.1.2 Block Diagram .................................................................................................................................. 5-4

5.2 Clocks ...................................................................................................................................................... 5-5

5.2.1 SYSCLK ............................................................................................................................................ 5-5

5.2.2 IMCLK ............................................................................................................................................... 5-7

5.2.3 EMCLK ............................................................................................................................................. 5-7

5.2.4 PLL ................................................................................................................................................... 5-8

5.2.5 Clock Monitor .................................................................................................................................. 5-11

5.2.6 Clock Out ........................................................................................................................................ 5-13

5.3 Clock Change......................................................................................................................................... 5-14

5.3.1 Clock State Machine ....................................................................................................................... 5-14

5.3.2 SYSCLK Change ............................................................................................................................ 5-16

5.3.3 WDTCLK Source Change .............................................................................................................. 5-16

5.4 Power Management ............................................................................................................................... 5-17

5.4.1 Operation Modes ............................................................................................................................ 5-17

5.4.2 Low Power Modes and Wake-Up ................................................................................................... 5-18

5.5 External Events (External Interrupts and Wake-up Event) .................................................................... 5-24

5.5.1 Operating Mode .............................................................................................................................. 5-24

5.5.2 Idle Modes ...................................................................................................................................... 5-25

5.5.3 Stop Modes ..................................................................................................................................... 5-25

5.6 Reset Management ................................................................................................................................ 5-26

5.6.1 nRESET Pin Reset (NRST) ............................................................................................................ 5-27

5.6.2 Power-On Reset (PORST) ............................................................................................................. 5-27

5.6.3 LVD Reset (LVDRST) ..................................................................................................................... 5-27

5.6.4 External Main Clock Monitor Reset (EMCMRST) .......................................................................... 5-29

5.6.5 Watchdog Timer Reset (WDTRST) ................................................................................................ 5-29

5.6.6 Software Reset (SWRST) ............................................................................................................... 5-29

5.6.7 CPU Request Reset (SYSRST) ..................................................................................................... 5-29

5.7 Basic Timer ............................................................................................................................................ 5-30

5.8 Fast Wake-up ......................................................................................................................................... 5-32

5.9 Register Description ............................................................................................................................... 5-34

5.9.1 Register Map Summary .................................................................................................................. 5-34

5.10 Guide-Clock Initialization ..................................................................................................................... 5-76

6 COMPARATOR .............................................................................................6-1

6.1 Overview .................................................................................................................................................. 6-1

6.1.1 Features ............................................................................................................................................ 6-1

6.1.2 Pin Description.................................................................................................................................. 6-1

6.2 Functional Description ............................................................................................................................. 6-2

6.2.1 Block Diagram .................................................................................................................................. 6-3

6.2.2 Comparator Input .............................................................................................................................. 6-4

6.2.3 Comparator Output ........................................................................................................................... 6-4

6.2.4 IMC Output-Off Control ..................................................................................................................... 6-4

6.2.5 Interrupt ............................................................................................................................................ 6-4

6.3 Register Description ................................................................................................................................. 6-5

6.3.1 Register Map Summary .................................................................................................................... 6-5

7 PULSE POSITION DECODER ......................................................................7-1

7.1 Overview .................................................................................................................................................. 7-1

7.1.1 Features ............................................................................................................................................ 7-1

7.1.2 Pin Description.................................................................................................................................. 7-1

7.2 Functional Description ............................................................................................................................. 7-2

7.2.1 Block Diagram .................................................................................................................................. 7-2

7.2.2 Operating Mode ................................................................................................................................ 7-3

7.3 Register Description ................................................................................................................................. 7-6

7.3.1 Register Map Summary .................................................................................................................... 7-6

8 GENERAL PURPOSE I/O (GPIO) .................................................................8-1

8.1 Overview .................................................................................................................................................. 8-1

8.1.1 Features ............................................................................................................................................ 8-1

8.1.2 Pin Description.................................................................................................................................. 8-1

8.2 Functional Description ............................................................................................................................. 8-2

8.2.1 GPIO Configuration .......................................................................................................................... 8-2

8.2.2 Input Configuration ........................................................................................................................... 8-2

8.2.3 Output Configuration ........................................................................................................................ 8-3

8.2.4 Operation Mode ................................................................................................................................ 8-3

8.2.5 Interrupt ............................................................................................................................................ 8-4

8.3 Register Description ................................................................................................................................. 8-5

8.3.1 Register Map Summary .................................................................................................................... 8-5

9 INTERNAL FLASH CONTROLLER (IFC) .....................................................9-1

9.1 Overview .................................................................................................................................................. 9-1

9.1.1 Features ............................................................................................................................................ 9-1

9.2 Functional Description ............................................................................................................................. 9-2

9.2.1 Organization ..................................................................................................................................... 9-3

9.2.2 Smart Option ..................................................................................................................................... 9-6

9.2.3 Modes ............................................................................................................................................. 9-10

9.2.4 Flow Chart ...................................................................................................................................... 9-16

9.2.5 Error ................................................................................................................................................ 9-22

9.3 Register Description ............................................................................................................................... 9-26

9.3.1 Register Map Summary .................................................................................................................. 9-26

10 INVERTER MOTOR CONTROLLER (IMC) ...............................................10-1

10.1 Overview .............................................................................................................................................. 10-1

10.1.1 Features ........................................................................................................................................ 10-1

10.1.2 Pin Description.............................................................................................................................. 10-1

10.2 Functional Description ......................................................................................................................... 10-2

10.2.1 Block Diagram .............................................................................................................................. 10-2

10.2.2 Operation ...................................................................................................................................... 10-3

10.2.3 Phase Signal Generation .............................................................................................................. 10-5

10.3 Register Description ........................................................................................................................... 10-25

10.3.1 Register Map Summary .............................................................................................................. 10-25

11 INTERRUPT CONTROLLER (INTC) .........................................................11-1

11.1 Overview .............................................................................................................................................. 11-1

11.1.1 Features ........................................................................................................................................ 11-1

11.2 Functional Description ......................................................................................................................... 11-2

11.2.1 Interrupt Vector ............................................................................................................................. 11-2

11.2.2 Block Diagram .............................................................................................................................. 11-4

11.3 Register Description ............................................................................................................................. 11-6

11.3.1 Register Map Summary ................................................................................................................ 11-6

12 I/O CONFIGURATION ...............................................................................12-1

12.1 Overview .............................................................................................................................................. 12-1

12.1.1 Features ........................................................................................................................................ 12-1

12.2 Functional Description ......................................................................................................................... 12-2

12.2.1 General Description ...................................................................................................................... 12-2

12.2.2 Peripheral Configuration ............................................................................................................... 12-2

12.3 Register Description ............................................................................................................................. 12-4

12.3.1 Register Map Summary ................................................................................................................ 12-4

13 OPERATIONAL AMPLIFIER .....................................................................13-1

13.1 Overview .............................................................................................................................................. 13-1

13.1.1 Features ........................................................................................................................................ 13-1

13.1.2 Pin Description.............................................................................................................................. 13-1

13.1.3 Block Diagram .............................................................................................................................. 13-2

13.1.4 Gain Generation Circuit ................................................................................................................ 13-3

13.2 Register Description ............................................................................................................................. 13-4

13.2.1 Register Map Summary ................................................................................................................ 13-4

14 PULSE WIDTH MODULATION .................................................................14-1

14.1 Overview .............................................................................................................................................. 14-1

14.1.1 Features ........................................................................................................................................ 14-1

14.1.2 Pin Description.............................................................................................................................. 14-1

14.2 Functional Description ......................................................................................................................... 14-2

14.2.1 Block Diagram .............................................................................................................................. 14-2

14.2.2 General Description ...................................................................................................................... 14-3

14.2.3 Clock and Operation Frequency ................................................................................................... 14-4

14.2.4 Period ........................................................................................................................................... 14-4

14.2.5 PULSE Level ................................................................................................................................ 14-4

14.2.6 nPULSE Width .............................................................................................................................. 14-4

14.2.7 IDLE Level .................................................................................................................................... 14-5

14.2.8 Parameter Relationship ................................................................................................................ 14-5

14.2.9 Extension Bit ................................................................................................................................. 14-8

14.3 Register Description ........................................................................................................................... 14-13

14.3.1 Register Map Summary .............................................................................................................. 14-13

15 SERIAL PERIPHERAL INTERFACE (SPI) ................................................15-1

15.1 Overview .............................................................................................................................................. 15-1

15.1.1 Features ........................................................................................................................................ 15-1

15.1.2 Pin Description.............................................................................................................................. 15-2

15.2 Functional Description ......................................................................................................................... 15-3

15.2.1 Block Diagram .............................................................................................................................. 15-3

15.2.2 Operation ...................................................................................................................................... 15-4

15.3 Register Description ........................................................................................................................... 15-18

15.3.1 Register Map Summary .............................................................................................................. 15-18

16 TIMER/COUNTER .....................................................................................16-1

16.1 Overview .............................................................................................................................................. 16-1

16.1.1 Features ........................................................................................................................................ 16-1

16.1.2 Pin Description.............................................................................................................................. 16-2

16.2 Functional Description ......................................................................................................................... 16-3

16.2.1 Block Diagram .............................................................................................................................. 16-3

16.2.2 Counter Size ................................................................................................................................. 16-3

16.2.3 Counter Clock ............................................................................................................................... 16-4

16.2.4 Debug Option................................................................................................................................ 16-4

16.2.5 ADC Trigger Source ..................................................................................................................... 16-4

16.2.6 Overflow Mode.............................................................................................................................. 16-5

16.2.7 Period Mode ................................................................................................................................. 16-8

16.2.8 Interrupt ...................................................................................................................................... 16-17

16.3 Register Description ........................................................................................................................... 16-18

16.3.1 Register Map Summary .............................................................................................................. 16-18

17 UNIVERSAL SYNCHRONOUS/ASYNCHRONOUS

RECEIVER/TRANSMITTER ...........................................................................17-1

17.1 Overview .............................................................................................................................................. 17-1

17.1.1 Feature ......................................................................................................................................... 17-2

17.1.2 Pin Description.............................................................................................................................. 17-2

17.2 Functional Description ......................................................................................................................... 17-3

17.2.1 Block Diagram .............................................................................................................................. 17-3

17.2.2 BaudRate Generator .................................................................................................................... 17-4

17.2.3 General Description ...................................................................................................................... 17-4

17.3 Asynchronous Mode ............................................................................................................................ 17-5

17.3.1 Synchronous Mode ....................................................................................................................... 17-5

17.4 Receiver ............................................................................................................................................. 17-12

17.4.1 Asynchronous Receiver .............................................................................................................. 17-12

17.4.2 Synchronous Receiver ............................................................................................................... 17-13

17.5 Transmitter ......................................................................................................................................... 17-15

17.5.1 General Description .................................................................................................................... 17-15

17.5.2 Time-Guard................................................................................................................................. 17-16

17.5.3 Multi-Drop Mode ......................................................................................................................... 17-16

17.6 Break .................................................................................................................................................. 17-17

17.6.1 Transmit Break ........................................................................................................................... 17-17

17.6.2 Receive Break ............................................................................................................................ 17-17

17.6.3 Interrupts ..................................................................................................................................... 17-17

17.6.4 Test Modes ................................................................................................................................. 17-18

17.6.5 Smart Card Protocol ................................................................................................................... 17-18

17.6.6 Character Transmission to Smart Card ...................................................................................... 17-19

17.6.7 Character Reception from Smart Card ....................................................................................... 17-20

17.6.8 USART Configuration in Smart Card Mode ................................................................................ 17-20

17.7 Programming Examples ..................................................................................................................... 17-21

17.8 Register Description ........................................................................................................................... 17-22

17.8.1 Register Map Summary .............................................................................................................. 17-22

17.9 4 to 40 MHz Asynchronous Mode ...................................................................................................... 17-46

18 WATCHDOG TIMER..................................................................................18-1

18.1 Overview .............................................................................................................................................. 18-1

18.1.1 Feature ......................................................................................................................................... 18-1

18.2 Functional Description ......................................................................................................................... 18-2

18.2.1 Block Diagram .............................................................................................................................. 18-2

18.2.2 Watchdog Timer Functionality ...................................................................................................... 18-3

18.2.3 Watchdog Timer Events ............................................................................................................... 18-4

18.3 Register Description ............................................................................................................................. 18-5

18.3.1 Register Map Summary ................................................................................................................ 18-5

19 ELECTRICAL DATA..................................................................................19-1

19.1 Overview .............................................................................................................................................. 19-1

19.2 Absolute Maximum Ratings ................................................................................................................. 19-1

19.3 Recommended Operating Conditions .................................................................................................. 19-2

19.4 I/O Characteristics ............................................................................................................................... 19-3

19.5 I/O AC Electrical Characteristics .......................................................................................................... 19-4

19.6 Reset Input Characteristics .................................................................................................................. 19-5

19.7 External Interrupt Input Characteristics ............................................................................................... 19-6

19.8 Oscillator Characteristics ..................................................................................................................... 19-7

19.8.1 External Main Oscillator Characteristics ....................................................................................... 19-7

19.8.2 Internal Main Oscillator Characteristics ........................................................................................ 19-8

19.9 Current Consumption ........................................................................................................................... 19-9

19.10 PLL Characteristics .......................................................................................................................... 19-10

19.11 LVD Characteristics ......................................................................................................................... 19-11

19.12 12-bit ADC Electrical Characteristics ............................................................................................... 19-12

19.13 Comparator Electrical Characteristics ............................................................................................. 19-13

19.14 OP-AMP Electrical Characteristics .................................................................................................. 19-14

19.15 Flash Memory Characteristics ......................................................................................................... 19-15

19.16 SPI (SSP) Timing Characteristics .................................................................................................... 19-16

19.17 ESD Characteristics ......................................................................................................................... 19-17

20 PACKAGE SPECIFICATION .....................................................................20-1

20.1 Overview .............................................................................................................................................. 20-1

List of Figures

Figure

Number

Title

Page

Number

Figure 1-1

Block Diagram................................................................................................................................... 1-9

Figure 2-1

Figure 2-2

Figure 2-3

Figure 2-4

Figure 2-5

Pin Map Diagram .............................................................................................................................. 2-2

Pin Circuit Type A (P0.0 to P0.11 and P0.18 to P0.31) .................................................................. 2-11

Pin Circuit Type B (P0.12 to P0.17) ................................................................................................ 2-12

Pin Circuit Type C (MODE1 and MODE0) ...................................................................................... 2-12

Pin Circuit Type D (nRESET) ......................................................................................................... 2-13

Figure 3-1

S3FN429 Memory Map ..................................................................................................................... 3-1

Figure 4-1

Figure 4-2

Figure 4-3

Figure 4-4

Figure 4-5

Figure 4-6

Figure 4-7

Figure 4-8

Figure 4-9

ADC Block Diagram .......................................................................................................................... 4-2

ADC Operation Timing Diagram ....................................................................................................... 4-4

One-Shot Mode, Single Channel Conversion ................................................................................... 4-7

One-Shot Mode, Multi-Channel Conversion ..................................................................................... 4-7

Continuous Mode, Single-Channel Conversion ................................................................................ 4-8

Continuous Mode, Multi-Channel Conversion .................................................................................. 4-8

ADC Calibration Scheme ................................................................................................................ 4-11

2 Point Calibration .......................................................................................................................... 4-12

ADC Flowchart ................................................................................................................................ 4-14

Figure 5-1

Figure 5-2

Figure 5-3

Figure 5-4

Figure 5-5

Figure 5-6

Figure 5-7

Figure 5-8

Figure 5-9

Figure 5-10

Figure 5-11

Figure 5-12

Figure 5-13

Figure 5-14

Figure 5-15

Figure 5-16

Figure 5-17

Figure 5-18

Figure 5-19

Figure 5-20

Figure 5-21

Figure 5-22

System Clock Tree Block Diagram ................................................................................................... 5-4

System Clock Selection .................................................................................................................... 5-5

Crystal/Ceramic Resonator or External Clock Circuit ....................................................................... 5-7

PLL (Phase-Locked Loop) Block Diagram ....................................................................................... 5-9

Clock Monitor Function ................................................................................................................... 5-11

External Main Oscillator Fail and Reset ......................................................................................... 5-12

End of Clock Fail ............................................................................................................................. 5-13

Clock Control State Machine .......................................................................................................... 5-14

The Change Clock Source of SYSCLK .......................................................................................... 5-15

Instruction for IDLE and STOP ..................................................................................................... 5-18

Interrupt and Event ....................................................................................................................... 5-22

Different Handling Process for Interrupt and Event in IDLE or Stop Mode .................................. 5-23

External Interrupt Diagram ............................................................................................................ 5-25

Reset Sources .............................................................................................................................. 5-26

LVD Block Diagram ...................................................................................................................... 5-28

RESET@EMCLK .......................................................................................................................... 5-31

Start-Up with Basic Timer ............................................................................................................. 5-31

Fast Wake-Up ............................................................................................................................... 5-32

Basic Timer and Exit of Stop Mode when FWAKE is "0".............................................................. 5-32

Basic Timer and Exit of Stop Mode when FWAKE is "1" (SYSCLK = IMCLK) ............................. 5-33

Clock Initialization when Reset Value of SYSCLK is EMCLK ...................................................... 5-76

Clock Initialization when Reset Value of SYSCLK is IMCLK ........................................................ 5-77

Figure 6-1

Comparator Block Diagram .............................................................................................................. 6-3

Figure 7-1

Figure 7-2

Figure 7-3

Figure 7-4

Figure 7-5

PPD Block Diagram .......................................................................................................................... 7-2

Counter Operation (4 Multiplication Mode) ....................................................................................... 7-3

Counter Operation (1 Multiplication Mode) ....................................................................................... 7-4

Counter Operation (Type 1) .............................................................................................................. 7-5

Counter Operation (Type 2) .............................................................................................................. 7-5

Figure 9-1

Figure 9-2

Figure 9-3

Figure 9-4

Figure 9-5

Figure 9-6

Figure 9-7

Figure 9-8

Figure 9-9

Figure 9-10

Figure 9-11

Figure 9-12

Figure 9-13

Flash Block Diagram (Non Pre-Fetch) .............................................................................................. 9-2

Flash Block Diagram (Pre-Fetch) ..................................................................................................... 9-2

Physical Configuration ...................................................................................................................... 9-3

Normal Program Flowchart ............................................................................................................. 9-16

Page Erase Flowchart .................................................................................................................... 9-17

Sector Erase Flowchart .................................................................................................................. 9-18

Entire Erase Flowchart ................................................................................................................... 9-19

Smart Option Program Flowchart ................................................................................................... 9-20

Smart Option Erase Flowchart ........................................................................................................ 9-21

Error0 Condition ............................................................................................................................ 9-22

Error0 Condition ............................................................................................................................ 9-23

Error1 Condition ............................................................................................................................ 9-24

Error2 Condition ............................................................................................................................ 9-25

Figure 10-1

Figure 10-2

Figure 10-3

Figure 10-4

Figure 10-5

Figure 10-6

Figure 10-7

Figure 10-8

Figure 10-9

Figure 10-10

Figure 10-11

Figure 10-12

Figure 10-13

Figure 10-14

Figure 10-15

Figure 10-16

Figure 10-17

Figure 10-18

Figure 10-19

Figure 10-20

Figure 10-21

Figure 10-22

Figure 10-23

Figure 10-24

Figure 10-25

Figure 10-26

Figure 10-27

Figure 10-28

Figure 10-29

IMC Block Diagram ....................................................................................................................... 10-2

Tri-Angular Wave Signal Generation ............................................................................................ 10-3

Saw-Tooth Wave Signal Generation ............................................................................................ 10-4

Tri-Angular Wave (No SWAP, a Low Start PWMxUy, and High Start PWMxDy) ........................ 10-5

Tri-Angular Wave Duty (No SWAP, a Low Start PWMxUy, and High Start PWMxDy) ................ 10-6

Tri-Angular Wave (SWAP, a Low Start PWMxUy, and High Start PWMxDy) .............................. 10-7

Tri-Angular Wave Duty (SWAP, a Low Start PWMxUy, and High Start PWMxDy) ...................... 10-8

Tri-Angular Wave (No SWAP, a Low Start PWMxUy, and Low Start PWMxDy) ......................... 10-9

Tri-Angular Wave (SWAP, a Low Start PWMxUy, and Low Start PWMxDy) ............................. 10-10

Tri-Angular Wave (No SWAP, a High Start PWMxUy, and Low Start PWMxDy) .................... 10-11

Tri-Angular Wave Duty (No SWAP, a High Start PWMxUy, and Low Start PWMxDy) ............ 10-12

Tri-Angular Wave (SWAP, a High Start PWMxUy, and Low Start PWMxDy) .......................... 10-13

Tri-Angular Wave (No SWAP, a High Start PWMxUy, and High Start PWMxDy) .................... 10-14

Tri-Angular Wave (SWAP, a High Start PWMxUy, and High Start PWMxDy) ......................... 10-15

Saw-Tooth Wave (No SWAP, a Low Start PWMxUy, and High Start PWMxDy) ..................... 10-16

Saw-Tooth Wave Duty (No SWAP, a Low Start PWMxUy, and High Start PWMxDy) ............ 10-17

Saw-Tooth Wave (SWAP, a Low Start PWMxUy, and High Start PWMxDy) .......................... 10-18

Saw-Tooth Wave (No SWAP, a Low Start PWMxUy, and Low Start PWMxDy) ...................... 10-19

Saw-Tooth Wave (SWAP, a Low Start PWMxUy, and Low Start PWMxDy) ........................... 10-20

Saw-Tooth Save (No SWAP, a High Start PWMxUy, and Low Start PWMxDy) ...................... 10-21

Saw-Tooth Wave (SWAP, a High Start PWMxUy, and Low Start PWMxDy) .......................... 10-22

Saw-Tooth Wave (No SWAP, a High Start PWMxUy, and High Start PWMxDy) .................... 10-23

Saw-Tooth Wave (SWAP, a High Start PWMxUy, and High Start PWMxDy) .......................... 10-24

Synchronous Write at Zero and IMC_TCR Match (SYNCSEL = 00'b, NUMSKIP = 00000'b) . 10-33

Synchronous Write at Zero and IMC_TCR Match (SYNCSEL = 00'b, NUMSKIP = 00000'b) . 10-34

Synchronous Write at Zero Match (SYNCSEL = 01'b, NUMSKIP = 00000'b) ......................... 10-34

Synchronous Write at IMC_TCR Match (SYNCSEL = 10'b, NUMSKIP = 00000'b) ................. 10-35

Synchronous Write at Zero and IMC_TCR Match (SYNCSEL = 00'b, NUMSKIP = 00001'b) . 10-35

Synchronous Write at Zero Match (SYNCSEL = 01'b, NUMSKIP = 00001'b) ......................... 10-36

Figure 10-30

Figure 10-31

Synchronous Write at IMC_TCR Match (SYNCSEL = 10'b, NUMSKIP = 00001'b) ................. 10-36

Skip Control of ADC Trigger Signal Interrupt ............................................................................ 10-37

Figure 11-1

Interrupt Block Diagram ................................................................................................................ 11-4

Figure 13-1

OP-AMP Block Diagram ............................................................................................................... 13-2

Figure 14-1

Figure 14-2

Figure 14-3

Figure 14-4

Figure 14-5

Figure 14-6

Figure 14-7

Figure 14-8

Figure 14-9

Pulse Width Modulation (PWM) Block Diagram ........................................................................... 14-2

PWM Cycle Description ................................................................................................................ 14-3

PWM Basic Waveform (OUTSL = 1, PWM Period = 0x40, Pulse = 0x0, 0x1, 0x20, 0x3F, 0x40) 14-6

PWM Basic Waveform (OUTSL = 0, PWM Period = 0x40, Pulse = 0x0, 0x1, 0x20, 0x3F, 0x40) 14-7

Extended PWM Waveform (PWM Period = 0x40, Pulse = 0x3E, PWMEX0) .............................. 14-9

Extended PWM Waveform (PWM Period = 0x40, Pulse = 0x3E, PWMEX1) ............................ 14-10

Extended PWM Waveform (PWM Period = 0x40, Pulse = 0x3E, PWMEX1 and PWMEX0) ..... 14-11

Extended PWM Waveform (High Start) ...................................................................................... 14-12

Extended PWM Waveform (Low Start) ....................................................................................... 14-12

Figure 15-1

Figure 15-2

Figure 15-3

Figure 15-4

Figure 15-5

Figure 15-6

Figure 15-7

Figure 15-8

Figure 15-9

SSP Block Diagram ...................................................................................................................... 15-3

Motorola SPI Frame Format (Single Transfer) with SPO = 0 and SPH = 0 ............................... 15-10

Motorola SPI Frame Format (Continuous Transfer) with SPO = 0 and SPH = 0 ....................... 15-11

Motorola SPI Frame Format with SPO = 0 and SPH = 1 ........................................................... 15-12

Motorola SPI Frame Format (Single Transfer) with SPO = 1 and SPH = 0 ............................... 15-13

Motorola SPI Frame Format (Continuous Transfer) with SPO = 1 and SPH = 0 ....................... 15-13

Motorola SPI Frame Format with SPO = 1 and SPH = 1 ........................................................... 15-14

PrimeCell SSP Master Coupled to Two Slaves .......................................................................... 15-15

SPI Master Coupled to two PrimeCell SSP Slaves .................................................................... 15-16

Figure 16-1

Figure 16-2

Figure 16-3

Figure 16-4

Figure 16-5

Figure 16-6

Figure 16-7

Figure 16-8

Figure 16-9

Figure 16-10

Figure 16-11

Figure 16-12

Figure 16-13

TC Block Diagram ......................................................................................................................... 16-3

Match and Overflow Operation Timing ......................................................................................... 16-5

Counter Values According to START, STOPCLEAR and STOPHOLD ....................................... 16-6

Capture Operation Timing ............................................................................................................ 16-7

Period Mode Timing ...................................................................................................................... 16-8

Interval Operation ......................................................................................................................... 16-9

PWM Operation .......................................................................................................................... 16-10

PWM Extension Waveform ......................................................................................................... 16-11

PWM Waveform with OUTSL = 0 ............................................................................................... 16-13

PWM Waveform with OUTSL = 1 ............................................................................................. 16-13

PWM Waveform Under IDLE State .......................................................................................... 16-15

PWM Waveform with STOPHOLD = 1, STOPCLEAR = 0 ....................................................... 16-15

PWM Waveform with STOPCLEAR = 1 ................................................................................... 16-16

Figure 17-1

Figure 17-2

Figure 17-3

Figure 17-4

Figure 17-5

Figure 17-6

Figure 17-7

USART Block Diagram ................................................................................................................. 17-3

USART BaudRate Generator Block Diagram ............................................................................... 17-5

Asynchronous Mode, Start Bit Detection .................................................................................... 17-12

Asynchronous Mode, Character Reception ................................................................................ 17-12

Synchronous Mode, Character Reception .................................................................................. 17-13

IDLE Flag .................................................................................................................................... 17-14

Synchronous and Asynchronous Modes, Character Transmission............................................ 17-15

Figure 17-8

Figure 17-9

Smart Card Transmission Error .................................................................................................. 17-19

Error Signaling on Reception ...................................................................................................... 17-20

Figure 18-1

Watchdog Timer Block Diagram ................................................................................................... 18-2

Figure 19-1

Figure 19-2

Figure 19-3

Input Timing for nRESET .............................................................................................................. 19-5

Input Timing for External Interrupt ................................................................................................ 19-6

SPI Interface Transmit/Receive Timing ...................................................................................... 19-16

Figure 20-1

44-QFP-1010 Package Dimension ............................................................................................... 20-2

List of Tables

Table

Number

Title

Page

Number

Table 2-1

Table 2-2

Table 2-3

Table 2-4

Table 2-5

Table 2-6

Table 2-7

Pin Assignment by Pin Number Order ............................................................................................... 2-3

Summary of Mirror Pins ..................................................................................................................... 2-5

Power Pin Description ........................................................................................................................ 2-6

System Pin Description ...................................................................................................................... 2-7

Function Pin Description .................................................................................................................... 2-9

Debug Interface Pin Description ...................................................................................................... 2-10

Flash Serial Program Pin Description .............................................................................................. 2-10

Table 3-1

Table 3-2

Table 3-3

S3FN429 Memory Map ...................................................................................................................... 3-1

Core Special Function Register Map ................................................................................................. 3-2

Peripheral Memory Map ..................................................................................................................... 3-3

Table 4-1

Table 4-2

Table 4-3

Table 4-4

ADC Pin Description .......................................................................................................................... 4-1

ADC Input and Digital Output ............................................................................................................. 4-3

CCNT Values and the Number of Conversions ................................................................................. 4-5

ICNUMx Value and Selected Input .................................................................................................... 4-6

Table 5-1

Table 5-2

Table 5-3

Table 5-4

Table 5-5

Table 5-6

Table 5-7

Table 5-8

Table 5-9

Table 5-10

Table 5-11

Table 5-12

Table 5-13

Table 5-14

Clock Definition .................................................................................................................................. 5-4

Summary of Smart Option for Clock Manager ................................................................................... 5-6

Clock Status at Reset and Wake-Up ................................................................................................. 5-6

Clock Monitor Control Bit ................................................................................................................. 5-11

Operation Mode Definition ............................................................................................................... 5-14

IDLE on Sleep-Now ......................................................................................................................... 5-20

IDLE on Sleep-on-Exit ..................................................................................................................... 5-20

Clock Status on STOP and Wake-Up .............................................................................................. 5-21

External Event Function ................................................................................................................... 5-24

Reset ID Flag ................................................................................................................................. 5-26

256 Counting Time by BT .............................................................................................................. 5-30

SYSCLK Divider Value .................................................................................................................. 5-60

PMS Value Table ........................................................................................................................... 5-64

The External Event Sources and Pin Assignment ......................................................................... 5-69

Table 6-1

Pin Description ................................................................................................................................... 6-1

Table 7-1

PPD Pin Description .......................................................................................................................... 7-1

Table 8-1

GPIO Pin Description ......................................................................................................................... 8-1

Table 9-1

Table 9-2

Flash Configuration ............................................................................................................................ 9-1

Base Address of Each Sector ............................................................................................................ 9-4

Table 9-3

Table 9-4

Table 9-5

Table 9-6

Table 9-7

Base Address of Each Page .............................................................................................................. 9-5

Configuration Smart Option Address and Control Bits ...................................................................... 9-6

Protection Smart Option Address and Control Bits ............................................................................ 9-8

Description of Interrupt Sources ...................................................................................................... 9-14

Pins Used to Read/Write/Erase the Flash ROM in Tool Program Mode ......................................... 9-15

Table 10-1

IMC Pin Description ....................................................................................................................... 10-1

Table 11-1

Table 11-2

Core Interrupt Vector ..................................................................................................................... 11-2

Device Interrupt Vector .................................................................................................................. 11-3

Table 12-1

I/O Function Mode Configuration ................................................................................................... 12-2

Table 13-1

Table 13-2

OP-AMP Pin Description ................................................................................................................ 13-1

Gain Configuration Table ............................................................................................................... 13-3

Table 14-1

Table 14-2

Table 14-3

PWM Pin Description ..................................................................................................................... 14-1

PERIOD and PULSE Field Relationship in Normal Mode ............................................................. 14-5

PWM Output................................................................................................................................... 14-6

Table 15-1

SSP Pin Description ....................................................................................................................... 15-2

Table 16-1

Table 16-2

Table 16-3

Pin Description ............................................................................................................................... 16-2

PWM Extension Bits .................................................................................................................... 16-11

PWM Output Polarity According to Control Bits ........................................................................... 16-14

Table 17-1

Table 17-2

Table 17-3

Table 17-4

USART Pin Description .................................................................................................................. 17-2

Asynchronous Mode (SYNC = 0) ................................................................................................... 17-6

Synchronous Mode (SYNC = 1) .................................................................................................... 17-9

Asynchronous Mode (SYNC = 0) ................................................................................................. 17-46

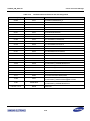

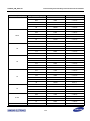

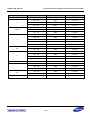

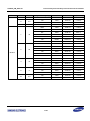

Table 19-1

Table 19-2

Table 19-3

Table 19-4

Table 19-5

Table 19-6

Table 19-7

Table 19-8

Table 19-9

Table 19-10

Table 19-11

Table 19-12

Table 19-13

Table 19-14

Table 19-15

Absolute Maximum Ratings ........................................................................................................... 19-1

Recommended Operating Conditions ............................................................................................ 19-2

I/O Characteristics ......................................................................................................................... 19-3

Reset Input Characteristics ............................................................................................................ 19-4

Reset Input Characteristics ............................................................................................................ 19-5

External interrupt Input Characteristics .......................................................................................... 19-6

External Main Oscillator Characteristics ........................................................................................ 19-7

Internal Main Oscillator Characteristics ......................................................................................... 19-8

Current Consumption at 5.5 V ....................................................................................................... 19-9

PLL Characteristics .................................................................................................................... 19-10

LVD Characteristics ................................................................................................................... 19-11

ADC Characteristics ................................................................................................................... 19-12

Comparator Electrical Characteristics ....................................................................................... 19-13

OP-AMP Electrical Characteristics ............................................................................................ 19-14

Flash Memory Characteristics ................................................................................................... 19-15

Table 19-16

Table 19-17

SPI Timing Characteristics ......................................................................................................... 19-16

ESD Characteristics ................................................................................................................... 19-17

Table 20-1

Package Specification Information................................................................................................. 20-1

List of Conventions

Register RW Access Type Conventions

Type

Definition

Description

R

Read Only

The application has permission to read the Register field. Writes to read-only fields

have no effect.

W

Write Only

The application has permission to write in the Register field.

RW

Read & Write

The application has permission to read and writes in the Register field. The

application sets this field by writing 1'b1 and clears it by writing 1'b0.

Register Value Conventions

Expression

Description

x

Undefined bit

X

Undefined multiple bits

?

Undefined, but depends on the device or pin status

Device dependent

Pin value

The value depends on the device

The value depends on the pin status