Download TR5-F40W User Manual

Transcript

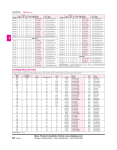

Design Tools Quartus II 12.0 Borland C++ Builder 6.0 Demonstration Source Code Location Quartus Project: PCIE_ImageProcess Borland C++ Project: PCIe_SW_KIT\PCIE_ImageProcess FPGA Application Design This demonstration uses the DMA channel of PCIe IP to download/upload the image into the internal RAM of FPGA, and controls the user register that switches the function which inverts the image data from the internal RAM. PC Application Design The software design defines some constant based on FPGA design as shown below: TR5-F40W User Manual 95 www.terasic.com August 29, 2014