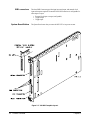

Download Agilent E1482B VXI-MXI Bus Extender User`s Manual

Transcript