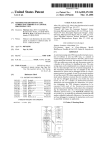

Download Method for symbolic simulation of circuits having non

Transcript

US007818158B2 (12) Ulllted States Patent (10) Patent N0.: McDonald et a]. (54) (45) Date of Patent: 6,459,324 B1* 10/2002 Neacsu et a1. ............. .. 327/379 CIRCUITS HAVING NON-DIGITAL NODE 6,577,992 B1 * VOLTAGES 6,634,012 B2 7,006,961 (Us) 703/14 B2 * 2/2006 Zhou Mandell et al. et al. . . . . . .............. . . . . . . . . . . . . .. 703/14 7,013,253 B1* 3/2006 Cong et a1. ................. .. 703/14 7,049,875 B2 * 5/2006 Tsividis .................... .. 327/308 7,143,021 B1 * 11/2006 McGaughy et al. ......... .. 703/14 Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 1153 days. (Continued) (21) APP1-NO-I 11/2331323 (22) Tcherniaev et al. ......... .. 703/14 * Assigneei SyIwPSyS, 1119-, Mountain View, CA Notice: 6/2003 10/2003 Zhong et al. ................. .. 716/5 6,662,149 B1* 12/2003 Devgan et al. (Us); Hsinwei smriti Gupta’ Chou’ San Sunnyvale’ Jose’ CA (Us) (*) Oct. 19, 2010 METHOD FOR SYMBOLIC SIMULATION OF (75) Inventors: Clayton B- McDonald’ Chapel Hill’ NC (73) US 7,818,158 B2 Filed: OTHER PUBLICATIONS Sep. 21, 2005 Understanding Semiconductor Devices by Sima Dimitrijev ISBN 0-19-513186-X Publication year 2000 p. 4-5.* (65) Prior Publication Data US 2007/0078638 A1 (51) Apr. 5, 2007 ( Continued ) Primary ExamineriKamini S Shah Assistant ExamineriAkesh Saxena Int. Cl. G06F 17/50 G06G 7/48 (2006.01) (2006.01) (74) Attorney, Agent, or FirmiSilicon Valley Patent Group LLP; Omkar Suryadevara (52) U.S.Cl. ........................................... .. 703/14; 703/3 (58) Field of Classi?cation Search ................. .. 703/19, (57) ABSTRACT 703/ 14, 3 See application ?le for complete search history. _ (56) In a computer simulation of an analog device in a digital References Clted circuit, a piece-Wise linear lookup table is used to determine the channel resistance of the transistors in the analog device, allowing the node voltages to take on non-digital values. The piece-Wise linear lookup table contains a set of channel resis U.S. PATENT DOCUMENTS 5,264,785 A * 11/1993 Greason ................... .. 323/350 5,313,398 A * 5/1994 Rohrer etal. 5,373,457 A * 12/1994 George et a1. 5,553,008 A * 9/1996 Huang et a1. 5,675,502 A * 10/1997 Cox .. ... ... ... . A * 12/1999 6,134,513 A * 10/2000 6,190,433 B1* 6,269,277 B1 * 2/2001 7/2001 Wang et a1. Gopal tances corresponding respectively to gate-to-source voltages. 716/6 and voltages in the circuit as a function of symbolic inputs. The program can analyze circuits containing more than tWo . . . .. 5,686,863 A * 11/1997 Whiteside 5,687,355 A * 11/1997 Joardaret a1. 5,692,158 A * 11/1997 Degeneffetal. 5,999,718 703/14 703/2 703/14 The program uses multi-terminal binary decision graphs (MTBDDs) to represent non-digital resistances, capacitances 330/260 716/20 voltage sources by modeling voltage sources With voltage 703/2 ..... . . . .. dividers betWeen the maximum and minimum voltages in the 703/2 Circuit ....................... .. 703/14 ' Van Fleet etal. ............. .. 71/18 Hershenson et al. ........ .. 700/97 28 Claims, 14 Drawing Sheets | MEMORY Piece-VWseLinear LookupTable 35 “mum “mum Node Name “Damage A1 ‘ A2 A3 _ (LTZZ'QTE'E'Q, B1 B2 B3 Gate Node K1 K2 K3 Ca acitanoe C1 List of transistors connected to node D1 C2 03 L1 M1 L2 M2 L3 M3 D2 D3 source Node Drain Node F'lW/L Lookup Table N1 N2 N3 J E2 E3 Channel VWdth O1 O2 03 Channel Length P1 Type(NurP) 01 P2 u: P3 as souroe or not?) Value (or range ofvalues)’ E1 ‘Tabla givm rea/ yaiue 38/ 340/ 356 US 7,818,158 B2 Page 2 TETA: Transistor-Level Engine for Timing Analysis by F. Dartu and L. T. Pileggi. Proceedings of the Design Automation by Conference, US. PATENT DOCUMENTS 7,353,157 B2 * 2001/0029601 A1* 4/2008 WasyncZuk et al. ......... .. 703/14 10/2001 Kimura et al. ..... .. 716/19 2002/0016704 A1* 2/2002 2003/0120473 A1* 2003/0208347 A1* Blanks ........ .. .. 6/2003 Jain et al. 703/14 703/14 11/2003 Huang .. 703/14 2004/0049370 A1 * 3/2004 Stanley et al. 2004/0117162 A1* 6/2004 OZis et al. .... .. . 703/2 703/14 2004/0148150 A1* Ashar et al. . Fertner et al. .. .. . 703/14 2005/0027491 A1* 7/2004 2/2005 2005/0143966 A1* 6/2005 McGaughy 2005/0149311 A1* 7/2005 2005/0149312 A1* 7/2005 McGaughy . 702/196 703/3 McGaughy . .. 703/14 .. 703/14 2005/0257178 A1* 11/2005 Daems et al. 2005/0273307 A1* 716/2 12/2005 Hemmett 2006/0069537 A1* 3/2006 2007/0261015 A1* 11/2007 2008/0033708 A1* Cao .. 703/14 ............... .. Morgenshtein et al. .. . 703/14 .. . 716/1 2/2008 Kanapka et al. ............. .. 703/14 OTHER PUBLICATIONS An amorphous-silicon thin-?lm transistor model including variable pp. 595-598, Jun. 1998* Microelectronic Circuits- Fourth Edition ; Sedra and Smith Jan. 1998; ISBN 0-19-511663-1; p. 366-369 and book cover.* Bahar, R. I. et al. “Algebraic Decision Diagrams And Their Applica tions”, ACM/IEEE International Conference on Computer Aided Design, Nov. 1993, pp. 4. SomenZi, F. “CUDD: CU Decision Diagram PackageiRelease 2.2. 0”, May 12, 1998, pp. 47. Bryant, R. E. “Graph-Based Algorithms For Boolean Function Manipulation”, IEEE Transactions on Computers, vol. C-35, No. 8, Aug. 1986, pp. 25. Andersen, H. R. et al. “Boolean Expression Diagrams”, In LICS, 1997, pp. 21. Kuehlmann, A. et al. “Equivalence Checking Using Cuts And Heaps”, Proceedings of the Design Automation Conference (DAC’97), Anaheim, CA, Jun. 1997, pp. 6. Bryant, R. E. et al. “Veri?cation Of Arithmetic Circuits Using Binary Moment Diagrams”, Software Tools for Technology Transfer, Springer-Verlag, vol. 3, No. 2, May 2001, pp. 18. Chen, Y.-A. et al. “PHDD: An Ef?cient Graph Representation For resistance effect by TaniZaWa, M.; Kikuta, S.; Nakagawa, N.; IshikaWa, K.; Kotani, N.; Miyoshi, H.;Simulation of Semiconductor Floating Point Circuit Veri?cation”, International Conference on Processes and Devices, 1996. SISPAD 96. 1996 International Con PhD Thesis titled “Symbolic Functional and Timing Veri?cation of ference onSep. 2-4, 1996 pp. 181-182.* Transistor Level Circuits,” Clayton B. McDonald, Apr. 9, 2001, Carnegie-Mellon University, 91 pages. Computing Logic-Stage Delays Using Circuit Simulation and Syrn Computer-Aided Design (ICCAD’97), Nov. 1997, pp. 6. bolic Elmore Analysis by Clayton B. McDonald Randal E. Bryant; IEEE 2001 p. 283-288* * cited by examiner US. Patent 0a. 19, 2010 Sheet 1 0114 US 7,818,158 B2 f _C 10 Q_ V In — Out \ 12 Prior Art V Fig. 1 t t1 ? (enable V Prior Art Fig. 2 f US. Patent 0a. 19, 2010 Sheet 3 0f 14 US 7,818,158 B2 REVISE CIRCUIT DESIGN TEXT EDITOR El 342 age CIRCUIT 336\ I 3 4 Lei-é —¥_ NON-DIGITAL n SIMULATION SYMBOLIC ° 3 3 34 Fig. 3B PROGRAM SIIIEI'IETIIW RESULTS US. Patent 0a. 19, 2010 US 7,818,158 B2 Sheet 4 0f 14 | |I l ii | i MEMORY | Piece-Wise Linear Lookup Table 3501 V95 v1 v2 v3 i P P1 P2 03 I | l Node Name A1 ! A2 A3 Type (voltage | source or not?) B1 B2 B3 I Capacitance C1 C2 C3 ! List of transistors | connected to node D1 D2 D3 i E1 E2 E3 I F1 F2 F3 i Value (or range of values)* CCR 352 ! / I *Table giving real value I (voltage) for any input | assignments (MTBDD) i I l 34 Legend 0_/ Fig. 3C Fig. Fig. 3C 3D I US. Patent 0a. 19, 2010 Sheet 5 0f 14 I I I I I US 7,818,158 B2 | i I CCR Name G1 G2 G3 ! 1 List of Nodes H1 Maximum Voltage |1 H2 |2 H3 J354 |3 I MinimumVoltage J1 J2 J3 l I l | Transistor List | (for each CCR) ! ! Gate Node Source Node K1 L1 K2 L2 K3 L3 | Drain Node M1 M2 M3 ' PNV/L ! Lookup Table N1 N2 N3 J | Channel Width 01 O2 03 i Channel Length P1 P2 P3 I Type (N or P) Q2 Q3 Q1 I I I I I 340/ Fig. 30 356 US. Patent 0a. 19, 2010 Sheet 6 0f 14 US 7,818,158 B2 @ 400 Get Event From J Queue " i402 4 404 Update Time Apply Event Value Event Queue Em pty? - - Simulation Determine J40 Complete Affected Nodes 6 List Of Affected Nodes Empty? N 408 Compute DC Value at J Node Using RC(n) 418 L Remove From Affected Nodes Y Change? A N ' 416 410 Compute J- Clean Events Delay 412 ' I414 Schedule New Event In Queue 7 Clean Events Fig. 4 US. Patent Oct. 19, 2010 Sheet 7 0f 14 __ US 7,818,158 B2 f 50 500 X ‘——<1 in Smalt m out Large 502 -/" V Fig. 5 t=0 ns t=1.1 ns out t=2.3 ns US. Patent 0a. 19, 2010 Sheet 8 0f 14 Fig. 7 804 816 US 7,818,158 B2 US. Patent 0a. 19, 2010 Sheet 9 0f 14 US 7,818,158 B2 a _|_ 902—/—_|_ Broken = aAbAC _|_"\—904 b c Fig. 9 102 Vdd 110 104 100 Fig. 10 US. Patent 0a. 19, 2010 Sheet 10 0114 US 7,818,158 B2 Channel Sheet Reslstance (p) Fig. 11 R1 R2 W T C R1 :> R2 W T Fig. 12 C * R1 US. Patent 0a. 19, 2010 Sheet 11 0114 / f US 7,818,158 B2 130 / F: / / ‘I 12 2.5 Fig.13 F + G KID H / / / / / l/ I’ / 12 // / 25 0.4 \ 1 1.0 Fig. 14 1.6 2.9 3.5 US. Patent 160 0a. 19, 2010 Sheet 12 0114 f 1 a —1 5/1 5/1 |— b 1; x Fig. 16 US 7,818,158 B2 162 US. Patent 0a. 19, 2010 Sheet 13 0f 14 Voltage at c 1.0 0.5 0.33 US 7,818,158 B2 US. Patent 0a. 19, 2010 Sheet 14 0114 US 7,818,158 B2 3.0 V 100 \ n’ F Ron = 5 Kohms 192 On = 10 fF out _\ in —-— Ron = 2 Kohms V OV Fig. 19 6.0 V : = 206 \ - 10 Ohms .3’ q’ - f If B-A, then 5.0 v. 200 If A, else 0.0 V then 5.0 V, else 0.0 V R=1 Kohms l 5 2.0 v E 204 / out R=1 Kohms E, 2.5 If E -I\, f;=- then 5.0V, “:5: I else V 208 / 5 R=1 K h o \ 202 1.0 V Fig. 20 US 7,818,158 B2 1 2 METHOD FOR SYMBOLIC SIMULATION OF CIRCUITS HAVING NON-DIGITAL NODE VOLTAGES Accordingly, there is a clear need for a fast, e?icient and accurate Way of symbolically simulating and verifying digital circuits that contain analog components. SUMMARY FIELD OF THE INVENTION The method of this invention is performed in a computer. In the method of this invention, the transistors Within an analog This invention pertains to methods of simulating the per formance of electrical circuits and in particular to methods of simulating circuits that contain analog circuits or devices. circuit are modeled as variable resistors. For each transistor, the program applies the gate-to-source voltage (Vgs) to a piece-Wise linear lookup table to determine the channel resis tance of the transistor. The piece-Wise linear lookup table BACKGROUND expresses the channel resistance of the transistor as a function of its Vgs, its on-resistance, its siZe and other factors speci?c Symbolic simulation is a Well-knoWn technology for the to the transistor. functional veri?cation of digital circuits. Symbolic simula Advantageously, both Vgs and the resistance of the tran tion differs from conventional simulation in that in conven tional simulation programs both the inputs and outputs are sistor are expressed as Multi-Terminal Binary Decision Dia grams (MTBDDs, also knoWn in the literature as Algebraic Decision Diagrams, or ADDs), Which are a convenient actual binary values (ls and 0s)), Whereas in symbolic simu lation programs the inputs are symbols representing both 0 20 digital inputs. Similarly, the node voltages and capacitances are Boolean expressions. Typically the clock remains binary. The circuit is veri?ed by checking the output Boolean expres sions against a reference. Some primarily digital circuits contain analog devices and hence have non-digital node voltages. The presence of analog devices in the circuit impacts the functionality being veri?ed. For example, in normal digital simulation programs the out put of the Schmitt trigger shoWn in FIG. 1 can only take on digital values, Which means that the feedback transistors 10 mechanism for expressing a plurality of non-digital (real valued) outputs as a Boolean function of a discrete number of and l (e.g., a1, a2, a3, a4, . . . b1, b2, b3, b4, etc.) and the outputs 25 in the analog circuit may generally be expressed as MTBDDs. Using a piece-Wise linear lookup table to determine the resistance of each transistor, the pull-up resistance betWeen the node and the high supply voltage and the pull-doWn resis tance betWeen the node and the loW voltage supply are com puted. After the pull-up and pull-doWn resistances have been 30 calculated, a voltage divider formula is used to compute the voltage at the node. The time at Which the voltage Will occur and 12 appear to be either on or off. If transistors 10 and 12 are at the node (i.e., the delay) is then computed, using the effec tive capacitance of the node, and the node voltage and delay siZed such that they are stronger than the other transistors in the device, then the current state of the output node Will be are entered chronologically in an event queue. After a change permanently locked. In reality, hoWever, When the input node in the inputs of the circuit, the program repeatedly returns to 35 empty, indicating that the circuit has reached a steady-state condition. The steady-state condition lasts until there is another change at the inputs. According to an aspect of the invention, circuits that have sWitches from 1 to 0 or vice-versa, the voltage at the output node Will shift slightly. This sets up a positive feedback con dition that Will end up With the output node completely shifted. This result can be accounted for, hoWever, only if the voltage at the output node is capable of taking on non-digital 40 Similarly, With the sense-ampli?er shoWn in FIG. 2, When creating voltage dividers betWeen the maximum and mini mum supply voltages. Preferably, the resistors in each voltage the enable signal goes high, the voltages at “ti” and “tf” are isolated from the voltages at “t” and “f”, respectively, setting 45 of “ti” and “tf’ being pulled up to the supply voltage and the loWer of “ti” and “tf’ being pulled doWn to ground. In a digital simulation scheme, the node values can only be 1 or 0. There fore, if tIl .5V and fIl .2V, both nodes Will be represented as logical ls. When the enable signal goes high an oscillation Moreover, the computer program of this invention is able to 50 BRIEF DESCRIPTION OF THE DRAWINGS 55 FIG. 1 is a schematic circuit diagram of a Schmitt trigger. FIG. 2 is a schematic circuit diagram of a sense-ampli?er. FIG. 3A is a How chart of a digital ASIC design How 60 is similarly a very sloW, manual effort. Use of SPICE or test benches; the siZe of test bench increases exponentially With the siZe of the circuit being analyZed. including the method of the invention. FIG. 3B illustrates a How of information during the design of a circuit using the program of this invention. FIGS. 3C and 3D illustrate a schematic diagram of the memory of the computer shoWn in FIG. 3B. FIG. 4 illustrates a How chart of the scheduling program circuit. This is very sloW, hoWever, and is applicable only to very small circuits. Model-checking on extracted ?oW-graphs fast-Spice (NanosimTM, HsimTM, etc,) requires exhaustive transistor resistances to be min-max ranges. Using the computer program of this invention makes it possible to simulate and verify digital circuits containing analog devices accurately and e?iciently. One Way of dealing With this problem is to manually replace the analog devices in the circuit With digital models results questionable. Another technique for analyZing analog devices in digital circuits involves symbolic analysis in MathematicaTM, using algebraic expressions that fully describe the behavior of the divider are small in relation to the other resistances in the circuit. handle unknoWn input values by alloWing node voltages and Will be set up that Will never resolve itself. before veri?cation. This process is time consuming and error prone, hoWever, and therefore makes the accuracy of the more that tWo voltage sources can be analyZed. To do this, the computer program identi?es the maximum and minimum voltage sources. All other voltage sources are mimicked by voltages. up a positive feedback condition that Will result in the higher analyZe the next event in the event queue until the queue is 65 Which is used to implement the symbolic event handling procedure. FIG. 5 is a schematic circuit diagram of a CMOS inverter. US 7,818,158 B2 4 3 FIG. 6 is a timing diagram of the input and output of the ucts from Synopsys, Inc. that can be used at this step include VCS, VERA, DesignWare®, Magellan, Formality, ESP and LEDA products. Synthesis and design for test (step 316): Here, the VHDL/ CMOS inverter shown in FIG. 5. FIG. 7 is a schematic circuit diagram illustrating tWo chan nel connected regions (CCRs). Verilog is translated to a netlist. The netlist can be optimiZed FIG. 8 illustrates an RC tree for one of the channel con for the target technology. Additionally, the design and imple nected regions shoWn in FIG. 7. mentation of tests to permit checking of the ?nished chip occurs. Exemplary EDA softWare products from Synopsys, Inc. that can be used at this step include Design Compiler®, FIG. 9 is a schematic circuit diagram of a data dependent loop. FIG. 10 is a schematic circuit diagram shoWing a node Physical Compiler, Test Compiler, PoWer Compiler, FPGA having pull-up and pull-doWn resistances that overlap. Compiler, Tetramax, and DesignWare® products. FIG. 11 a graph of the channel resistance of a transistor as Netlist veri?cation (step 318): At this step, the netlist is checked for compliance With timing constraints and for cor a function of Vgs. FIG. 12 is a circuit diagram illustrating the translation of capacitances across resistances to obtain the effective capaci respondence With the VHDL/Verilog source code. Exemplary EDA softWare products from Synopsys, Inc. that can be used tance at a node. at this step include Formality, ESP, PrimeTime, and VCS FIG. 13 shoWs a Boolean function represented by a multi products. terminal binary decision diagram (MTBDD). FIG. 14 illustrates the addition of tWo MTBDDs to obtain a third MTBDD. 20 Design planning (step 320): Here, an overall ?oorplan for the chip is constructed and analyZed for timing and top-level routing. Exemplary EDA softWare products from Synopsys, FIG. 15 shoWs an MTBDD that represents the resistance of Inc. that can be used at this step include Astro and IC Com the parallel combination of resistors shoWn in FIG. 16. FIG. 17 shoWs an MTBDD that represents the voltage at piler products. Physical implementation (step 322): The placement (posi tioning of circuit elements) and routing (connection of the node c in FIG. 18. FIG. 19 is a circuit diagram for illustrating hoW symbolic 25 same) occurs at this step. Exemplary EDA softWare products gate voltages are dealt With and hoW a neW value and delay at from Synopsys, Inc. that can be used at this step include the an output node are computed as a result of a change at an input Astro and IC Compiler products. Analysis and extraction (step 324): At this step, the circuit node. FIG. 20 is a circuit diagram for illustrating the analysis of a circuit that contains more than tWo voltage sources. function is veri?ed at a transistor level, this in turn permits 30 What-if re?nement. Exemplary EDA softWare products from Synopsys, Inc. that can be used at this step include AstroRail, PrimeRail, Primetime, and Star RC/XT products. Physical veri?cation (step 326): At this step various check DETAILED DESCRIPTION ing functions are performed to ensure correctness for: manu Before proceeding further With the description, it may be helpful to place this process in context. FIG. 3A shoWs a 35 simpli?ed representation of an exemplary digital ASIC design How. At a high level, the process starts With the product idea (step 300) and is realiZed in an EDA softWare design process (step 302). When the design is ?nalized, it can be taped-out (event 304). After tape out, the fabrication process can be used at this step include the Hercules product. 40 Proteus, ProteusAF, and PSMGen products. Mask data preparation (step 330): This step provides the occur resulting, ultimately, in a ?nished integrated circuit (IC) composed of a number of steps 312-330, shoWn in linear fashion for simplicity. In an actual ASIC design process, the “tape-out” data for production of masks for lithographic use 45 to produce ?nished chips. Exemplary EDA softWare products from Synopsys, Inc. that can be used at this step include the CATSI family of products. particular design might have to go back through steps until The computer program of this invention is an aspect of certain tests are passed. Similarly, in any actual design pro Netlist Veri?cation (Step 318) and is represented by step 332 cess, these steps may occur in different orders and combina in FIG. 3A. FIG. 3B illustrates the How of information in some tions. This description is therefore provided by Way of context and general explanation rather than as a speci?c, or recom mended, design How for a particular ASIC. A brief description of the components steps of the EDA softWare design process (step 302) Will noW be provided: Resolution enhancement (step 328): This step involves geometric manipulations of the layout to improve manufac turability of the design. Exemplary EDA softWare products from Synopsys, Inc. that can be used at this step include (step 306) and packaging and assembly processes (step 308) chip 310. The EDA softWare design process (step 302) is actually facturing, electrical issues, lithographic issues, and circuitry. Exemplary EDA softWare products from Synopsys, Inc. that 55 System design (step 312): The designers describe the func embodiments, Wherein a circuit design 334 is analyZed by computer 336 that has been programmed to perform acts of the type illustrated in FIG. 4 and described elseWhere herein, and any results are then revieWed by chip designer 338. Com puter 336 contains a memory 340 Chip designer 338 in turn tionality that they Want to implement, they can perform What if planning to re?ne functionality, check costs, etc. HardWare revises the circuit design, by use of a text editor or a schematic softWare architecture partitioning can occur at this stage. can be used at this step include Model Architect, Saber, Sys may be a personal computer Whereas computer 336 may be a Sun Workstation. Note that a single computer may be used instead of tWo computers. When the circuit designer 338 is tem Studio, and DesignWare® products. Logic design and functional veri?cation (step 314): At this satis?ed With the simulation results provided by computer 336, then the circuit design 334 may be taped out for fabri Exemplary EDA softWare products from Synopsys, Inc. that stage, the VHDL orVerilog code for modules in the system is Written and the design is checked for functional accuracy. entry program in a personal computer 342. Computer 342 60 More speci?cally, does the design as checked to ensure that cation into IC chip 310 in the normal manner. It Will be understood that the arroW from computer 336 to ?nished chip 310 includes all of the process steps after Netlist Veri?cation produces the correct outputs. Exemplary EDA softWare prod (step 318) in FIG. 3A. 65 US 7,818,158 B2 6 5 At step 402, the current time (curtime) is updated to the FIGS. 3C and 3D show a schematic vieW of memory 340 showing several of the data structures that are stored in memory 340 in the method of this invention. FIG. 4 illustrates a How chart for SymbolicSimulate, the time of the event, and at step 404 the current value of the node (Node.value) may be updated to the value of the event (Event.Value), Which is the voltage at the node at Which the event occurs. The value of the node is updated, hoWever, only if permitted by Mask, a Boolean function that essentially acts basic scheduling program Which is used to implement the symbolic event handling procedure. The program uses event queues, Where an event is a change in the value function for a as a ?lter that de?nes When the state of the node Will change. particular node in the circuit. Events are sorted in the event This is accomplished using an If-Then-Else (ITE) operator, queue by increasing time. Which changes Node.value to Event.Value if Mask is true. The use of the Mask function in this manner solves the prob The program shoWn in FIG. 4 can be represented in pseudo-code as folloWs: lem of scheduling data-dependent delays. At step 406, the program identi?es the nodes that Will be affected by the event. To do this, it calls a subroutine called SymbolicAffectedNodes. The subroutine SymbolicAffected SymbolicSirnulate( ) Nodes and the other subroutines referred to beloW in connec tion With basic scheduling program of FIG. 4 are described While ( <Node, Time, Event.Value, Mask> <- GetNext( ) ) cultirne <— Time further beloW. The program then cycles through the affected nodes to Node.value <- ITE(Mask, Event.Value, Node.Value) N<— SymbolicAffectedNodes(Node) Vn E N newvalue <- SymbolicComputeDC(n) change <— newvalue XOR n.value determine, for each affected node, Whether the value (DC 20 if( change == FALSE ) Tdelay<— SymbolicComputeDelay(n) voltage) at that node Will change as a result of the event and, if so, What the neW value Will be. This is represented at step 408 and is accomplished by calling a subroutine called Sym bolicComputeDC Which in turn, to alloW for the non-digital voltage values in analog devices, calls another subroutine Tdelay <- MtbddITE(change, Tdelay, [w] ) SymbolicSchedule (n, newvalue, Tdelay ) SymbolicCleanEvents( n, curtime, change’ ) SymbolicSchedule( node n, BDD value, MTBDD Tdelay ) Whild Tdelay == I°°l ) called RC. These stages of the program are represented in dInin <— MtbddMinValue(Tdelay) mask <- MtbddEqua1(Tdelay,dInin) asks Whether the value at the node has changed as a result of the event. time <- FIG. 4 by step 408 and the decision point after step 408 Which curtirne+dmin SyrnbolicCleanEvents(n,time,rnask) EnqueueEvent( <node,time,value,rnask> ) Tdelay <- MtbddITE(rnask,[w], Tdelay) If the value at the node has changed, the program calls a 30 puteDelay uses the resistance and capacitance associated With the node to compute an Elmore delay, Which represents SymbolicCleanEvents( node 11, real time, BDD mask ) for each event such that (e.Node = node) ' (e.Tirne>tirne) e.Mask <— the time at Which the neW value Will “arrive” at the node. This e.Mask ' mask’ ife.Mask = FALSE Delete e from EventQueue subroutine called SymbolicComputeDelay. SymbolicCom stage of the program is represented by step 410 in FIG. 4. 35 The neW value at the node and the delay represent a neW “event.” Based on the delay (Which is the time at Which the As the name implies, each circuit’s node state in Symbol icSimulate is represented in a symbolic form. Rather than being a binary value 1 or 0, each node value is represented by a Boolean function of the variables applied to the input ter minals of the circuit. All of the other quantities shoWn in boldface type in the code listing above are also Boolean functions. The Boolean functions are represented as Binary Decision Diagrams (BDDs) or Multi-Terminal Binary Deci sion Diagrams (MTBDDs). All BDD and MTBDD primitive operations are performed using the University of Colorado Decision Diagram Package (CUDD) version 2.2.0. See R. I. Bahar, E. A. Frohm, C. M. Gaona, G. D. Hachtel, E. Macii, A. Pardo, and F. SomenZi. Algebraic Decision Diagrams and Their Applications, ACM/IEEE International Conference on CompulerAided Design, pages 188-191, November 1993; F. SomenZi. C UDD: CU Decision Diagram PackageiRelease 2.2.0, Online User Manual, May 1998; each of Which is incorporated herein by reference in its entirety. To start the simulation, the input values to be executed are scheduled by placing them in an initial event queue. The event Will occur in relation to the present time), the neW event is placed at the proper place in the event queue. This is accomplished by calling a subroutine called SymbolicSched 40 The program then calls a subroutine called CleanEvents. CleanEvents scans through the event queue to delete all events on the speci?ed node that are scheduled to occur after 45 computed node values that Would take place after the neWly 50 event, Which is the neW DC voltage at the node, and (d) a mask. Both the value and the mask are symbolic values. steady-state value and should not be overWritten by long delay events generated using old information. CleanEvents is represented by step 414 in FIG. 4, If the value at the node does not change as a result of the event, there is no need to schedule a neW event in the queue, and steps 410 and 412 are omitted. 55 In some instances, the duration of a neW event is shorter than the delay. For example, a 10 psec glitch may appear on the gate of a transistor Whose gate capacitance produces a delay of 50 psec. In such cases, the output pulse needs to be suppressed because the input voltage Will have returned to its 60 original state before the voltage at the source or drain of the transistor can change. For this purpose, the program calls another version of CleanEvents, Which cancels all future events at a node When the neW value matches the current the next (earliest) event in the event queue. The event is represented by a tuple that includes (a) the identity of the node at Which the event takes place, (b) the time, (c) the value of the the neWly inserted event. This use of CleanEvents, immedi ately after the neW event is enqueued, overrides previously inserted event. This is necessary because the neWly-inserted event represents the latest information about the node’s simulator then executes all events in the event queue, com putes neW values for fanouts of the changed nodes, and sched ules them back into the event queue. This process is repeated until the circuit reaches a steady-state, as signaled by an empty event queue. Initially, at step 400, the program calls GetNext to obtain ule and is represented by step 412 in FIG. 4. 65 value. This use of CleanEvents is represented at step 416 in FIG. 4. After the affected node has been analyZed, it is removed from the list of affected nodes (step 418), and the program US 7,818,158 B2 7 8 proceeds to analyze the next affected node. This process continues until all of the nodes affected by the event have been analyzed. At this point, the program returns to step 400 to in betWeen the output function Will be dependent on a mix of the neW and old input variables. The Mask for the event at Time:1.1 ns Would be xAy obtain the next event in the queue. When there are no events (representing a rising transition from x:0 to y:1) and the mask for the event at Time:2.3 ns Would be xAy (representing a falling transition from x:1 to yIO), With Event.Value? in both cases. When x%/ (no change at the input), no event Would be scheduled. left in the queue, the circuit being simulated has reached a steady state and the simulation is complete until there is another change at the input terminals. To summarize, the program illustrated in FIG. 4, in response to a change at the input terminals, identi?es the SymbolicAffectedNodes affected doWnstream nodes, recomputes their steady-state Next, the program calls SymbolicAffectedNodes, Which node values, determines the delays to the affected nodes, and schedules the appropriate events. determines Which nodes Will be affected by the transition at the node at Which the event took place (step 406 in FIG. 4). The affected nodes (and, as described beloW, the node values With this overvieW of the basic program, the individual steps and subroutines Will noW be described in greater detail. and delays) are preferably computed by breaking the circuit into channel-connected regions and transforming each chan GetNext As indicated above, each event in the queue is represented nel-connected region into an RC tree. A channel-connected region (CCR) is de?ned by an array of nodes that are con nected to each other or to a voltage source only through by a tuple Which includes: (a) the identity of the node, (b) the time at Which the event Will occur, (c) the value, and (d) a mask. The “value” is the neW value (DC voltage) that Will be present at the node at the time of the event. The mask de?nes the circumstances under Which the value at the node Will change. Both the value and mask are Boolean expressions. As described above, the program initially calls GetNext to obtain a neW event (the next or earliest event in the queue) and 20 dielectric in any transistor. FIG. 7 shoWs tWo CCRs 70 and 72. The channels of transistors 700 and 702 are Within CCR 70. The channels of transistors 704, 706, 708 and 710 are Within CCR 72. A data set for each CCR is stored in the computer as 25 Event.Value, Node.Value), “Node.Value” is the current value at the node; Event.Value is the neW value at the node. If Mask is true, the value at the node is set to the neW value; otherWise, 30 400, 402 and 404 in FIG. 4. The need for the Mask function in a system Where delays are data-dependent can be illustrated by the CMOS inverter 50 shoWn in FIG. 5. Inverter 50 includes a high side PMOS transistor 500 and a loW side NMOS transistor 502. Inverter (e) the value (i.e. voltage) of the node (as explained further 35 3C. The data structure also includes a list of the transistors in each CCR, identi?ed by: (a) the nodes to Which the gate, 40 HoWever, for any given input pattern, the output Will transi 45 herein, the Word “node” and “net” are synonymous unless the context indicates otherWise.) The data structure for the list of value of the output node at any time can be represented by a 50 transistors is represented by box 356 in FIG. 3D. An RC tree for each CCR is formed by replacing each 55 grounded capacitance to each node. As described beloW, the equivalent resistance for each transistor depends on the size of the transistor, the gate-source voltage (Vgs) and some pre-computed process information (from a default process if Boolean function of the input variables, and the full symbolic conducting transistor With a resistor and connecting a Using this concept, one can construct a valid sequence of none is supplied). A corresponding RC tree for CCR 72 in FIG. 7 is shoWn in FIG. 8. The size of the capacitance that is connected to each Would be scheduled at Time:1 .1 ns and Time:2.3 ns, respec tively, and We Would obtain the series of three node functions shoWn in FIG. 6. Initially the output function is x, and even tually it settles to Since, at the output, a falling transition function of the gate-to-source voltage, (c) the Width and length of the transistor’s channel, and (d) the “type” of the transistor (i.e., Whether N-channel or P-channel). (Note: in some publications nodes are referred to as “nets.” As used from high to loW, the delay in the output Will be greater than the delay When the input goes from loW to high. Thus, the functions of the output node of unbalanced inverter 50. For example, assume that the delay at the output When the input goes from high to loW is 2.3 ns and the delay at the output When the input goes from loW to high is 1.1 ns. TWo events source and drain terminals, respectively, are connected, (b) a piece-Wise linear lookup table that is used, as described beloW, to compute the channel resistance of the transistor as a either or both of Which could represent 0 or 1, it is not obvious When the resultant event should be scheduled on the output. transition is actually a progression though a series of node functions. terminal binary decision diagram (MTBDD)), and (f) the identity of the CCR in Which the node is located. The data structure for a list of nodes is represented by box 352 in FIG. signi?cantly larger than high side transistor 500. It is apparent tion at some Well-de?ned point in time. When the input goes tains a list of the nodes (or nets) in each CCR, including for each node: (a) the name of the node, (b) the “type” of the node (i.e., Whether it is a voltage source or not), (c) the capacitance of the node, (d) a list of the transistor connections to the node, beloW, this value is expressed in Boolean form as a multi 50 is unbalanced, meaning that loW side transistor 502 is that the delay in the change of the output in response to a change in the input Will be different depending on Whether the input goes from loW to high or from high to loW. If the input sWitches from the symbolic variable x to symbolic variable y a list of the nodes that are in the CCR as Well as the maximum and minimum voltages in the CCR. This data set is repre sented by box 354 in FIG. 3D. In addition, the data structure stored in the computer con then applies the If-Then-Else (ITE) logical operator to (Mask, the oldvalue is retained. This sequence is represented by steps transistor source-drain channels, Without traversing a gate node in the RC tree is computed by summing all gate, drain 60 and source capacitances that are connected to the node, as Will occur at t:1.1 ns and a rising transition Will not occur Well as any explicit capacitances that are in the netlist. For until t:2.3 ns, the only Way that the output Will be high in the example, in FIG. 8, resistors 804, 806, 808 and 810 are replacements for transistors 704, 706, 708 and 710, respec interval betWeen 1.1 ns and 2.3 ns is if x and y are 0 and the output remains high continuously. This behavior is captured in the function xAy. In general, the output node function Will progress from being dependent only on the old input function variables to being dependent on the neW input variables, and 65 tively in FIG. 7. The capacitance 812 connected to node 802 is equal to the sum of the drain capacitances of transistors 704, 706 and 708. The capacitance 814 connected to node 816 is equal to the drain capacitance of transistor 710.