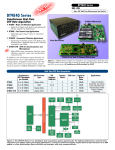

Download DT9840 Series User`s Manual

Transcript