Download GPC® 150

Transcript

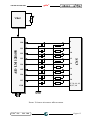

grifo® ITALIAN TECHNOLOGY + Master R Slave 1 4 + RXB 5 - + TX R + RX - VCL CN2 + TXB 1 GPC® 150 2 Slave 2 4 + RXB 5 CN2 2 + TXB 1 GPC® 150 Slave n 4 + RXB 5 CN2 2 + TXB 1 GPC® 150 FIGURA 21: ESEMPIO DI COLLEGAMENTO IN RETE IN CURRENT LOOP PASSIVO Per il collegamento in Current Loop passivo sono possibili due diversi tipi di collegamento: a 2 fili ed a 4 fili. Tali connessioni sono riportate nelle figure 19 e 20; in esse é indicata la tensione per alimentare l’anello (VCL) e le resistenze di limitazione della corrente (R). I valori di tali componenti variano in funzione del numero di dispositivi collegati e della caduta sul cavo di collegamento; bisogna quindi effettuare la scelta considerando che: - si deve garantire la circolazione di una corrente di 20 mA; - su ogni trasmettitore cadono mediamente 2,35 V con una corrente di 20 mA; - su ogni ricevitore cadono mediamente 2,52 V con una corrente di 20 mA; - in caso di cortocircuito sulla rete ogni trasmettitore dissipi al massimo 125 mW; - in caso di cortocircuito sulla rete ogni ricevitore dissipi al massimo 90 mW. Per maggiori informazioni consultare il Data-Book HEWLETT-PACKARD, nella parte che riguarda gli opto-accoppiatori per Current Loop denominati HCPL 4100 e HCPL 4200. GPC® 150 Rel. 3.00 Pagina 25