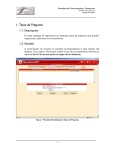

Download PCA9685

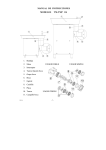

Transcript