Download RMAP User Manual - ESA Microelectronics Section

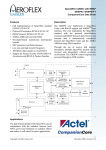

Transcript