Download HI302 - Smar

Transcript

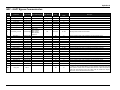

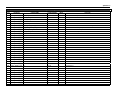

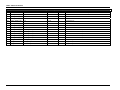

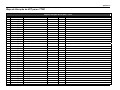

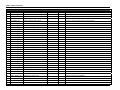

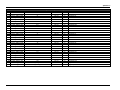

Teoria Básica de Funcionamento Conector com tampa Conector sem tampa Tampa do conector Figura 6.5 – Conector p/ programação do Firmware Para reduzir a quantidade de componentes, aumentar a confiabilidade e tornar o hardware mais flexível, foi utilizado um dispositivo lógico programável (EPLD, U10) que engloba diversas funções com lógica combinacional e seqüencial, tais como divisor de freqüência para os modems HART, decodificadores de endereços, etc. Esse componente é alimentado em 3V3 e possui entradas e saídas compatíveis com 5V. Possui uma função muito importante que é gerar o “clock” para os modems HART a partir do “clock” das UARTs. Programação do EPLD Também é possível atualizar a programação do EPLD “ in circuit”. Eventualmente isso pode ser necessário devido à melhoria contínua no desenvolvimento do equipamento. Essa atualização, entretanto, apenas é possível em fábrica. Chave de RESET manual e FACTORY INIT Na parte frontal dos HI302 encontram-se duas chaves tipo “push-button”. A do lado ESQUERDO é o RESET manual ligado ao U5, que atinge os seguintes componentes: HC11 (U1), FB3050 (U2), EPLD (U10) e UARTs (U7 e U8). A outra chave, do LADO DIREITO, provoca uma interrupção no HC11 que realiza uma inicialização na memória, retornando toda a configuração ao padrão de fábrica. Esta opção é muito útil no caso de mal funcionamento por erros de configuração, pois restaura a memória a configuração ao seu estado funcional básico. Os dados relativos à calibração não são perdidos durante o Fct Init. 6.4