Download MAN-R4300-PS - Crescent Heart Software

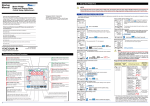

Transcript