Download Embedded Systems Architecture

Transcript

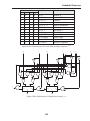

Embedded Processors Core 4K 1 Cache I MMU System Interface Unit 2 Memory Controller BIU System F unctions Real Time clock PCMCIA Interface U-bus 4K D Cache PowerPC™ 1 D MMU Parallel I/O Internal Interrupt 4 General Memory Controller Purpose Baud Rate Space Timers 16 Serial Generators DMAs; Parallel Interface 32-Bit RISC μController 2 Virtual 1DMA Port and Prog r am ROM MA Internal Timers Peripheral Bus 3 SCC1 SCC2 SCC3 SCC4 SMC1 SMC2 SPI1 Time Slot Assig ne r I2C Serial Interface Communications Processor Module Figure 4-70: MPC860 processor buses [4-15] Copyright of Freescale Semiconductor, Inc. 2004. Used by permission. In the case of the MPC860, the processor buses include the U-bus interconnecting the system interface unit (SIU), the communications processor module (CPM), and the PowerPC core. Within the CPM, there is a peripheral bus, as well. Of course, this includes the buses within the CPU. A key feature of processor buses is their width which is (the number of bits that can be transmitted at any one time). This can vary depending on both the buses implemented within the processor—for example: x86 contains bus widths of 16/32/64, 68K has 8/16/32/ 64 bit buses, MIPS 32 has 32 bit buses, and so forth—as well as the ISA register size definitions. Each bus also has a bus speed (in MHz) that impacts the performance of the processor. Buses implemented in real-world processor designs include the U, peripheral, and CPM buses in the MPC8xx family of processors, and the C and X buses in the x86 Geode. To avoid redundancy, buses are covered in more detail in Chapter 7: Board Buses, and more examples are provided there. 4.3 Processor Performance There are several measures of processor performance, but are all based upon the processor’s behavior over a given length of time. One of the most common definitions of processor performance is a processor’s throughput, the amount of work the CPU completes in a given period of time. 203

Related documents

RAS 2000 PowerRack Software Configuration Guide

Troubleshooting Async Multilink PPP Operations

User manual (Adobe pdf format)

Using Design-Level Scan to Improve Design

Hands-On Electronics: A One-Semester Course for Class Instruction

e101 - CNews.ru

- Manuals, Specs & Warranty

Set top box

LEAP USER GUIDE - Recherche : Service web

LEAP User Guide

JOPI: Java Object-Passing Interface

LEAP USER GUIDE

TABLA DE CONTENIDO - Facultad de Ingeniería

cache

IDT MIPS Microprocessor Family Software Reference Manual

ASLan++ specification and tutorial

Guida all`etichettatura e all`imballaggio a norma - ECHA

Agilent Technologies 11867A? Technical data

(CE) n. 1272/2008

Cisco 827 - 827 Router - EN Troubleshooting guide

1931 Data Entry Operator User Manual

CPU Instruction Set Details