Download Xilinx XST User Guide

Transcript

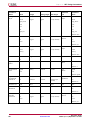

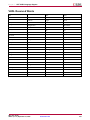

Chapter 3: XST Hardware Description Language (HDL) Coding Techniques RAMs and ROMs Related Constraints • BRAM Utilization Ratio (BRAM_UTILIZATION_RATIO) • Automatic BRAM Packing (AUTO_BRAM_PACKING) • RAM Extraction (RAM_EXTRACT) • RAM Style (RAM_STYLE) • ROM Extraction (ROM_EXTRACT) • ROM Style (ROM_STYLE) XST accepts LOC and RLOC constraints on inferred RAMs that can be implemented in a single block RAM primitive. The LOC and RLOC constraints are propagated to the NGC netlist. RAMs and ROMs Coding Examples Coding examples are accurate as of the date of publication. Download updates from ftp://ftp.xilinx.com/pub/documentation/misc/examples_v9.zip. Block RAM resources in the following devices offer different read/write synchronization modes: • Virtex®-4 • Virtex-5 • Spartan®-3 • Spartan-3E • Spartan-3A The following coding examples describe a single-port block RAM. You can deduce descriptions of dual-port block RAMs from these examples. Dual-port block RAMs can be configured with a different read/write mode on each port. Inference supports this capability. Support For Read/Write Modes summarizes support for read/write modes according to the targeted devices and how XST handles it. Support For Read/Write Modes Devices Inferred Modes Behavior Spartan-3 write-first Macro inference and generation Spartan-3E read-first Spartan-3A no-change Attach adequate WRITE_MODE, WRITE_MODE_A, WRITE_MODE_B constraints to generated block RAMs in NCF none RAM inference completely disabled Virtex-4 Virtex-5 CPLD Single-Port RAM in Read-First Mode Diagram XST User Guide UG627 (v 11.3) September 16, 2009 www.xilinx.com 129

Related documents