Download QuickWorks® Tutorial User Manual (Release 2008.2.1)

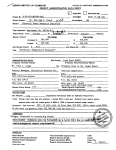

Transcript