Download MPC5121e Hardware Design Guide

Transcript

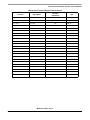

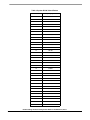

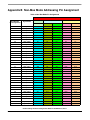

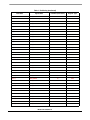

DRAM Controller Initialization NOTE Because the specifications in JESD79E, JEDEC Standard: Double Data Rate (DDR) SDRAM Specification, JESD79-2E, JEDEC Standard: DDR2 SDRAM Specification, and JESD209, JEDEC Standard: Low Power Double Data Rate (LPDDR) SDRAM Specification define different numbers of DRAM bank, row, and column address lines, the number of address lines have to be taken into account during the mapping of the addresses. The bit 16BITMODE controls the column address. In 32-bit mode (16BITMODE is cleared) the DRAM controller is controlling the column address line 0 internally. The other address lines will be mapped to the internal address lines. The table below shows the mapping of the column address lines to the internal address lines, depending on the number of the used column address lines in 32-bit mode. Table 3. Mapping of DDR SDRAM Column Address Lines to the MPC5121e Internal Address Lines in 32-Bit Mode Column Address (CA) Lines Mapped Column Address (CA) Lines Used Internal Address (IA) Lines CA0 CA7 CA1 CA7 IA3 IA9 CA0 CA8 CA1 CA8 IA3 IA10 CA0 CA9 CA1 CA9 IA3 IA11 CA0 CA11 CA1 CA11 IA3 IA13 CA0 CA12 CA1 CA12 IA3 IA14 In 16-bit mode (16BITMODE is set), the DRAM controller is controlling the column address lines 0 and 1 internally. The other address lines will be mapped to the internal address lines. Table 4 shows the mapping of the column address lines to the internal address lines depending on the number of the column address lines used in 16-bit mode. Table 4. Mapping of DDR SDRAM Column Address Lines to the MPC5121e Internal Address Lines in 16-Bit Mode 1 Column Address (CA) Lines Mapped Column Address (CA) Lines Used Internal Address (IA) Lines CA0 CA7 CA2 CA7 IA3 IA81 CA0 CA8 CA2 CA8 IA3 IA9 CA0 CA9 CA2 CA9 IA3 IA10 CA0 CA11 CA2 CA11 IA3 IA12 CA0 CA12 CA2 CA12 IA3 IA13 Not supported. The bit field DRAM_ROW_SELECT controls the row address mapping. The table 14-7 in chapter 14.2.2.1 “DDR System Configuration Register” in MPC5121ERM, MPC5121e Reference Manual Rev. 3, shows all possible address mappings from internal to DDR SDRAM row addresses. MPC5121e DRAM Controller, Rev. 2 68 Freescale Semiconductor