Download - Emulation Technology Inc.

Transcript

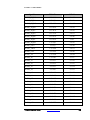

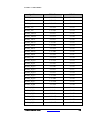

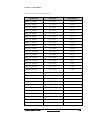

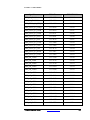

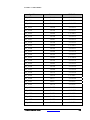

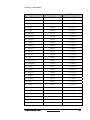

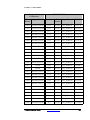

B O A R D H A R D W A R E two controllers to access the same SSRAM, using two activation signals, ADSC# and ADSP#; an activation with ADSP# requires data and byte enables one clock cycle after the address and activation. Syncburst Pipelined (Figure 49) is identical except for registered outputs, which delay read data an additional clock cycle but may be necessary for high speed designs. Figure 48 - SSRAM Flow-trough Figure 49 - SSRAM Pipeline Zero-Bus-Turnaround (ZBT) SSRAM’s are designed to eliminate wait states between reads and writes by synchronizing data. Figure 50 accept and return data one clock cycle after the address phase, and ZBT Pipeline SSRAMs (Figure 51) accept and return data two clock cycles after the address phase. This allows the user to begin a write burst ET6000K10S User Guide www.emulation.com 99