Download - Emulation Technology Inc.

Transcript

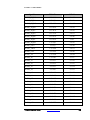

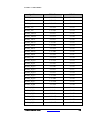

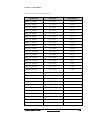

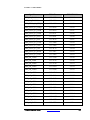

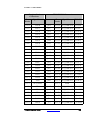

B O A R D H A R D W A R E operates at twice the clock frequency, while address and control operate at the base clock frequency. In other words, the data is written or read from the part on every clock transition, or twice per clock cycle. This effectively doubles the throughput of the memory device. The trade-off for such an improvement in throughput is increased complexity in interface logic to the DDR memory, as well as increased complexity in routing the DDR signals on the printed circuit board. Additionally, this memory has the same latencies as standard SDRAM, so that while the data transfers are twice as fast, the latencies associated with DDR SDRAM are on par with standard SDRAM. 6.3.1 Basics of DDR Operation DDR SDRAM provides data capture at a rate of twice the clock frequency. Therefore, DDR SDRAM with a clock frequency of 100 MHz has a peak data transfer rate of 200 MHz or 6.4 Gigabits per second for a 16-bit interface. In order to maintain high-speed signal integrity and stringent timing goals, a bi-directional data strobe is used in conjunction with SSTL_2 signaling standard as well as differential clocks. DDR SDRAM operates as a source-synchronous system, in which data is captured twice per clock cycle, using a bi-directional data strobe to clock the data. The DDR SDRAM control bus consists of a clock enable, chip select, row and column addresses, bank address, and a write enable. Commands are entered on the positive edges of the clock, and data occurs for both positive and negative edges of the clock. The double data rate memory utilizes a differential pair for the system clock and, therefore, has both a true clock (CK) and complementary clock (CK#) signal. 6.3.2 DDR SDRAM Configuration The DDR SDRAM memory components on the ET6000K10S are arranged as a 16bit mode (refer to Figure 54). Made up of four discrete parts (U20, U21, U22, U23), the components used are 64-Mb x 16 parts, organized as 16 million deep by 16-bits wide and 4 banks. This provides for a total capacity of 128-Mbytes for the system (for more information, refer to Micron’s datasheet PN MT46V64M16). ET6000K10S User Guide www.emulation.com 112