Download VR4181 specs - Delorie Software

Transcript

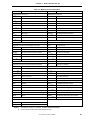

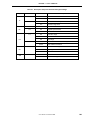

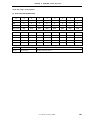

CHAPTER 27 MIPS III INSTRUCTION SET DETAILS SLLV SLLV Shift Left Logical Variable 31 26 25 21 20 16 15 11 10 6 5 0 SPECIAL 000000 rs rt rd 0 00000 SLLV 000100 6 5 5 5 5 6 Format: SLLV rd, rt, rs Description: The contents of general register rt are shifted left the number of bits specified by the low-order five bits contained in general register rs, inserting zeros into the low-order bits. The result is placed in register rd. In 64-bit mode, the 32-bit result is sign-extended when placed in the destination register. It is sign extended for all shift amounts, including zero; SLLV with zero shift amount truncates a 64-bit value to 32 bits and then sign extends this 32-bit value. SLLV, unlike nearly all other word operations, does not require an operand to be a properly sign-extended word value to produce a valid sign-extended word result. Operation: 32 T: s ← GPR [rs] 4…0 GPR [rd] ← GPR [rt] (31 – s)…0 || 0 64 T: s s ← 0 || GPR [rs] 4…0 temp ← GPR [rt] (31 – s)…0) || 0 s GPR [rd] ← (temp31) || temp 32 Exceptions: None Remark SLLV with a shift amount of zero may be treated as a NOP by some assemblers, at some optimization levels. If using SLLV with a zero shift to truncate 64-bit values, check the assembler you are using. User’s Manual U14272EJ1V0UM00 669

Related documents

manual de usuario del simulador de instrucciones mips r-4000

VR4181™

cache

ST-Realizer-II user manual (for ST62 & ST7 8-bit MCUs)

Using PDtrace™ with SDE and System Navigator™ for MIPS® Cores

Errata Sheet

Errata Sheet

Errata for MIPS R4000/R4400 Microprocessor User`s Manual

YAMON™ User`s Manual

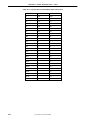

CPU Instruction Set Details

IDT MIPS Microprocessor Family Software Reference Manual

VR Series 64-/32-Bit Microprocessor Programming Guide AN