Download VR4181 specs - Delorie Software

Transcript

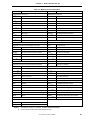

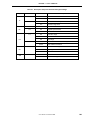

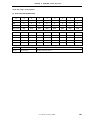

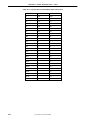

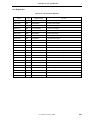

CHAPTER 27 MIPS III INSTRUCTION SET DETAILS LDR LDR Load Doubleword Right (Continued) Given a doubleword in a register and a doubleword in memory, the operation of LDR is as follows: LDR Register A B C D E F G H Memory I J K L M N O P vAddr 2..0 BigEndianCPU = 0 destination type offset (LEM) 0 I J K LMNOP 7 0 1 A I J K LMNO 6 1 2 A B I J K LMN 5 2 3 A BC I J K LM 4 3 4 A BCD I J K L 3 4 5 A BCDE I J K 2 5 6 A BCDE F I J 1 6 7 A BCDE FG I 0 7 LEM Little-endian memory (BigEndianMem = 0) Type AccessType (see Figure 3-2) sent to memory Offset pAddr2..0 sent to memory Exceptions: TLB refill exception TLB invalid exception Bus error exception Address error exception Reserved instruction exception (VR4181 in 32-bit user mode, VR4181 in 32-bit supervisor mode) User’s Manual U14272EJ1V0UM00 635

Related documents

manual de usuario del simulador de instrucciones mips r-4000

VR4181™

cache

ST-Realizer-II user manual (for ST62 & ST7 8-bit MCUs)

Using PDtrace™ with SDE and System Navigator™ for MIPS® Cores

Errata Sheet

Errata Sheet

Errata for MIPS R4000/R4400 Microprocessor User`s Manual

YAMON™ User`s Manual

CPU Instruction Set Details

IDT MIPS Microprocessor Family Software Reference Manual

VR Series 64-/32-Bit Microprocessor Programming Guide AN

Preliminary User`s Manual

SERVICE MANUAL COOKING

MIPSproTM Assembly Language Programmer`s Guide

μMPS2 Principles of Operation

Using SYS/BIOS with Stellaris® ARM® Cortex

The IDT79R3071™, IDT 79R3081™ RISController™ Hardware

Toshiba TX39 Computer Hardware User Manual

ATOM 1024 User Manual