Download i960 Jx Microprocessor Developer`s Manual

Transcript

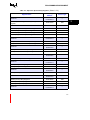

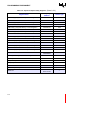

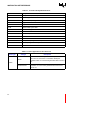

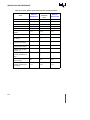

12.6 SYSTEM REQUIREMENTS...................................................................................... 12.6.1 Input Clock (CLKIN) ............................................................................................ 12.6.2 Power and Ground Requirements (VCC, VSS) ..................................................... 12.6.3 VCC5 Pin Requirements ....................................................................................... 12.6.4 Power and Ground Planes .................................................................................. 12.6.5 Decoupling Capacitors ........................................................................................ 12.6.6 I/O Pin Characteristics ......................................................................................... 12.6.6.1 Output Pins .................................................................................................. 12.6.6.2 Input Pins ..................................................................................................... 12.6.7 High Frequency Design Considerations .............................................................. 12.6.8 Line Termination .................................................................................................. 12.6.9 Latchup ................................................................................................................ 12.6.10 Interference ......................................................................................................... 12-34 12-34 12-34 12-35 12-35 12-36 12-36 12-37 12-37 12-38 12-38 12-39 12-40 CHAPTER 13 MEMORY CONFIGURATION 13.1 Memory Attributes ....................................................................................................... 13-1 13.1.1 Physical Memory Attributes ................................................................................... 13-1 13.1.2 Logical Memory Attributes ..................................................................................... 13-2 13.2 Differences With Previous i960 Processors ................................................................ 13-3 13.3 Programming the Physical Memory Attributes (PMCON Registers) ........................... 13-4 13.3.1 Bus Width .............................................................................................................. 13-5 13.4 Physical Memory Attributes at Initialization ................................................................. 13-5 13.4.1 Bus Control (BCON) Register ................................................................................ 13-6 13.5 Boundary Conditions for Physical Memory Regions ................................................... 13-7 13.5.1 Internal Memory Locations .................................................................................... 13-7 13.5.2 Bus Transactions Across Region Boundaries ....................................................... 13-7 13.5.3 Modifying the PMCON Registers ........................................................................... 13-7 13.6 Programming the Logical Memory Attributes .............................................................. 13-8 13.6.1 Defining the Effective Range of a Logical Data Template ................................... 13-11 13.6.2 Selecting the Byte Order ..................................................................................... 13-12 13.6.3 Data Caching Enable .......................................................................................... 13-12 13.6.4 Enabling the Logical Memory Template .............................................................. 13-12 13.6.5 Initialization .......................................................................................................... 13-13 13.6.6 Boundary Conditions for Logical Memory Templates .......................................... 13-13 13.6.6.1 Internal Memory Locations ........................................................................... 13-13 13.6.6.2 Overlapping Logical Data Template Ranges ............................................... 13-13 13.6.6.3 Accesses Across LMT Boundaries .............................................................. 13-14 13.6.7 Modifying the LMT Registers ............................................................................... 13-14 13.6.8 Dynamic Byte Order Changing ............................................................................ 13-14 CHAPTER 14 EXTERNAL BUS 14.1 OVERVIEW ................................................................................................................. 14-1 xiii