Download i960 Jx Microprocessor Developer`s Manual

Transcript

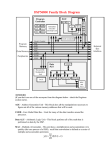

INTERRUPTS Figure 11-7 shows how a signal is sampled in each mode. The debounce-sampling option adds several clock cycles to an interrupt’s latency due to the multiple clocks of sampling. Inputs are sampled once every CLKIN cycle (external bus clock). Interrupt pins are asynchronous inputs. Setup or hold times relative to CLKIN are not needed to ensure proper pin detection. Note in Figure 11-7 that interrupt inputs are sampled once every two CLKIN cycles. For practical purposes, this means that asynchronous interrupting devices must generate an interrupt signal that is asserted for at least three CLKIN cycles for the fast sampling mode or seven CLKIN cycles for the debounce sampling mode. See section 1.4, “Related Documents” (pg. 1-10). These documents have setup and hold specifications that guarantee detection of the interrupt on particular edges of CLKIN. These specification are useful in designs that use synchronous logic to generate interrupt signals to the processor. These specification must also be used to calculate the minimum signal width, as shown in Figure 11-7. * * * * * * * CLKIN XINT[7:0] (fast sampled) XINT[7:0] (debounce) 2 cycle min. Detect Interrupt 4 cycle min. Detect Interrupt * Denotes sampling clock edge. Interrupt pins are sampled every CLKIN (external bus clock) cycle. Figure 11-7. Interrupt Sampling 11-20 * *

Related documents

i960 CA/CF Microprocessor User`s Manual

USP 507 Universal Signal Processor User's Manual

DABmotion DAB1002 Instructions

80960Jx Processor

2016 Nissan LEAF | Navigation System Owner`s Manual | Nissan USA

User's Guide

i960 Microprocessor User`s Guide for Cyclone and PCI

i960® Processor Compiler User`s Manual

Embedded Programming with C++

Acronyms

Old Customer Relationship Agreement

LSI MegaRAID SCSI 320-1 RAID Controller Series 520 User's Manual

Chevrolet 2015 Impala Get To Know Manual

Annotator User`s Manual - Preliminary

qui - HP

TESEQ Modula - PH