Download i960 Jx Microprocessor Developer`s Manual

Transcript

TEST FEATURES If TMS is high on the rising edge of TCK, the controller enters the Exit1-DR. If TMS is low on the rising edge of TCK, the controller enters the Shift-DR state. 15.3.5.5 Shift-DR State In this controller state, the test data register, which is connected between TDI and TDO as a result of the current instruction, shifts data one bit position nearer to its serial output on each rising edge of TCK. Test data registers that the current instruction selects but does not place in the serial path, retain their previous value during this state. The instruction does not change while the TAP controller is in this state. If TMS is high on the rising edge of TCK, the controller enters the Exit1-DR state. If TMS is low on the rising edge of TCK, the controller remains in the Shift-DR state. 15.3.5.6 Exit1-DR State This is a temporary controller state. When the TAP controller is in the Exit1-DR state and TMS is held high on the rising edge of TCK, the controller enters the Update-DR state, which terminates the scanning process. If TMS is held low on the rising edge of TCK, the controller enters the Pause-DR state. The instruction does not change while the TAP controller is in this state. All test data registers selected by the current instruction retain their previous value during this state. 15.3.5.7 Pause-DR State The Pause-DR state allows the test controller to temporarily halt the shifting of data through the test data register in the serial path between TDI and TDO. The test data register selected by the current instruction retains its previous value during this state. The instruction does not change in this state. The controller remains in this state as long as TMS is low. When TMS goes high on the rising edge of TCK, the controller moves to the Exit2-DR state. 15.3.5.8 Exit2-DR State This is a temporary state. If TMS is held high on the rising edge of TCK, the controller enters the Update-DR state, which terminates the scanning process. If TMS is held low on the rising edge of TCK, the controller enters the Shift-DR state. The instruction does not change while the TAP controller is in this state. All test data registers selected by the current instruction retain their previous value during this state. 15-11 15

Related documents

i960 CA/CF Microprocessor User`s Manual

USP 507 Universal Signal Processor User's Manual

DABmotion DAB1002 Instructions

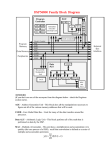

80960Jx Processor

2016 Nissan LEAF | Navigation System Owner`s Manual | Nissan USA

User's Guide

i960 Microprocessor User`s Guide for Cyclone and PCI

i960® Processor Compiler User`s Manual

Embedded Programming with C++

Acronyms

Old Customer Relationship Agreement

LSI MegaRAID SCSI 320-1 RAID Controller Series 520 User's Manual

Chevrolet 2015 Impala Get To Know Manual

Annotator User`s Manual - Preliminary

qui - HP

TESEQ Modula - PH