Download Intel Xeon D-1540

Transcript

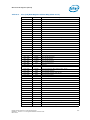

High Precision Event Timer Registers 14.1.4 MAIN_CNT—Main Counter Value Register Address Offset: Default Value: 0F0h N/A Attribute: Size: R/W 64 bits . Bit 63:0 14.1.5 Description Counter Value (COUNTER_VAL[63:0]) — R/W. Reads return the current value of the counter. Writes load the new value to the counter. Notes: 1. Writes to this register should only be done while the counter is halted. 2. Reads to this register return the current value of the main counter. 3. 32-bit counters will always return 0 for the upper 32-bits of this register. 4. If 32-bit software attempts to read a 64-bit counter, it should first halt the counter. Since this delays the interrupts for all of the timers, this should be done only if the consequences are understood. It is strongly recommended that 32-bit software only operate the timer in 32-bit mode. 5. Reads to this register are monotonic. No two consecutive reads return the same value. The second of two reads always returns a larger value (unless the timer has rolled over to 0). TIMn_CONF—Timer n Configuration and Capabilities Register Address Offset: Default Value: Note: Timer Timer Timer Timer Timer Timer Timer Timer N/A 0: 1: 2: 3: 4: 5: 6: 7: 100–107h, 120–127h, 140–147h, 160–167h, 180–187h, 1A0–1A7h, 1C0–1C7h, 1E0–1E7h, RO, R/W Size: 64 bit The letter n can be 0, 1, 2, 3, 4, 5, 6, or 7 referring to Timer 0, 1, 2, 3, 4, 5, 6, or 7. Bit 514 Attribute: Description 63:56 Reserved. These bits will return 0 when read. 55:52, 44,43 Timer Interrupt Rout Capability (TIMERn_INT_ROUT_CAP) — RO. Timer 0, 1:Bits 52, 53, 54, and 55 in this field (corresponding to IRQ 20, 21, 22, and 23) have a value of 1. Writes will have no effect. Timer 2:Bits 43, 52, 53, 54, and 55 in this field (corresponding to IRQ 11, 20, 21, 22, and 23) have a value of 1. Writes will have no effect. Timer 3:Bits 44, 52, 53, 54, and 55 in this field (corresponding to IRQ 11, 20, 21, 22, and 23) have a value of 1. Writes will have no effect. Timer 4, 5, 6, 7:This field is always 0 as interrupts from these timers can only be delivered using direct processor interrupt messages. Note: If IRQ 11 is used for HPET #2, software should ensure IRQ 11 is not shared with any other devices to ensure the proper operation of HPET #2. Note: If IRQ 12 is used for HPET #3, software should ensure IRQ 12 is not shared with any other devices to ensure the proper operation of HPET #3. 51:45, 42:16 Reserved. These bits return 0 when read. 15 Timer n Processor Message Interrupt Delivery (Tn_PROCMSG_INT_DEL_CAP) — RO. This bit is always read as ‘1’, since Intel® Xeon® Processor D-1500 Product Family HPET implementation supports the direct processor interrupt delivery. 14 Timer n Processor Message Interrupt Enable (Tn_PROCMSG_EN_CNF) — R/W / RO. If the Tn_PROCMSG_INT_DEL_CAP bit is set for this timer, then the software can set the Tn_PROCMSG_EN_CNF bit to force the interrupts to be delivered directly as processor messages, rather than using the 8259 or I/O (x) APIC. In this case, the Tn_INT_ROUT_CNF field in this register will be ignored. The Tn_PROCMSG_ROUT register will be used instead. Timer 0, 1, 2, 3 Specific: This bit is a read/write bit. Timer 4, 5, 6, 7 Specific: This bit is always Read Only ‘1’ as interrupt from these timers can only be delivered using direct processor interrupt messages. Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 1 of 4: Integrated Platform Controller Hub March 2015

Related documents

CT-CCVAX Intel Atom D2000/N2000 COM

Intel Atom E620

User Guide

Development Kits User Guide: 4th Generation Intel® Core

Intel Xeon Wolfdale E3210

Evido EAD-D2000 User`s manual

Intel Pentium G6951

Carrier Access CMG Router User manual

Black Box Compact T1 MT850A User manual

Microsoft SP5100/S Specifications