Download Intel Xeon D-1540

Transcript

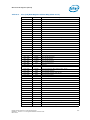

SATA Controller Registers (D31:F2) 8.1.6.3 When Sub Class Code Register (D31:F2:Offset 0Ah) = 06h Address Offset: Default Value: 09h 01h Attribute: Size: Bit 7:0 8.1.7 Description Interface (IF) — RO. Indicates that the SATA Controller is an AHCI HBA that has a major revision of 1. SCC—Sub Class Code Register (SATA–D31:F2) Address Offset: Default Value: 0Ah See bit description Bit 7:0 SCC Register Value 00b 01h (IDE Controller) 01b 06h (AHCI Controller) 10b 04h (RAID Controller) BCC—Base Class Code Register (SATA–D31:F2SATA– D31:F2) 0Bh 01h Bit 7:0 Attribute: Size: RO 8 bits Description Base Class Code (BCC) — RO. 01h = Mass storage device PMLT—Primary Master Latency Timer Register (SATA– D31:F2) Address Offset: Default Value: 0Dh 00h Bit 7:0 8.1.10 RO 8 bits Sub Class Code (SCC) This field specifies the sub-class code of the controller, per the table below: Address Offset: Default Value: 8.1.9 Attribute: Size: Description MAP.SMS (D31:F2:Offset 90h:bit 7:6) Value 8.1.8 RO 8 bits Attribute: Size: RO 8 bits Description Master Latency Timer Count (MLTC) — RO. 00h = Hardwired. The SATA controller is implemented internally, and is not arbitrated as a PCI device, so it does not need a Master Latency Timer. HTYPE—Header Type Register (SATA–D31:F2) Address Offset: Default Value: 0Eh 00h Bit 7 6:0 Attribute: Size: RO 8 bits Description Multi-function Device (MFD) — RO. Indicates this SATA controller is not part of a multifunction device. Header Layout (HL) — RO. Indicates that the SATA controller uses a target device layout. Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 1 of 4: Integrated Platform Controller Hub March 2015 327

Related documents

CT-CCVAX Intel Atom D2000/N2000 COM

Intel Atom E620

User Guide

Development Kits User Guide: 4th Generation Intel® Core

Intel Xeon Wolfdale E3210

Evido EAD-D2000 User`s manual

Intel Pentium G6951

Carrier Access CMG Router User manual

Black Box Compact T1 MT850A User manual

Microsoft SP5100/S Specifications