Download Intel Xeon D-1540

Transcript

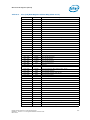

PCI Express* Configuration Registers 13.1.4 Bit Description 2 Bus Master Enable (BME) — R/W. 0 = Disable. Memory and I/O requests received at a Root Port must be handled as Unsupported Requests. 1 = Enable. Allows the root port to forward Memory and I/O Read/Write cycles onto the backbone from a PCI Express* device. Note: This bit does not affect forwarding of completions in either upstream or downstream direction nor controls forwarding of requests other than memory or I/O 1 Memory Space Enable (MSE) — R/W. 0 = Disable. Memory cycles within the range specified by the memory base and limit registers are master aborted on the backbone. 1 = Enable. Allows memory cycles within the range specified by the memory base and limit registers can be forwarded to the PCI Express device. 0 I/O Space Enable (IOSE) — R/W. This bit controls access to the I/O space registers. 0 = Disable. I/O cycles within the range specified by the I/O base and limit registers are master aborted on the backbone. 1 = Enable. Allows I/O cycles within the range specified by the I/O base and limit registers can be forwarded to the PCI Express device. PCISTS—PCI Status Register (PCI Express*—D28:F0/F1/ F2/F3/F4/F5/F6/F7) Address Offset: Default Value: Attribute: Size: R/WC, RO 16 bits Bit Description 15 Detected Parity Error (DPE) — R/WC. 0 = No parity error detected. 1 = Set when the root port receives a command or data from the backbone with a parity error. This is set even if PCIMD.PER (D28:F0/F1/F2/F3:04, bit 6) is not set. 14 Signaled System Error (SSE) — R/WC. 0 = No system error signaled. 1 = Set when the root port signals a system error to the internal SERR# logic. 13 Received Master Abort (RMA) — R/WC. 0 = Root port has not received a completion with unsupported request status from the backbone. 1 = Set when the root port receives a completion with unsupported request status from the backbone. 12 Received Target Abort (RTA) — R/WC. 0 = Root port has not received a completion with completer abort from the backbone. 1 = Set when the root port receives a completion with completer abort from the backbone. 11 Signaled Target Abort (STA) — R/WC. 0 = No target abort received. 1 = Set whenever the root port forwards a target abort received from the downstream device onto the backbone. 10:9 DEVSEL# Timing Status (DEV_STS) — Reserved per the PCI Express* Base Specification. 8 Master Data Parity Error Detected (DPED) — R/WC. 0 = No data parity error received. 1 = Set when the root port receives a completion with a data parity error on the backbone and PCIMD.PER (D28:F0/F1/F2/F3:04, bit 6) is set. 7 Fast Back to Back Capable (FB2BC) — Reserved per the PCI Express* Base Specification. 6 Reserved 5 66 MHz Capable — Reserved per the PCI Express* Base Specification. 4 Capabilities List — RO. Hardwired to 1. Indicates the presence of a capabilities list. 3 Interrupt Status — RO. Indicates status of Hot-Plug and power management interrupts on the root port that result in INTx# message generation. 0 = Interrupt is de-asserted. 1 = Interrupt is asserted. This bit is not set if MSI is enabled. If MSI is not enabled, this bit is set regardless of the state of PCICMD.Interrupt Disable bit (D28:F0/F1/F2/F3/F4/F5/F6/F7/F6/F7:04h:bit 10). 2:0 482 06h–07h 0010h Reserved Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 1 of 4: Integrated Platform Controller Hub March 2015

Related documents

CT-CCVAX Intel Atom D2000/N2000 COM

Intel Atom E620

User Guide

Development Kits User Guide: 4th Generation Intel® Core

Intel Xeon Wolfdale E3210

Evido EAD-D2000 User`s manual

Intel Pentium G6951

Carrier Access CMG Router User manual

Black Box Compact T1 MT850A User manual

Microsoft SP5100/S Specifications